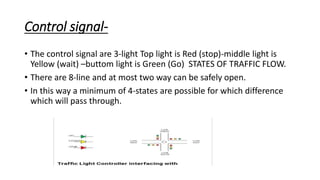

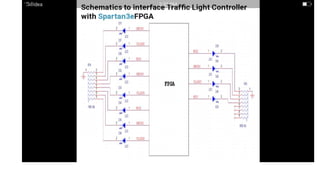

This document summarizes a student project to design an FPGA-based traffic light controller system using VHDL to reduce waiting times for drivers during peak hours. The system uses sensors to detect vehicle presence and automatically adjust light timings. It was tested through simulation and implemented on an Altera FLEX 10K FPGA chip. The design addresses a complex six-way intersection with varying light cycle times for main roads and side roads. Simulation results showed it effectively reduces driver wait times during designated morning, afternoon and evening peak periods.