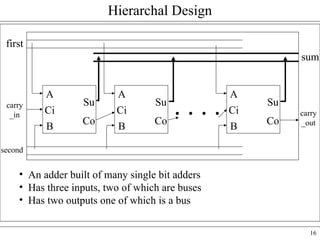

The document covers structural modeling in Verilog, emphasizing its advantages over dataflow modeling and outlining the essential components like primitives, delays, and synthesis directives. Key topics include the importance of hand-designed systems, the use of hierarchical designs for adders, and component instantiation methods. It concludes by highlighting how structural modeling serves as a foundational approach for designing efficient digital systems using Verilog.

![23

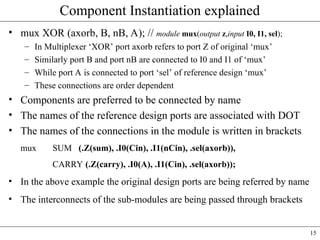

Code for hierarchal design

1. module adder_bit_n #(parameter n = 8)

2. (output [n-1:0] sum,

3. output carry_out,

4. input [n-1:0] first, second,

5. input carry_in);

6. genvar j;

7. wire [n:0] carry_wires;

8. assign carry_wires[0] = carry_in;

9. generate

10. for(j=0; j <n; j = j+1)

11. begin :series

12. adder

A(.A(first[j]), .Ci(carry_wires[j]), .B(second[j]), .Su(sum[j]), .Co(carry_wires[j+1]));

13. end

14. endgenerate

15. assign carry_out = carry_wires[n];

16. endmodule](https://image.slidesharecdn.com/structuralmodelling-250109164529-488c15c8/85/Structural_Modelling-Design-DetailsExplaination-23-320.jpg)

![24

Vectors

• Signals which are multi-bits are declared as vectors

• Can be declared as [high:low] or [low:high]

• The left hand value always specifies the index of the MSB

• A bit of the vector is accessible

• Example

– see previous example

• wire [n:0] carry_wires // line 7 – vector being declared

• carry_wires[0] =carry_in // line 8 – Bit of vector is assigned

• carry_out = carry_wires[n] // line 15 – Bit of vector is accessed

• carry_wires[5:2] = 4’d1010 // part of vector being assigned value

• outp = carry_wires[n-1:n-5] // part of vector being accessed](https://image.slidesharecdn.com/structuralmodelling-250109164529-488c15c8/85/Structural_Modelling-Design-DetailsExplaination-24-320.jpg)