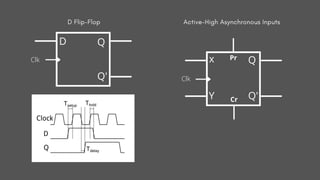

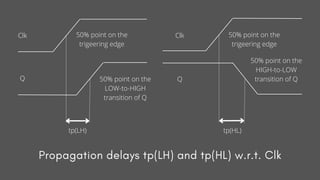

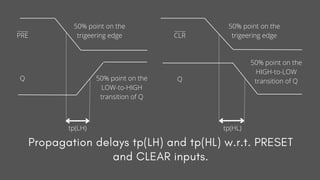

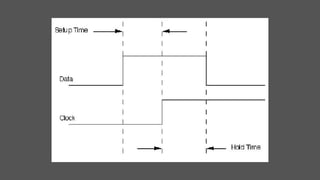

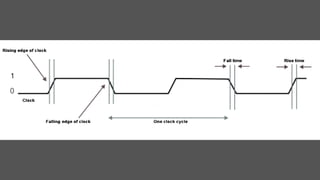

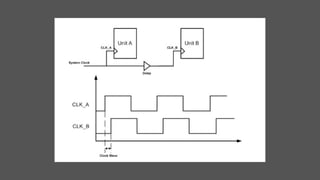

The document discusses the operational characteristics of flip-flops, including propagation delay, set-up time, hold time, maximum clock frequency, clock skew, and time race in latches and flip-flops, which are essential components in synchronous digital systems. It differentiates between level triggering and edge triggering mechanisms and elaborates on synchronous versus asynchronous inputs affecting flip-flop outputs. The document also addresses clock skew and time race phenomena that can impact the timing and reliability of sequential circuits.