This document provides an overview of an introductory lecture on embedded systems and ARM processors. It discusses the ARM instruction set, versions of ARM including ARM7, and ARM's design philosophy which emphasizes portability, limited memory, and price sensitivity for embedded applications. The goal is high code density and total effective system performance while minimizing power consumption.

![2

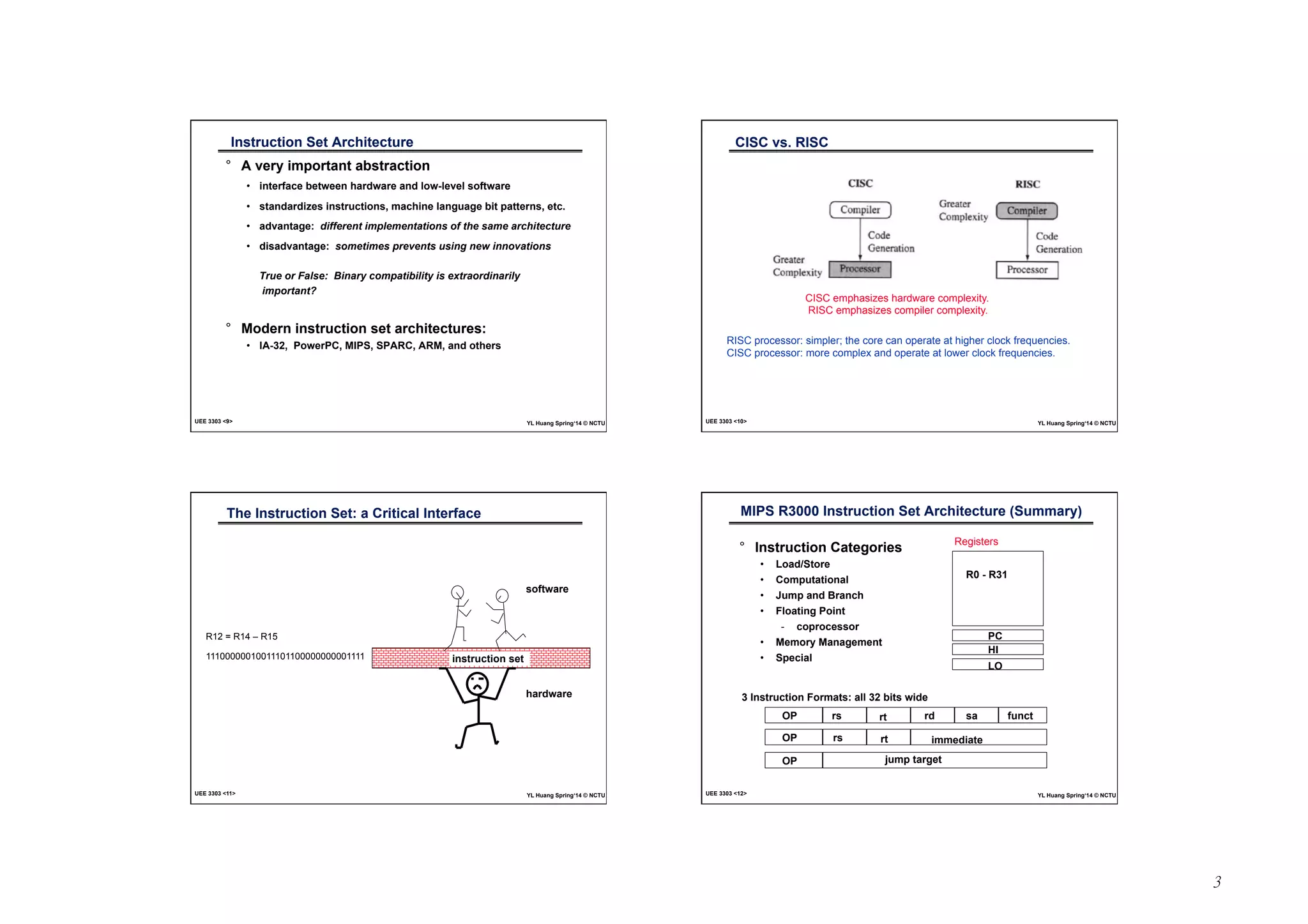

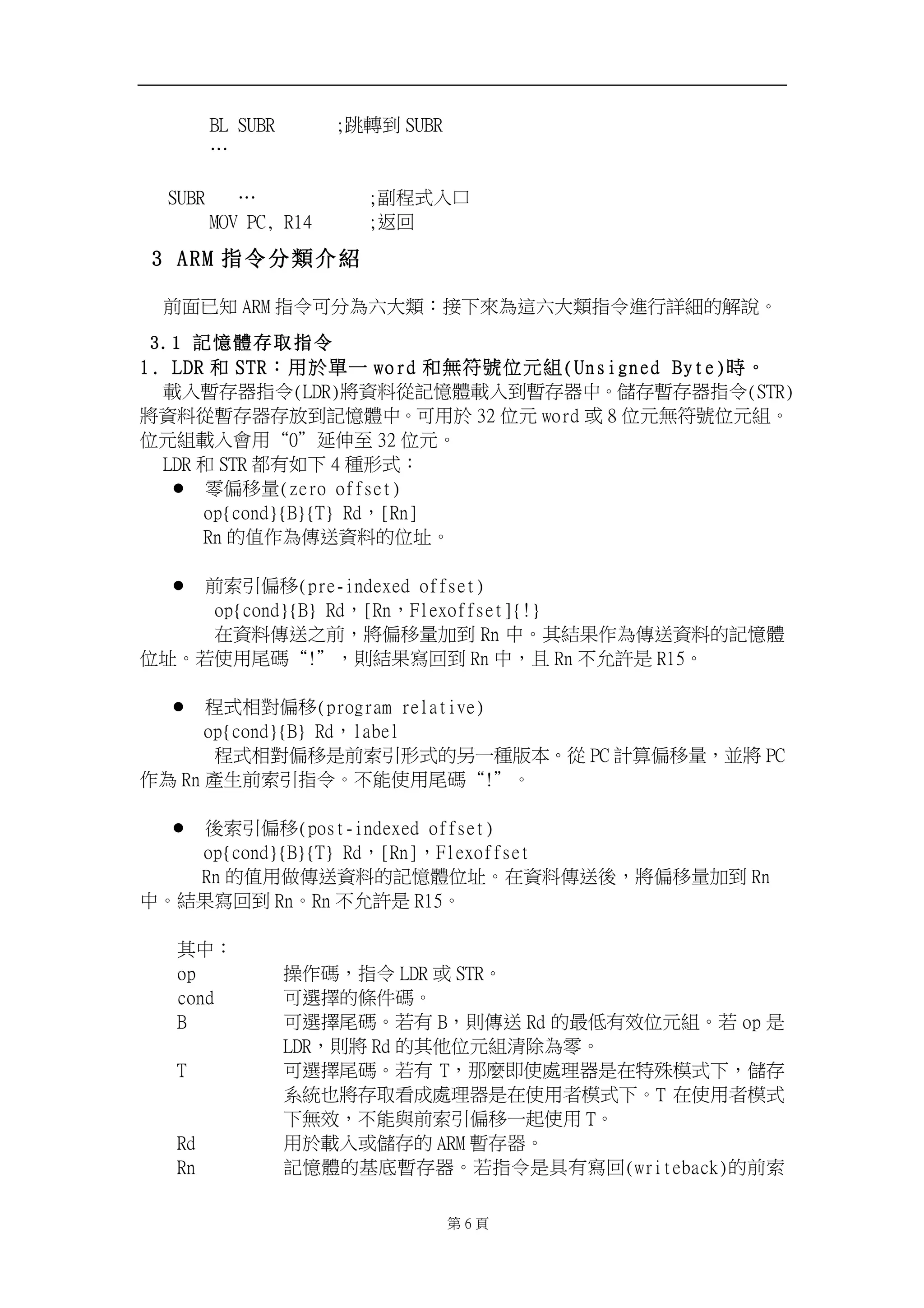

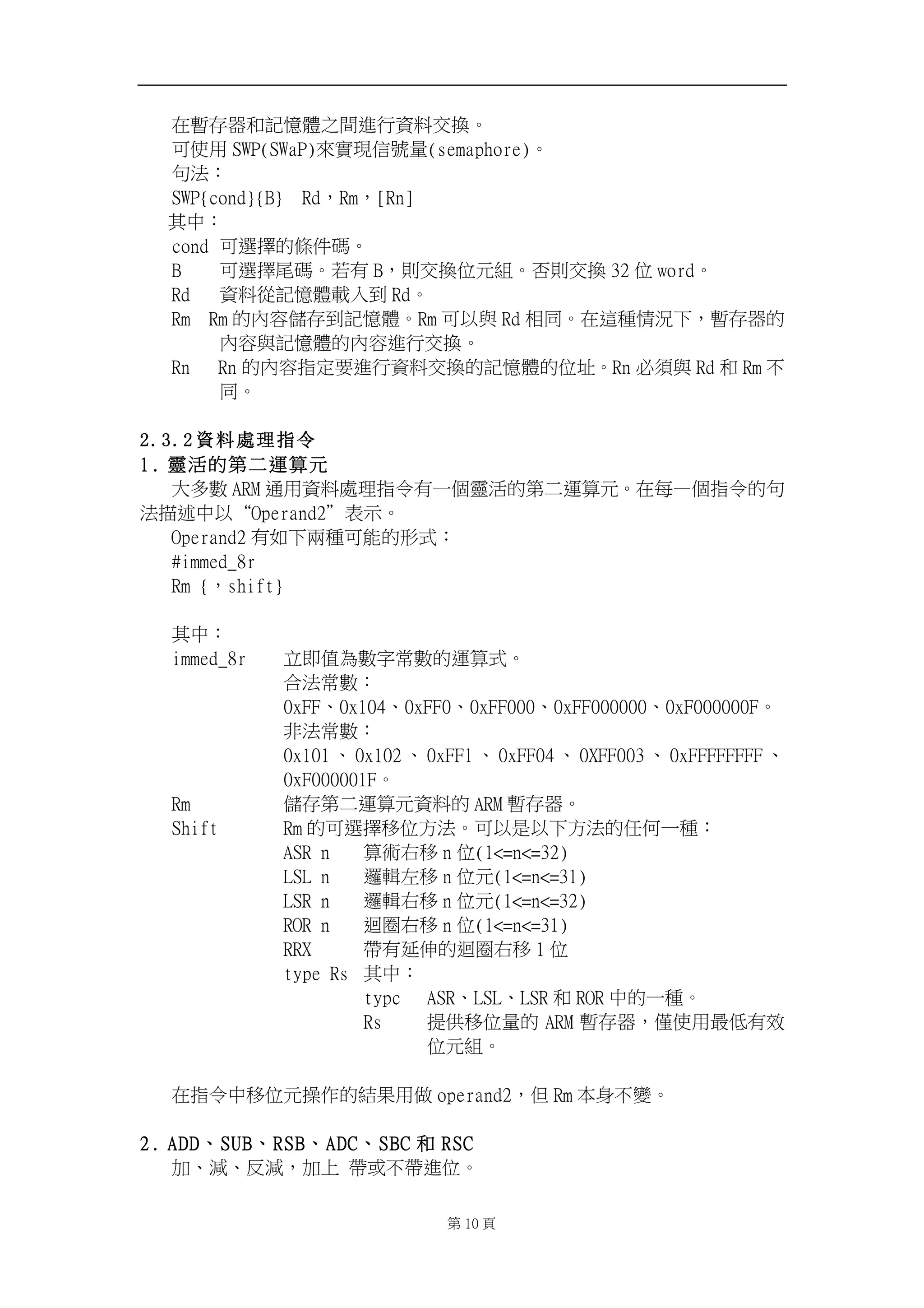

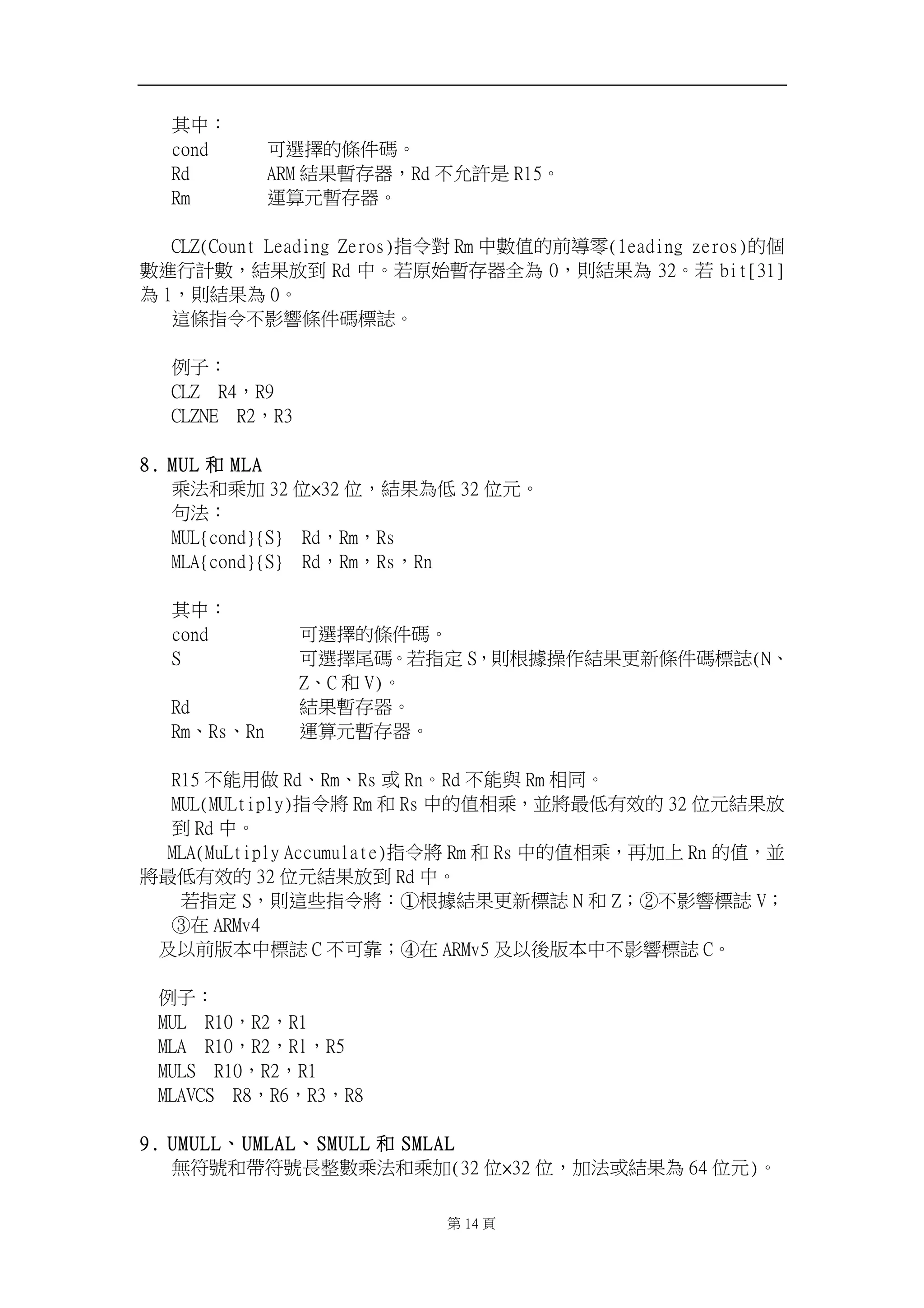

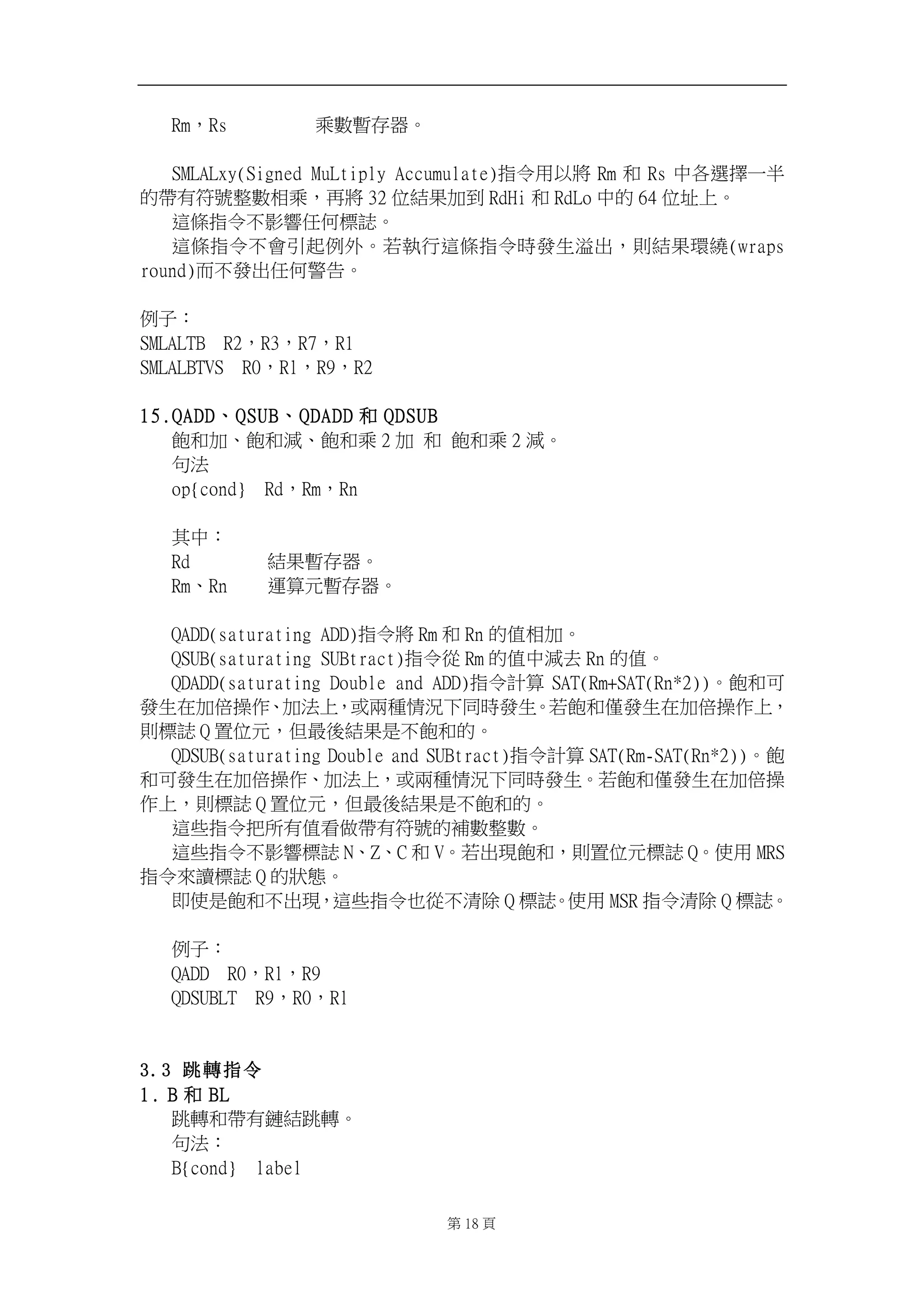

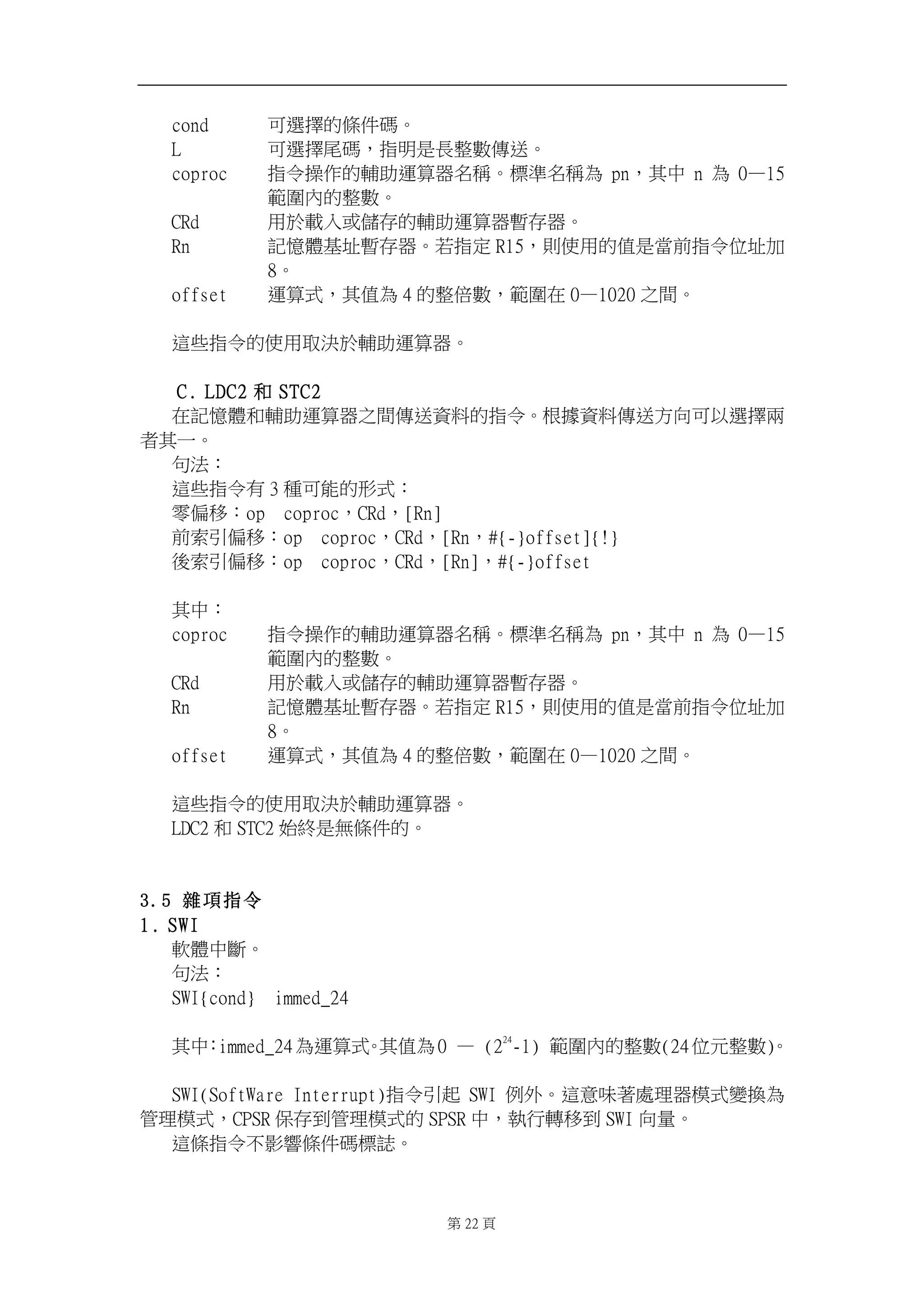

Memory Operands

° Complex data structures – array/structures – are kept in memory

° Arithmetic operations occur only on registers in MIPS instr.

• MIPS must include instructions that transfer data between memory and

registers

- Data transfer instructions

• To access a word in memory, the instruction must supply the memory

‘address’

UEE 3303 <5> YL Huang Spring‘14 © NCTU

Byte vs. Word

° Bytes are nice, but most data items use larger

"words"

° For MIPS, a word is 32 bits or 4 bytes.

0

4

8

12

...

32 bits of data

Word must start at addr

32 bits of data

the are multiples of 4

32 bits of data

32 bits of data Registers hold 32 bits of data

° 232 bytes with byte addresses from 0 to 232-1

° 230 words with byte addresses 0, 4, 8, ... 232-4

° Words are aligned

i.e., what are the least 2 significant bits of a word address?

- Left most: big endian

- Right most: little endian

UEE 3303 <6> YL Huang Spring‘14 © NCTU

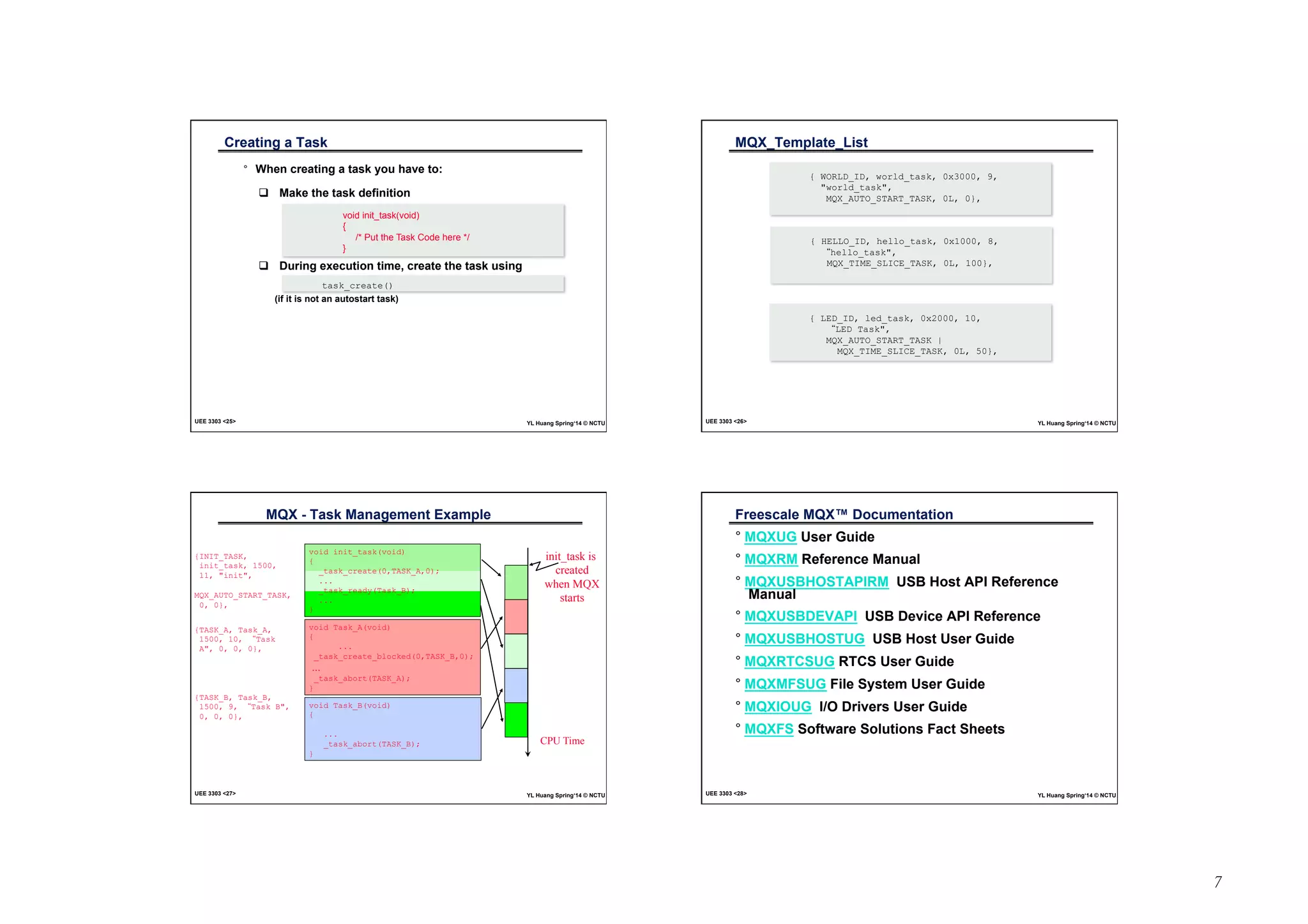

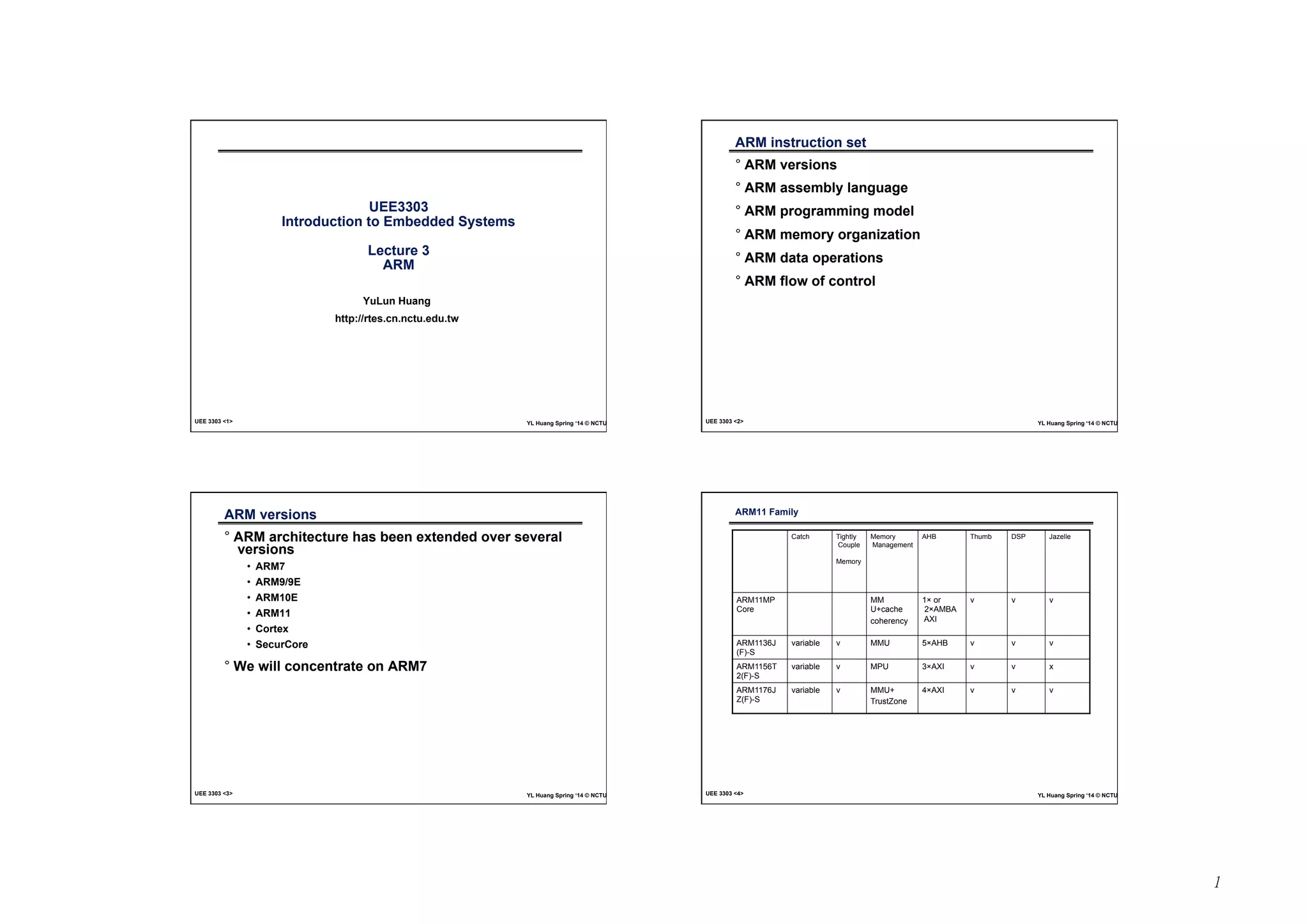

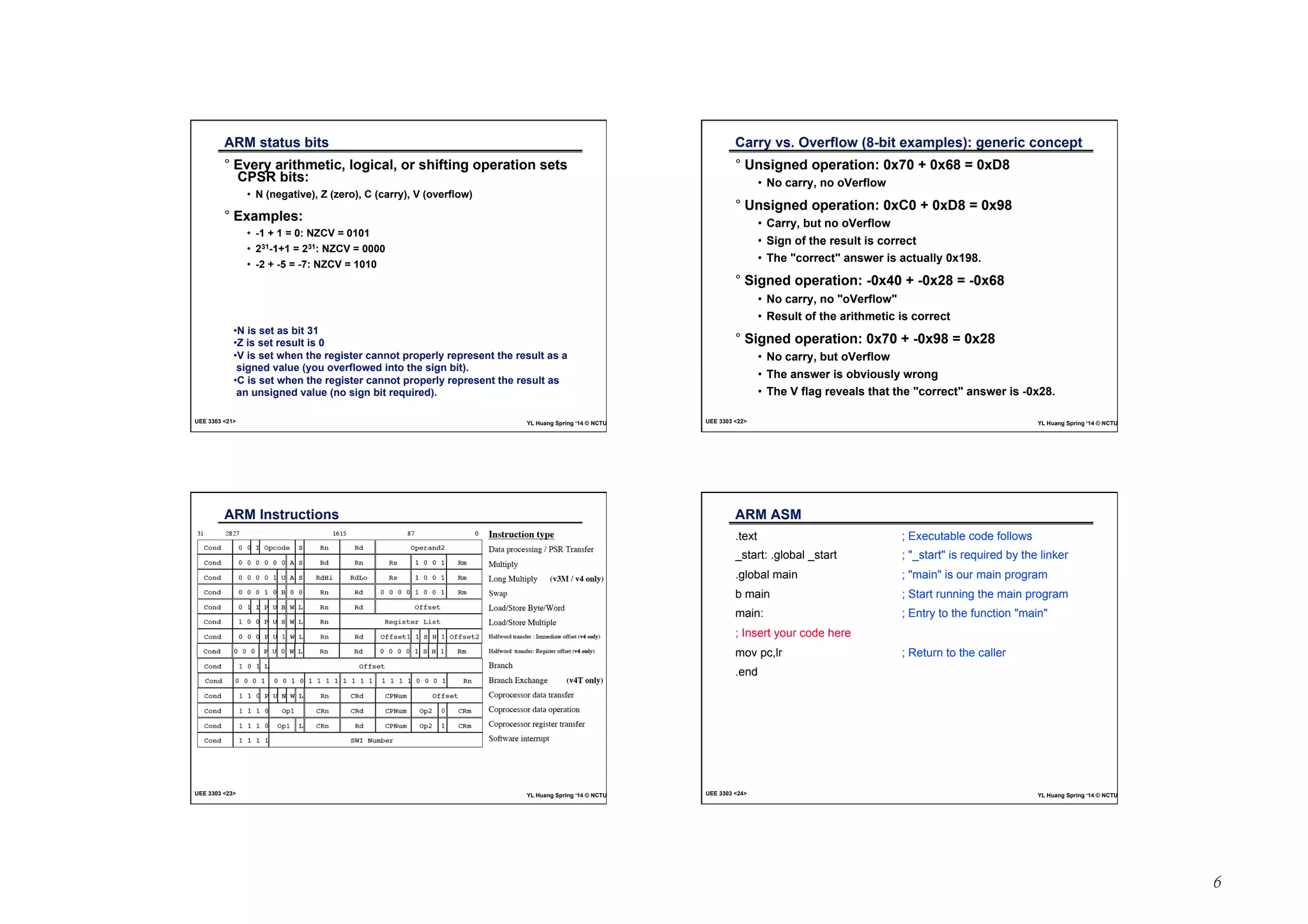

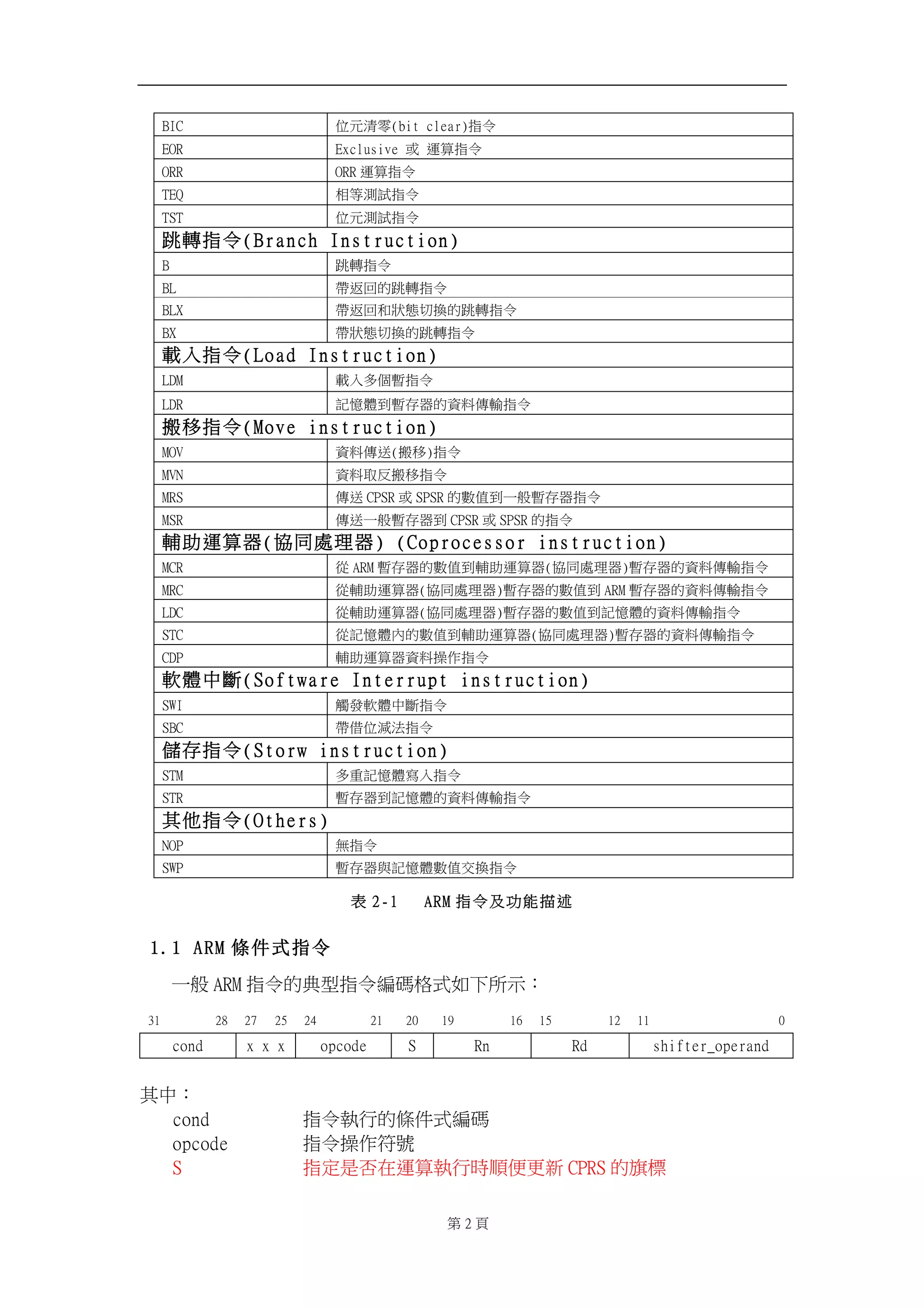

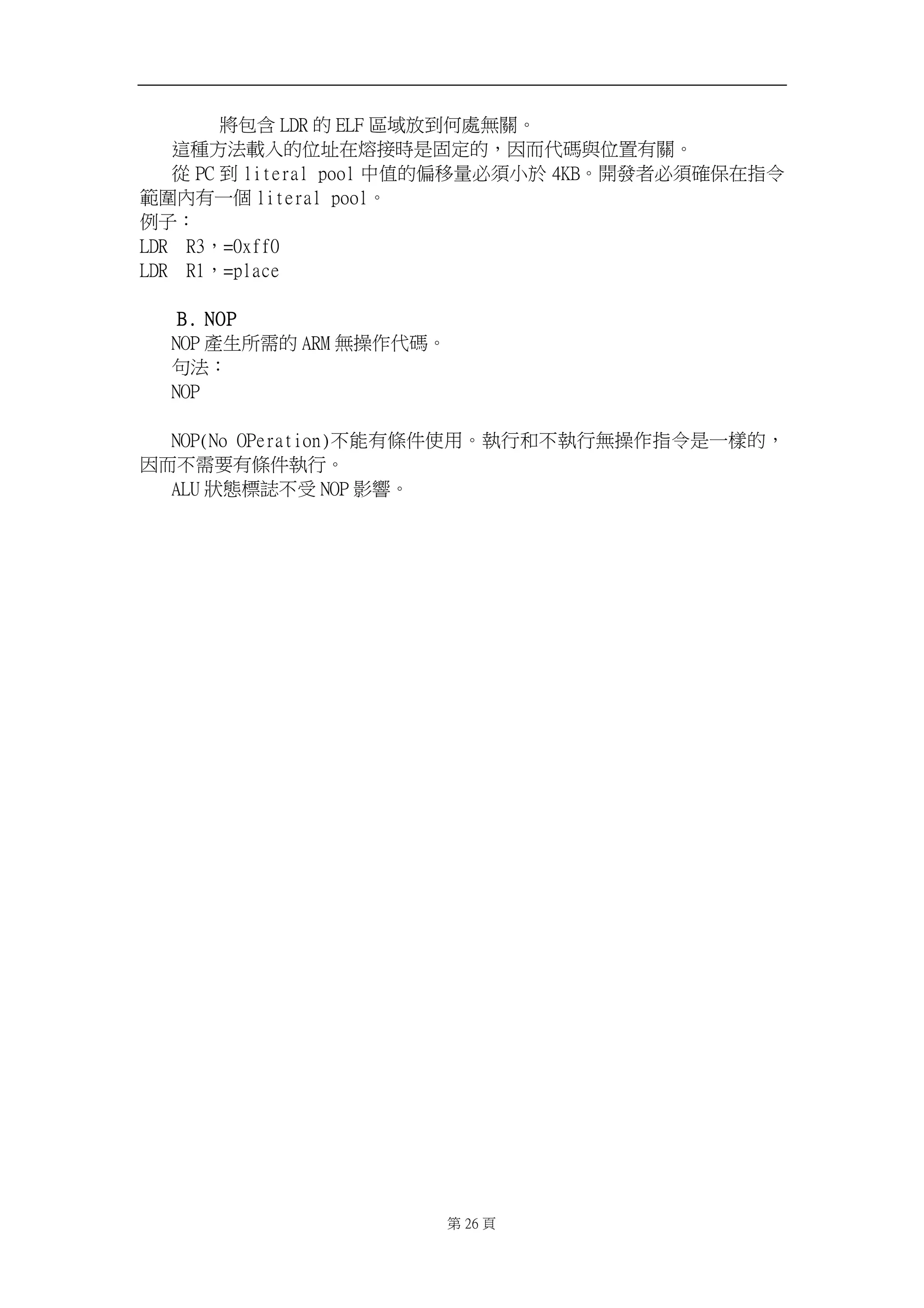

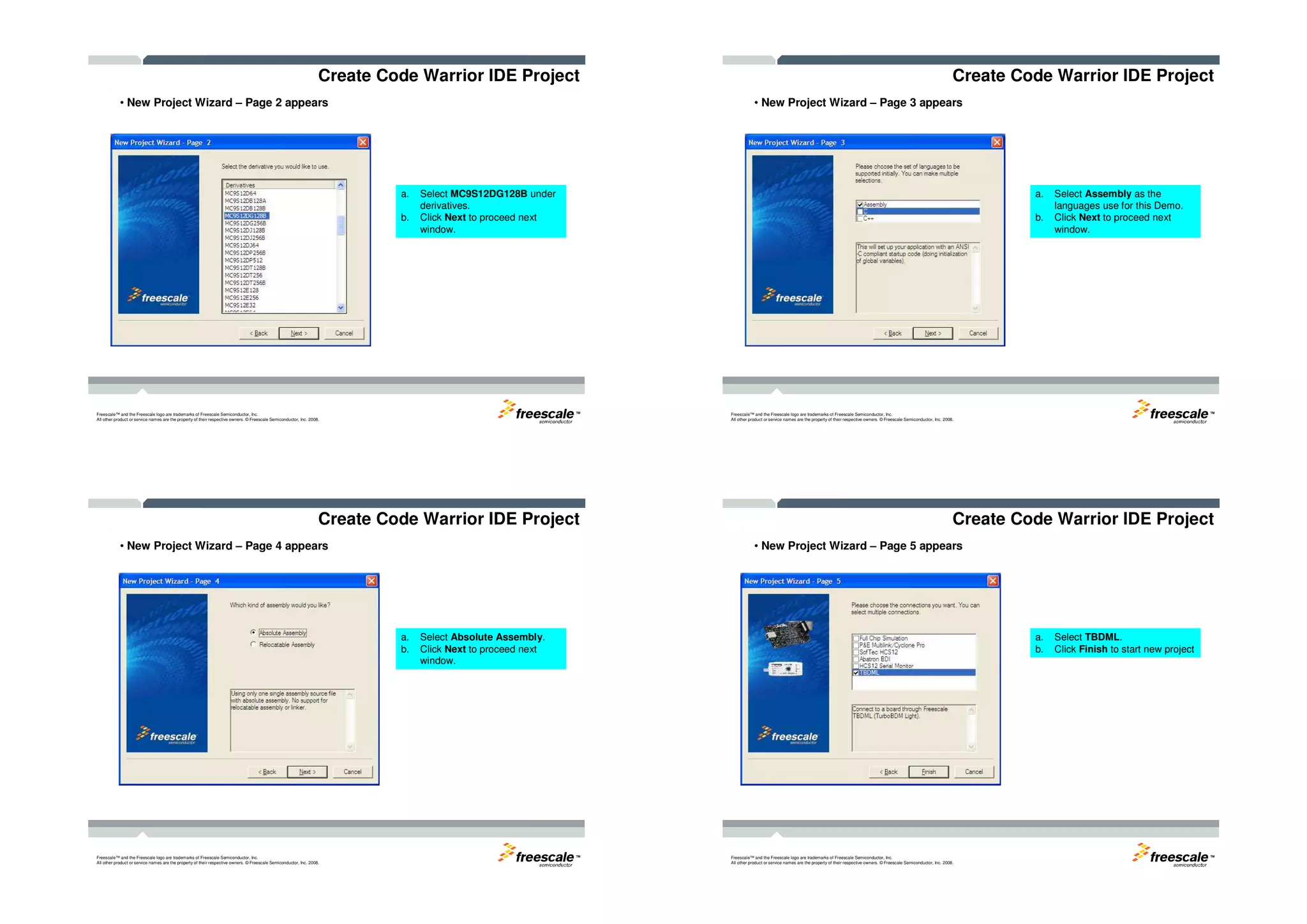

Instructions

° Load and store instructions

° Example:

C code: A[12] = h + A[8];

MIPS code: lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3)

1. h is associated with $s2

2. base addr of array A is in

$s3

° Can refer to registers by name (e.g., $s2, $t2) instead of number

° Store word has destination last

° Remember arithmetic operands are registers, not memory!

Can’t write: add 48($s3), $s2, 32($s3)

UEE 3303 <7> YL Huang Spring‘14 © NCTU

So far

° Instruction Meaning

add $s1,$s2,$s3 $s1 = $s2 + $s3

sub $s1,$s2,$s3 $s1 = $s2 – $s3

lw $s1,100($s2) $s1 = Memory[$s2+100]

sw $s1,100($s2) Memory[$s2+100] = $s1

bne $s4,$s5,L Next instr. is at Label if $s4 ≠ $s5

beq $s4,$s5,L Next instr. is at Label if $s4 = $s5

j Label Next instr. is at Label

° Formats:

?

op rs rt rd shamt funct

op rs rt 16 bit address

op 26 bit address

R

I

J

R: register

I: immediate

UEE 3303 <8> YL Huang Spring‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-6-2048.jpg)

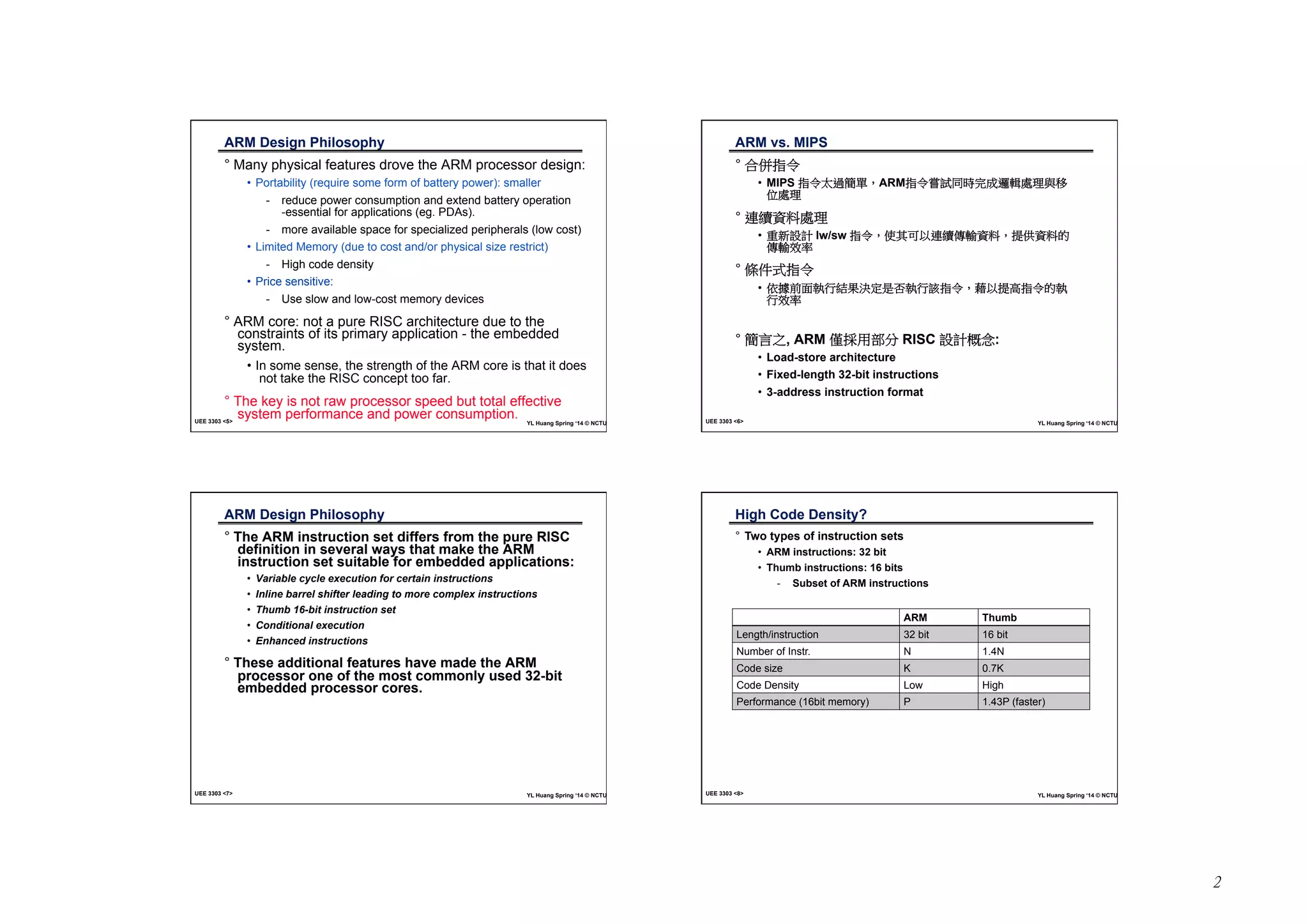

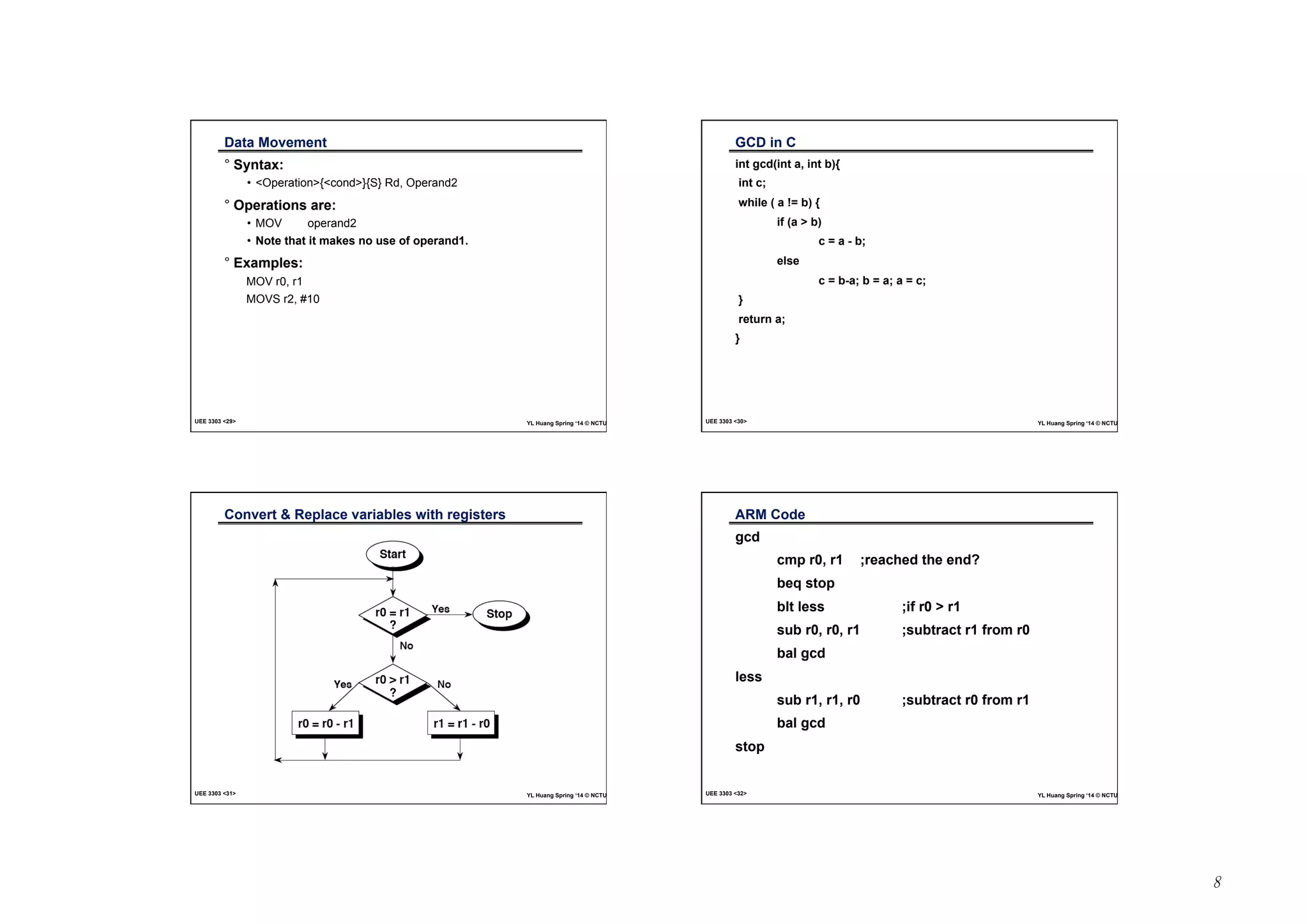

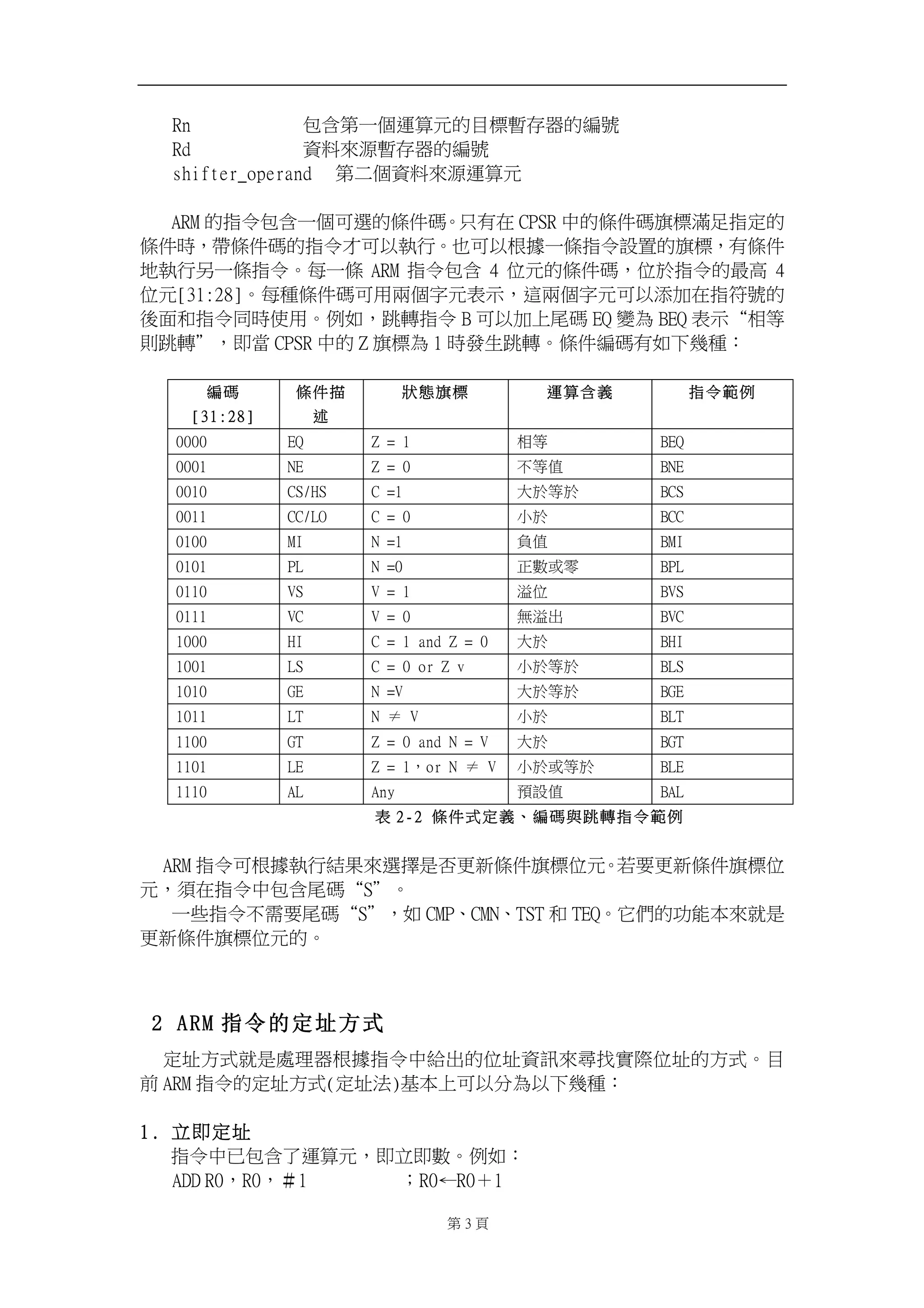

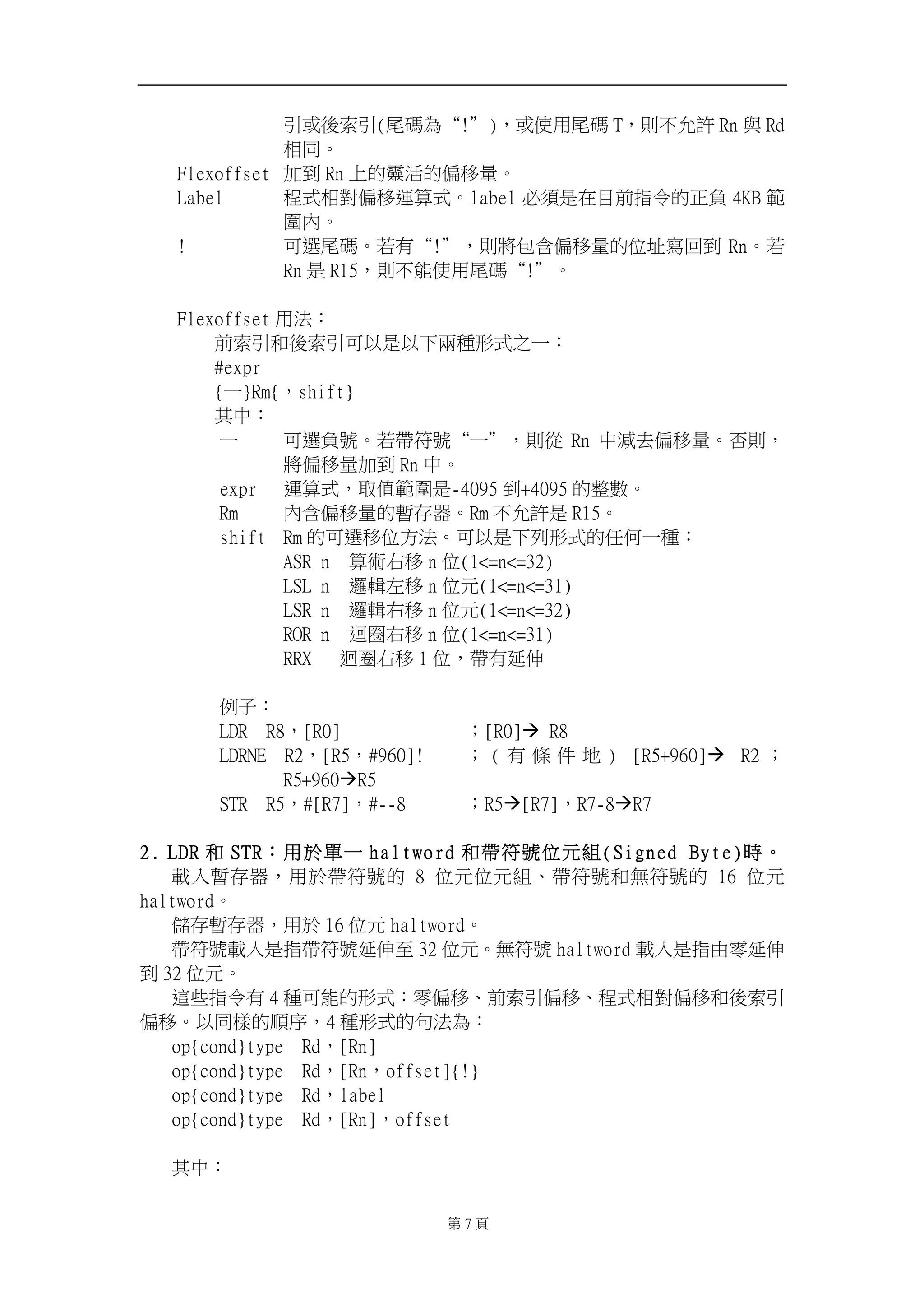

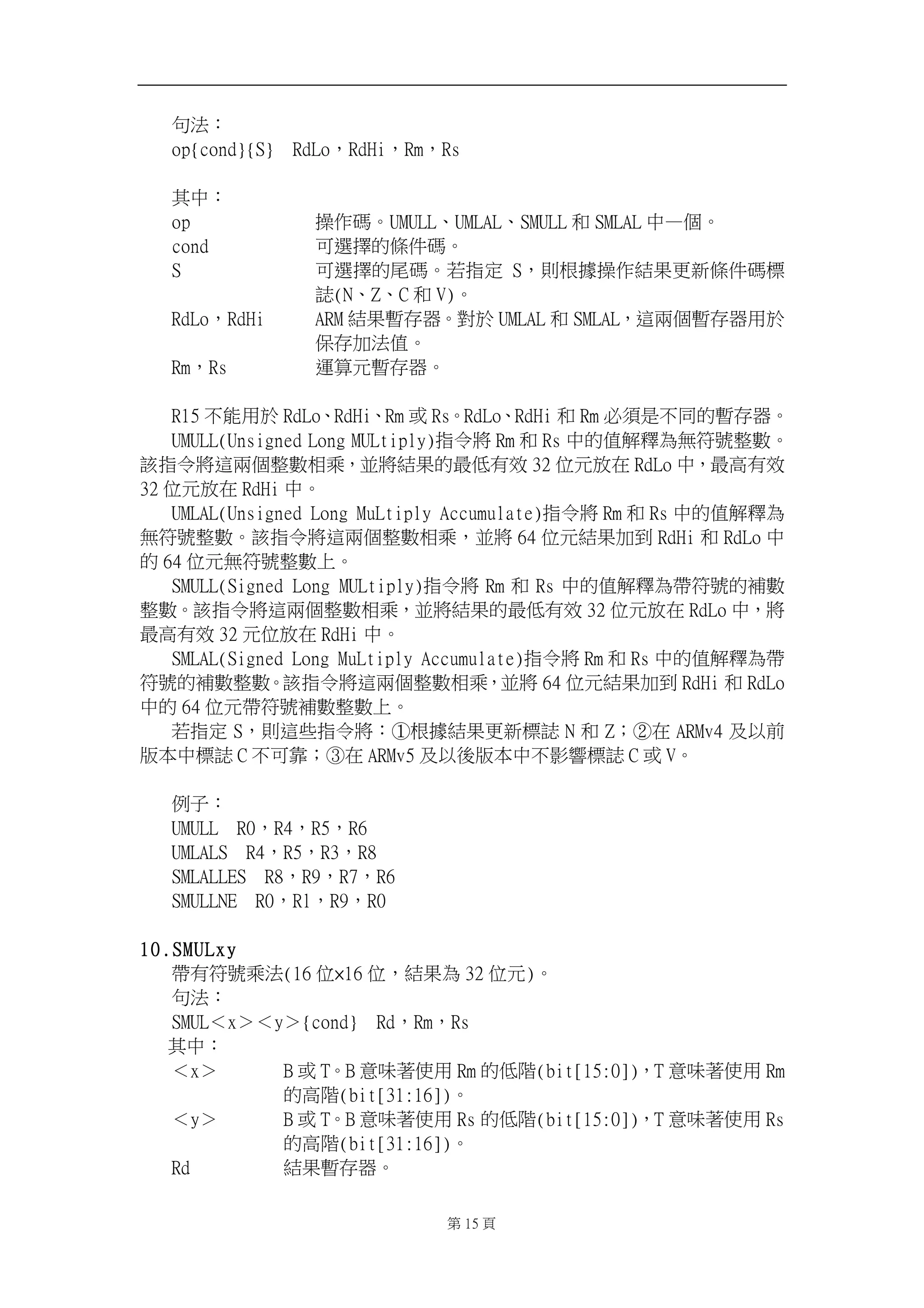

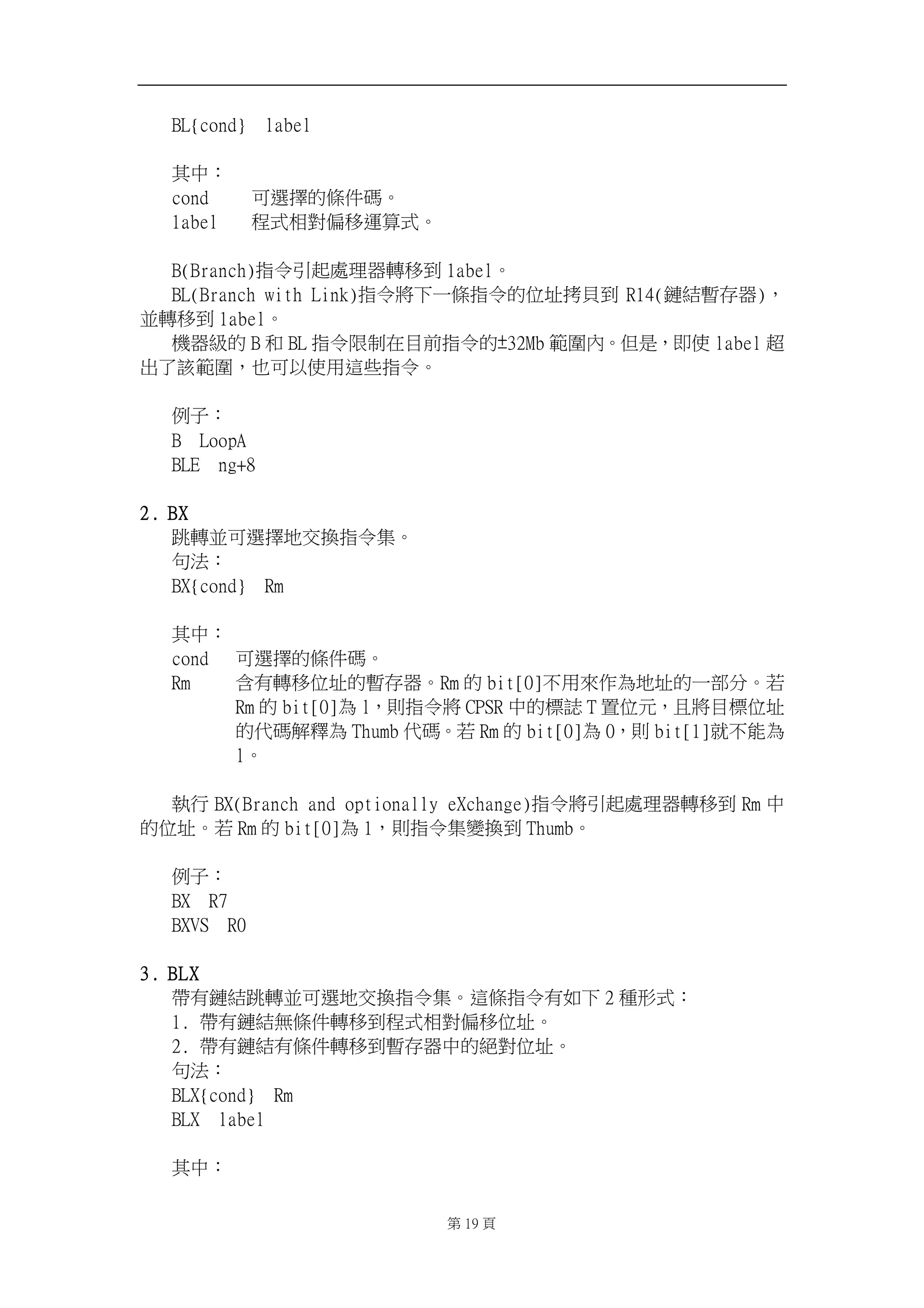

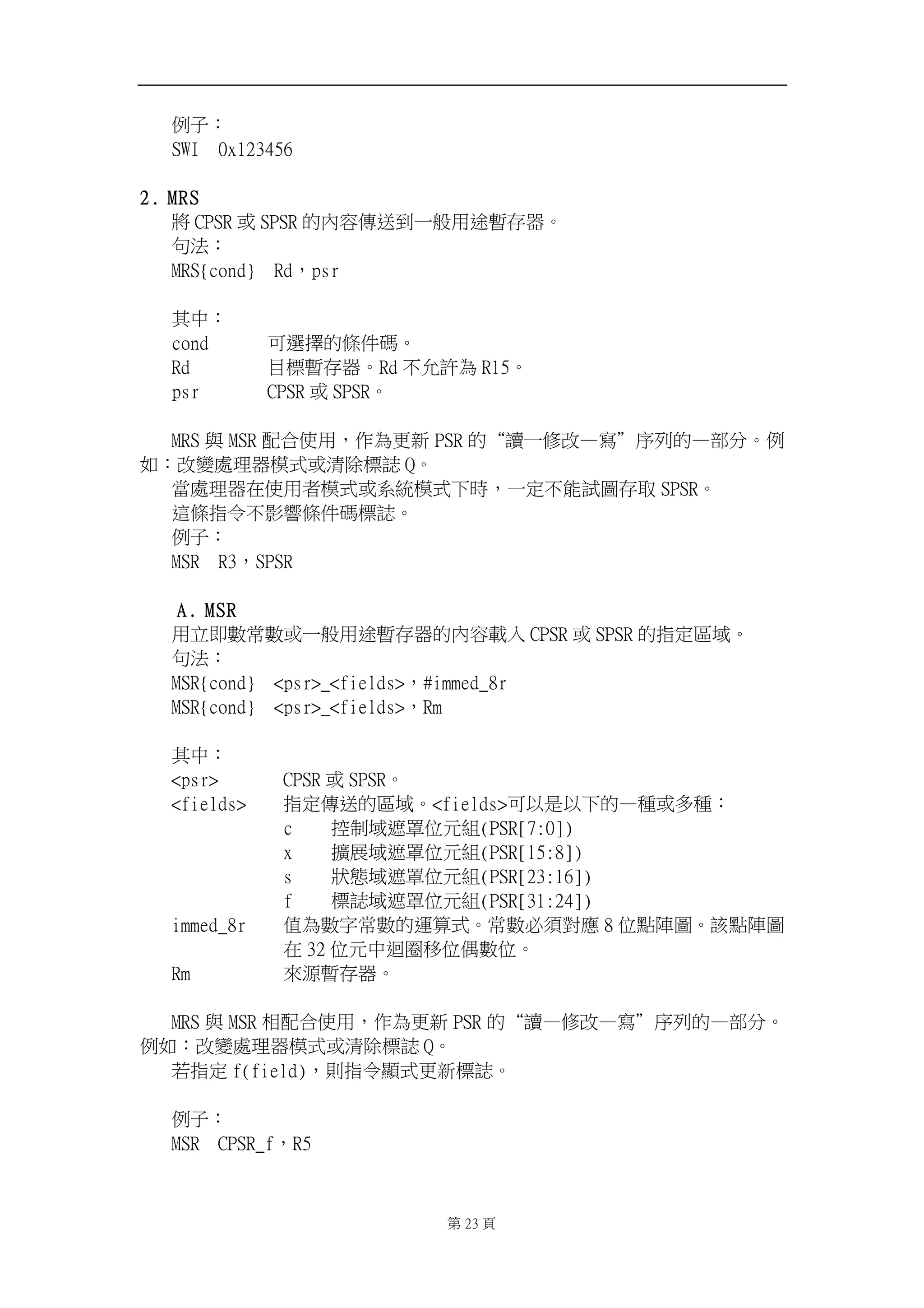

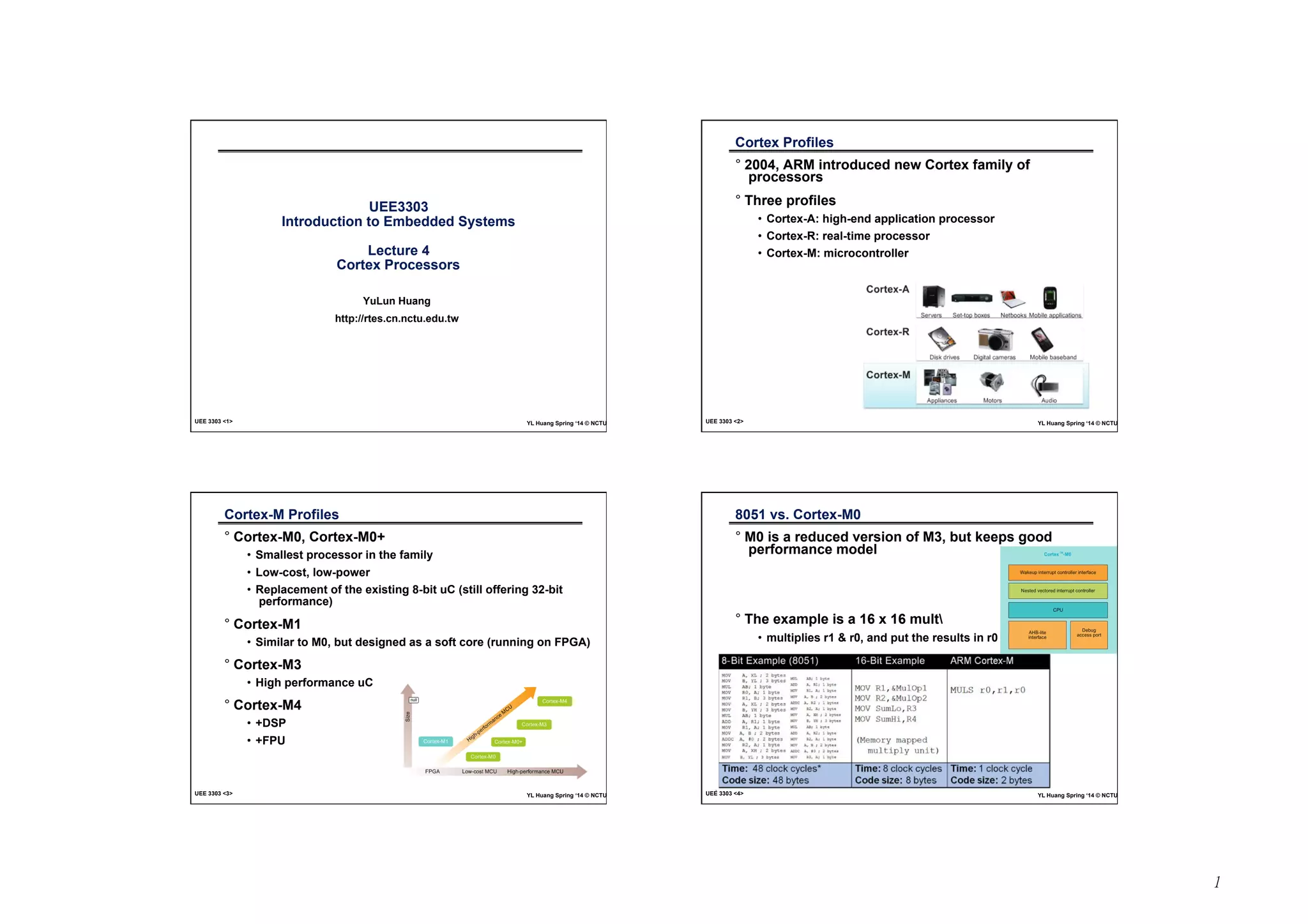

![3

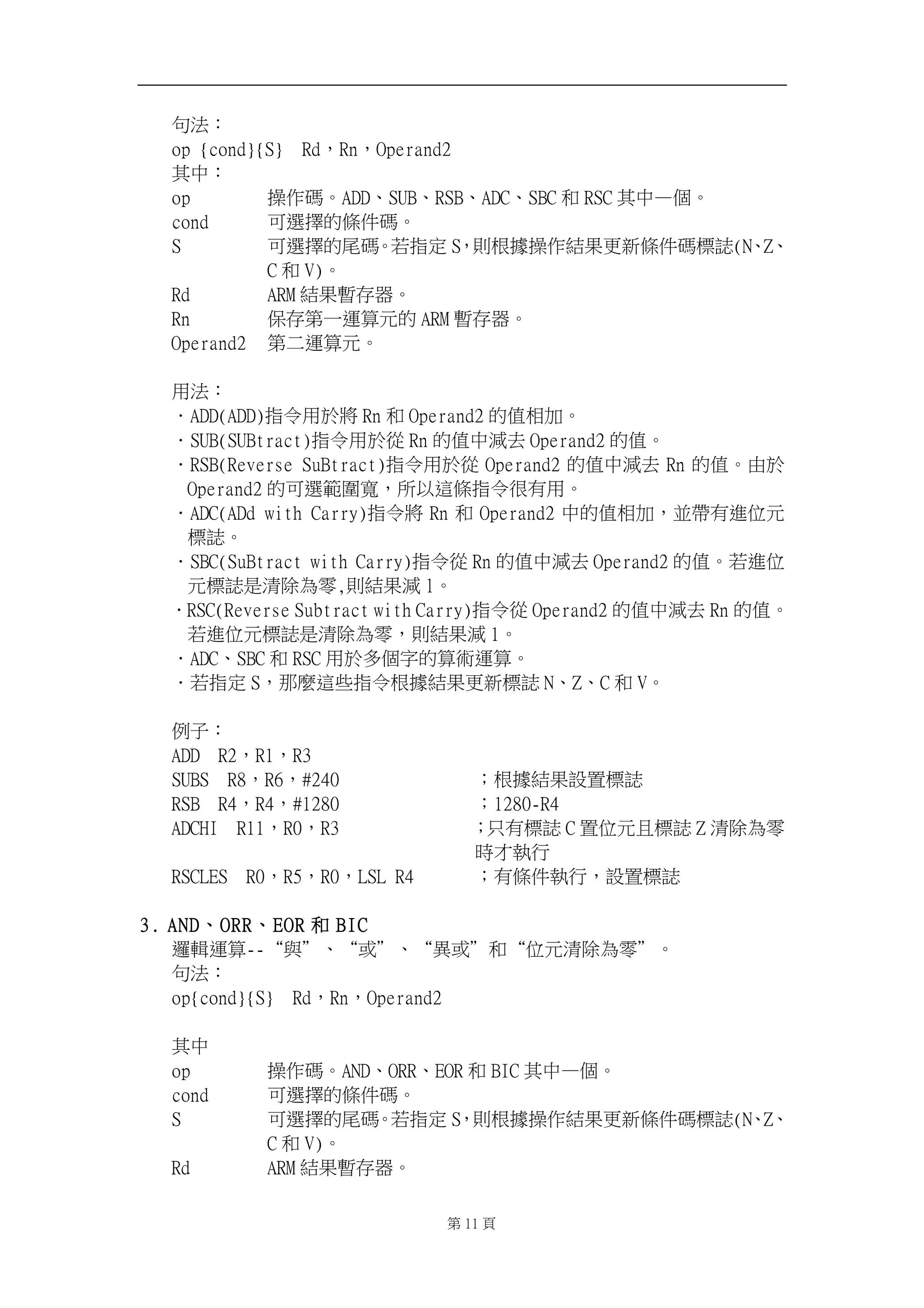

Different ARM cores: StrongARM vs. XscaleĎ

CatchĎ Tightly

Couple

MemoryĎ

Memory

Mangem

entĎ

AHBĎ Thumb Ď DSP Ď Jazelle Ď

Strong

ARM Ď

16K/8K Ď xĎ MMU Ď N/A Ď xĎ xĎ xĎ

XScale Ď 32K/32K Ď xĎ MMU Ď N/A Ď vĎ vĎ xĎ

UEE 3303 <9> YL Huang Spring ‘14 © NCTU

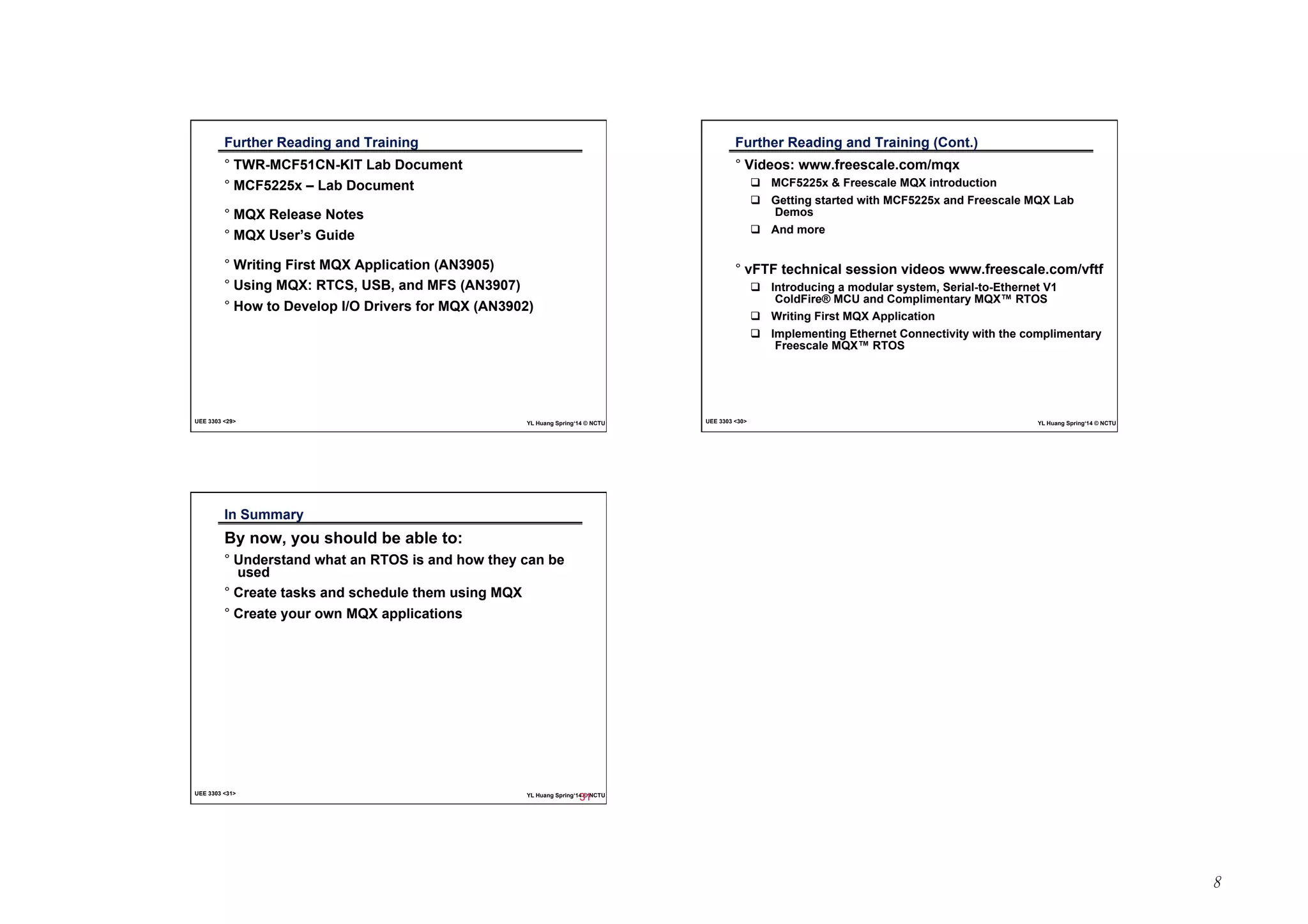

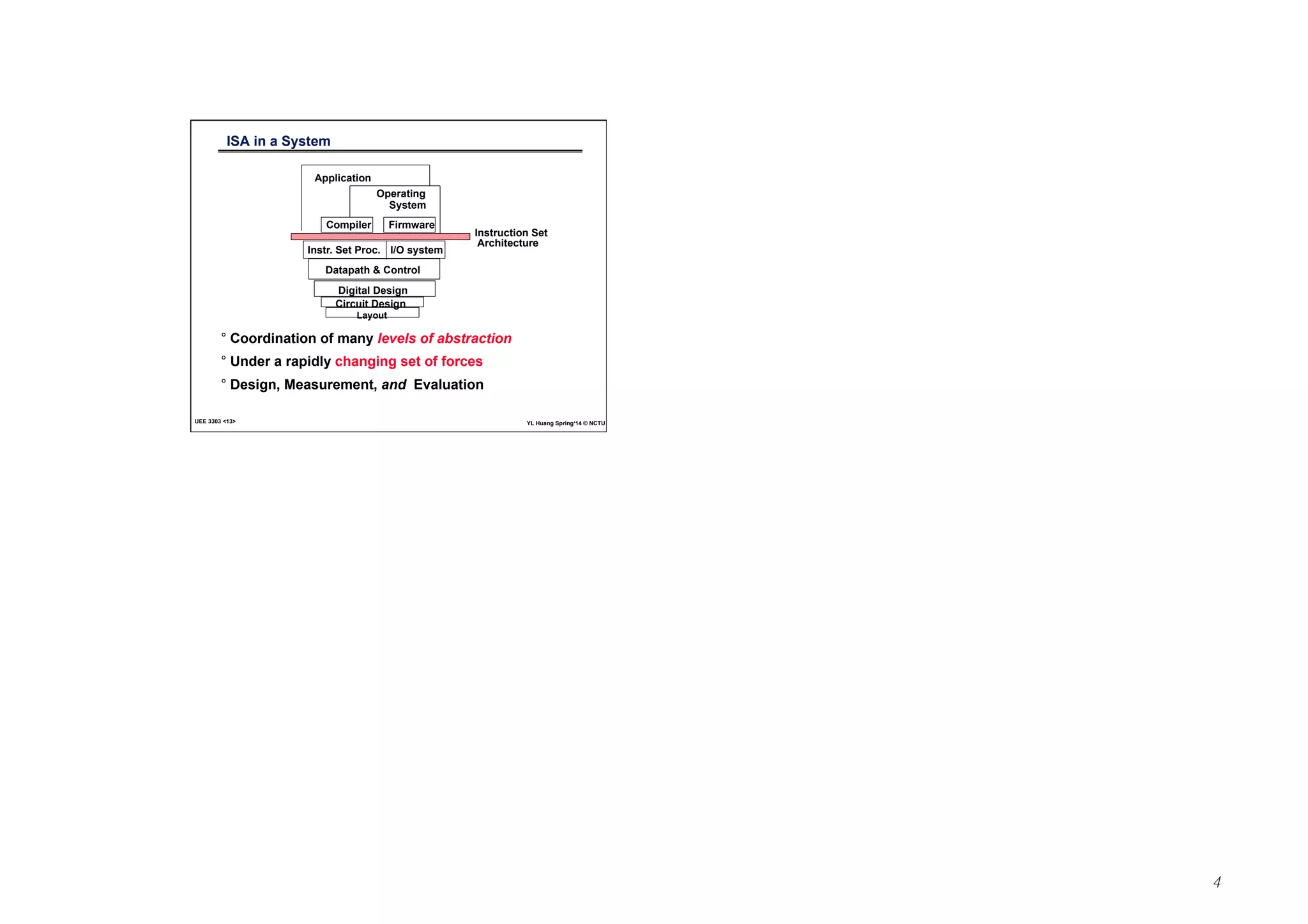

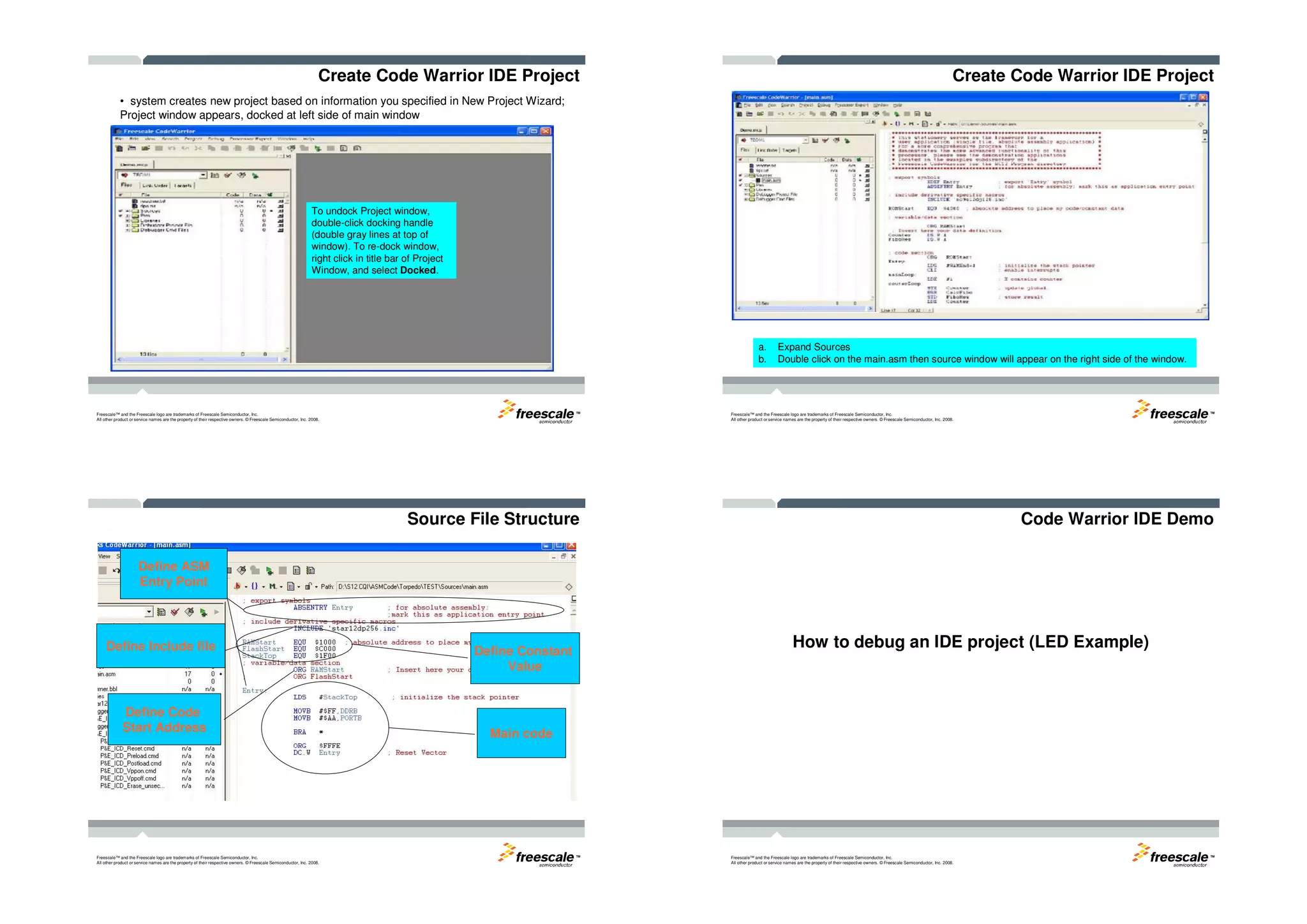

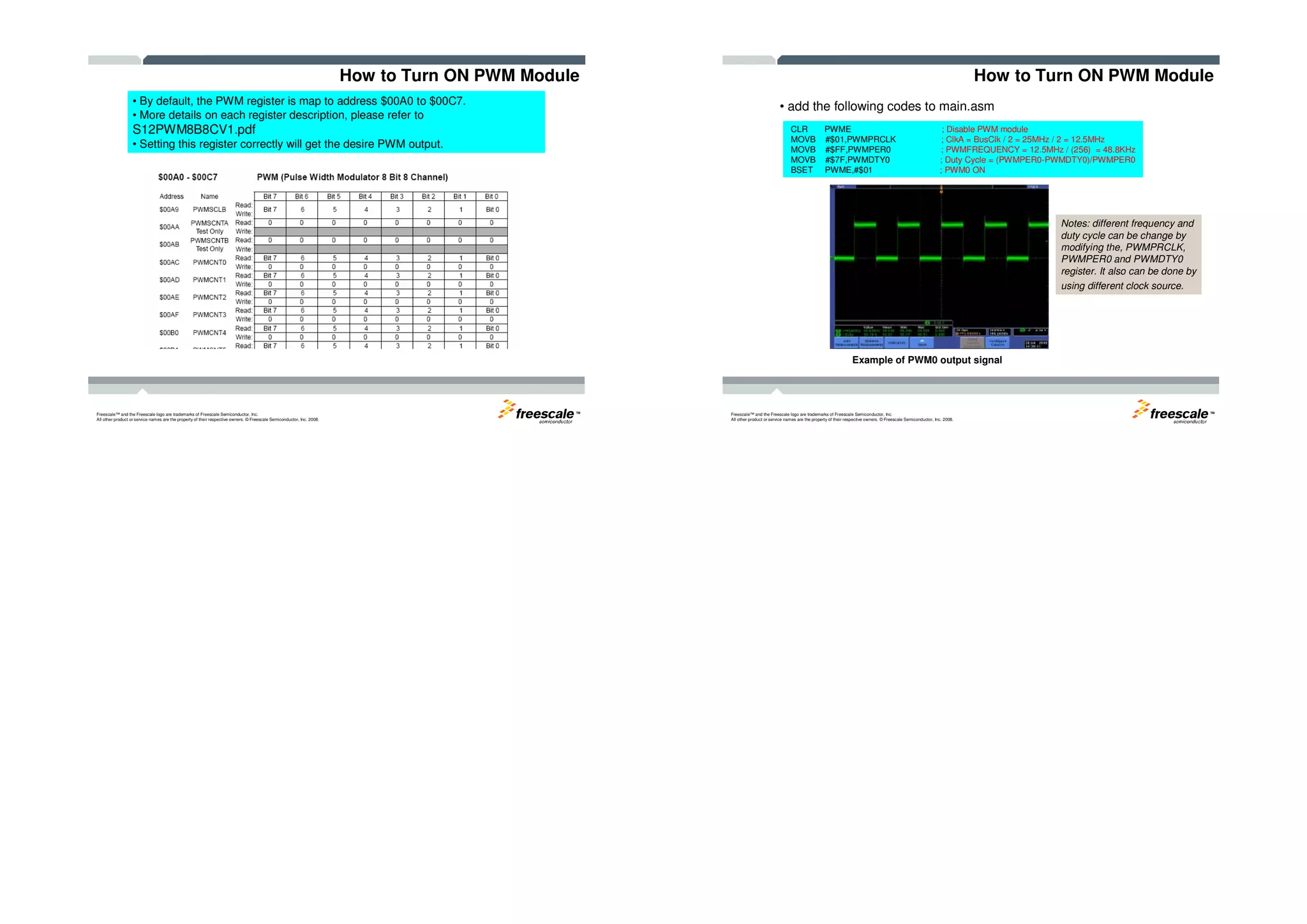

ARM ArchitectureĎ

° 7 modes

• usr – normal execution

• sys – privileged OS tasks

• fiq – fast interrupt

• irq – general interrupt

• svc – protected mode for OS

• abt – vir mem (mem protect)

• und – for s/w emulation

° 37 registers

• 30: general purpose

• 6: status

• 1: program counter

UEE 3303 <10> YL Huang Spring ‘14 © NCTU

ModesĎ

ModeĎ CodeĎ DescriptionĎ

User (usr)Ď 10000Ď Normal mode; only condition flags in cpsr

can be changedĎ

FIQ (fiq)Ď 10001Ď Fast interruptĎ

IRQ (irq)Ď 10010Ď Normal interruptĎ

Supervisor (svc)Ď 10011Ď OS kernelĎ

Abort (abt)Ď 10111Ď Memory protectionĎ

Undefined (und)Ď 11011Ď Software emulationĎ

System (sys)Ď 11111Ď Normal mode, but be able to r/w cpsrĎ

UEE 3303 <11> YL Huang Spring ‘14 © NCTU

RegistersĎ

° ARM 嗽䎮☐㚱ġ37ġᾳ㙓⬀☐炻⊭㊔

• [15] 30ᾳ忂䓐㙓⬀☐

• [1] 1 PC

• [1] 6ġᾳ䉨ン㙓⬀☐烉CPSR x 1 + SPSR x 5

° ARM 㚱ġ7ġ䧖ⶍἄ㧉⺷

• 㭷ᶨ䧖㧉⺷ᶳ悥㚱ᶨ䳬䚠⮵䘬㙓⬀☐冯ᷳ⮵ㅱ

UEE 3303 <12> YL Huang Spring ‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-10-2048.jpg)

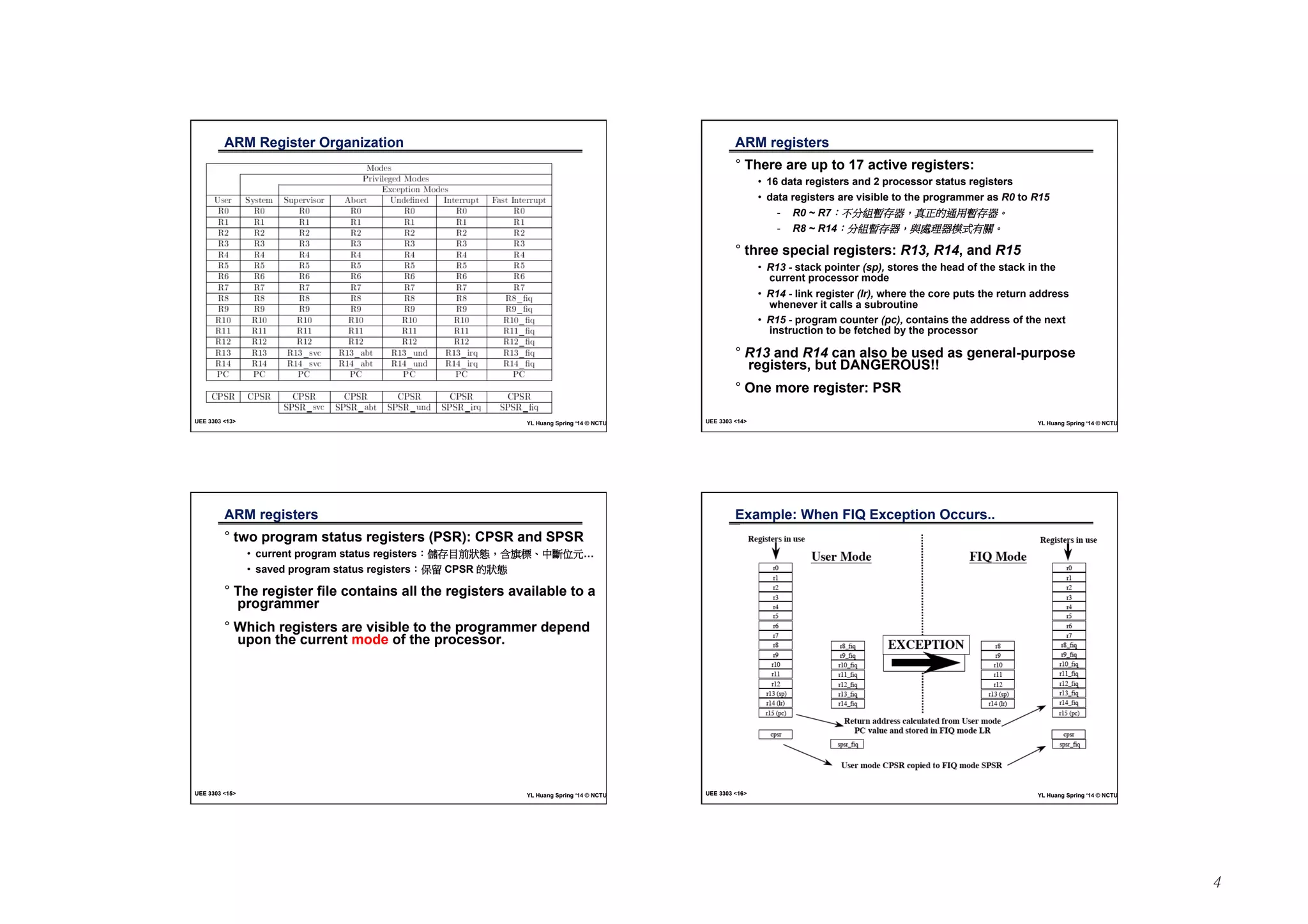

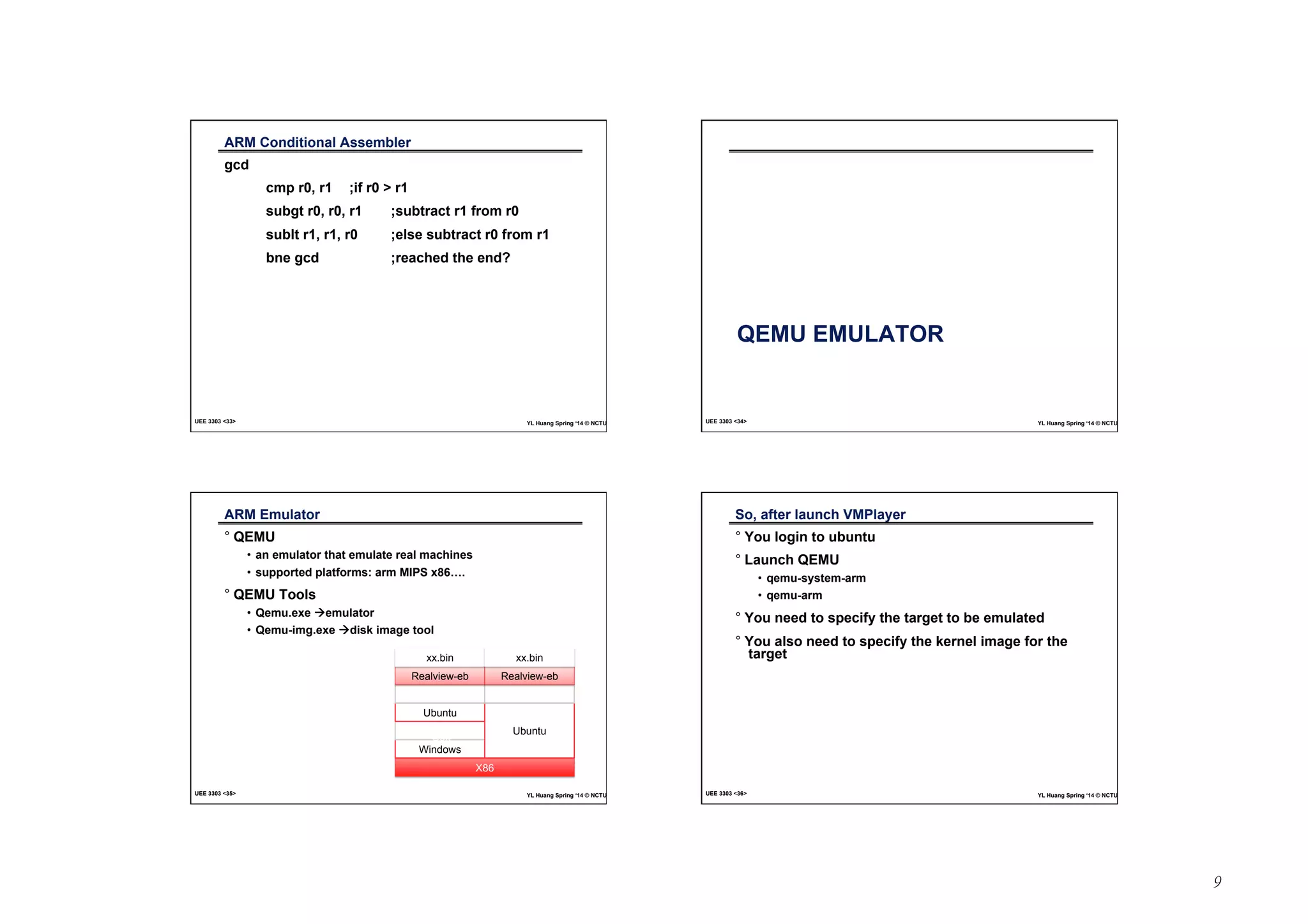

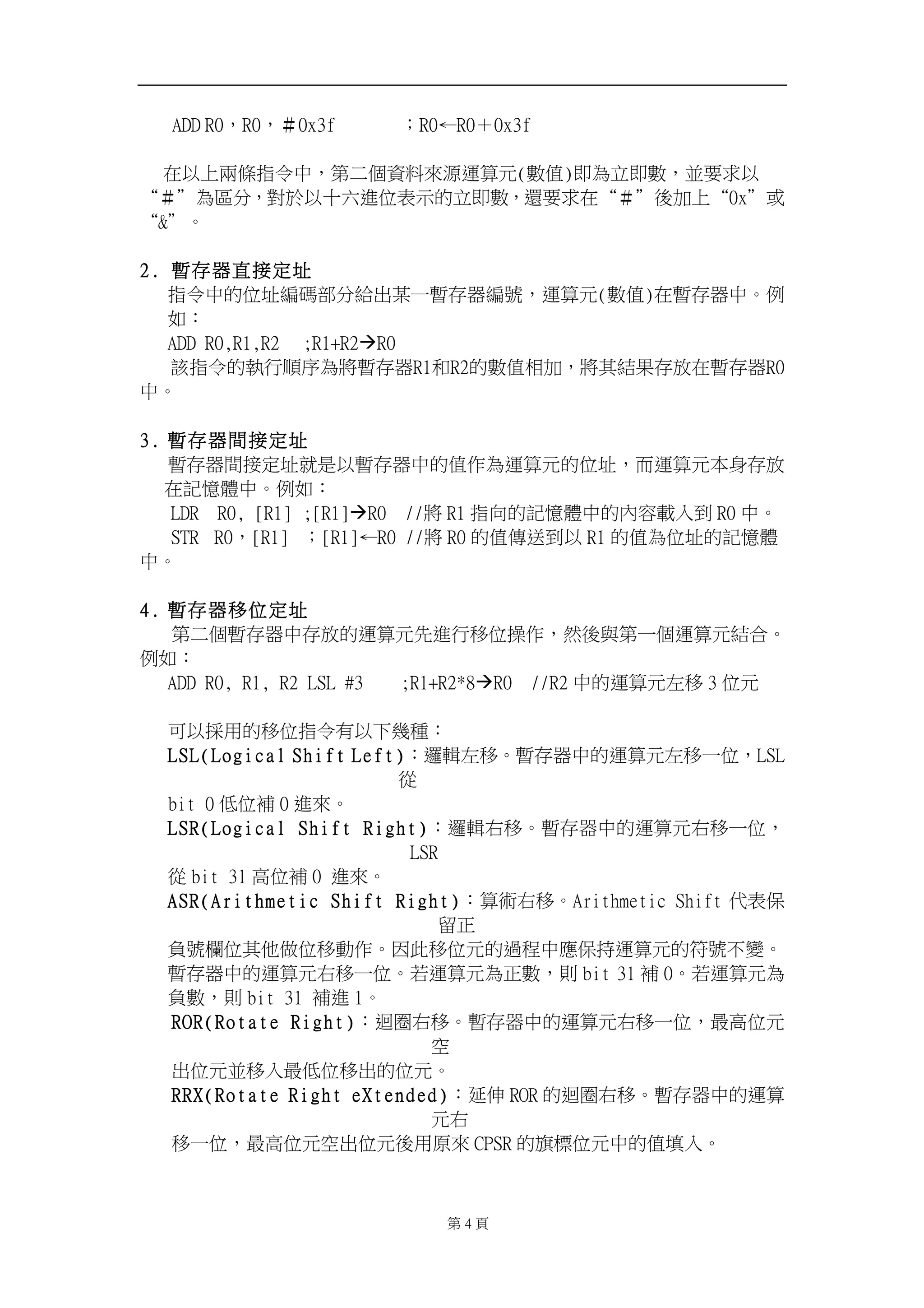

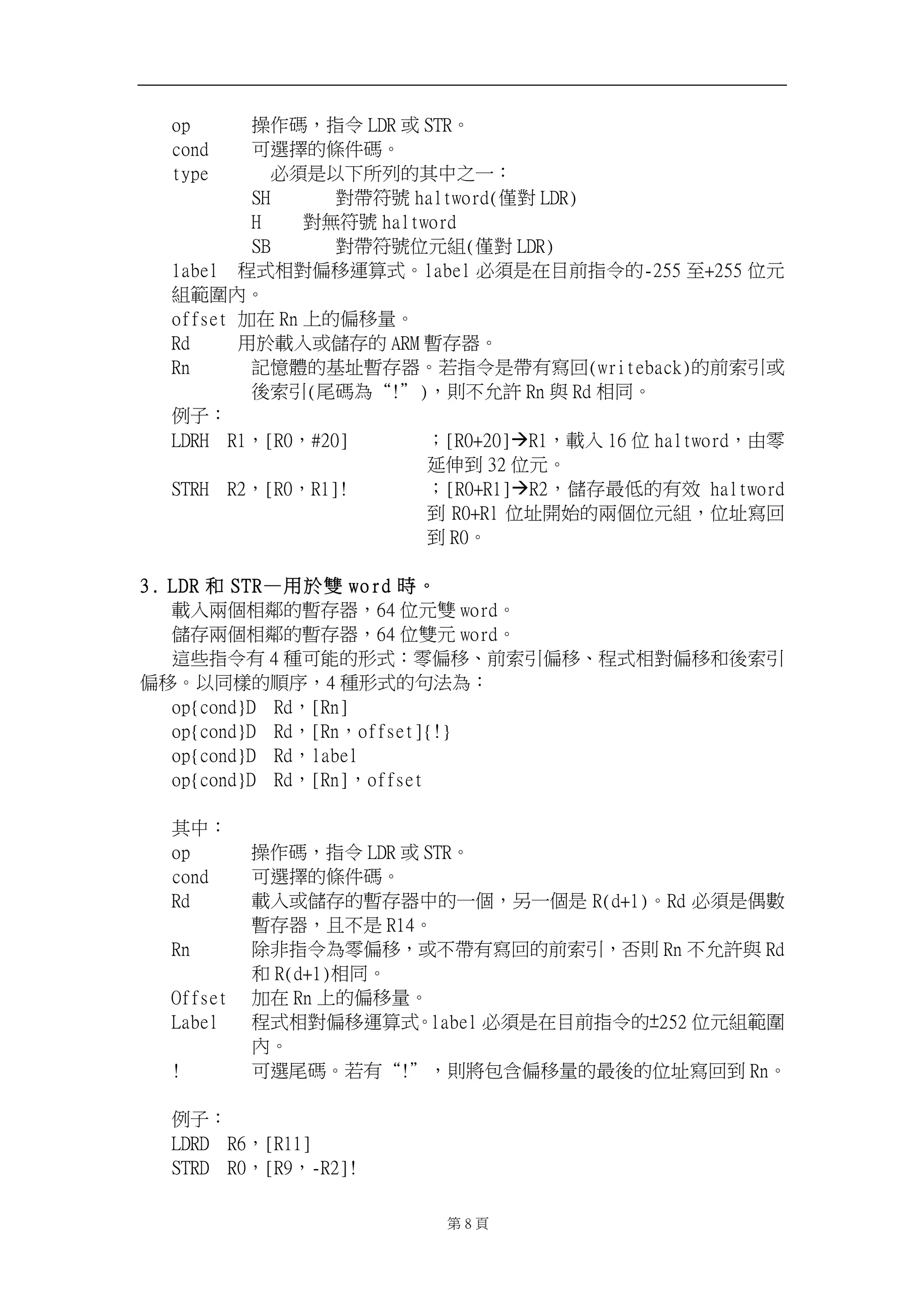

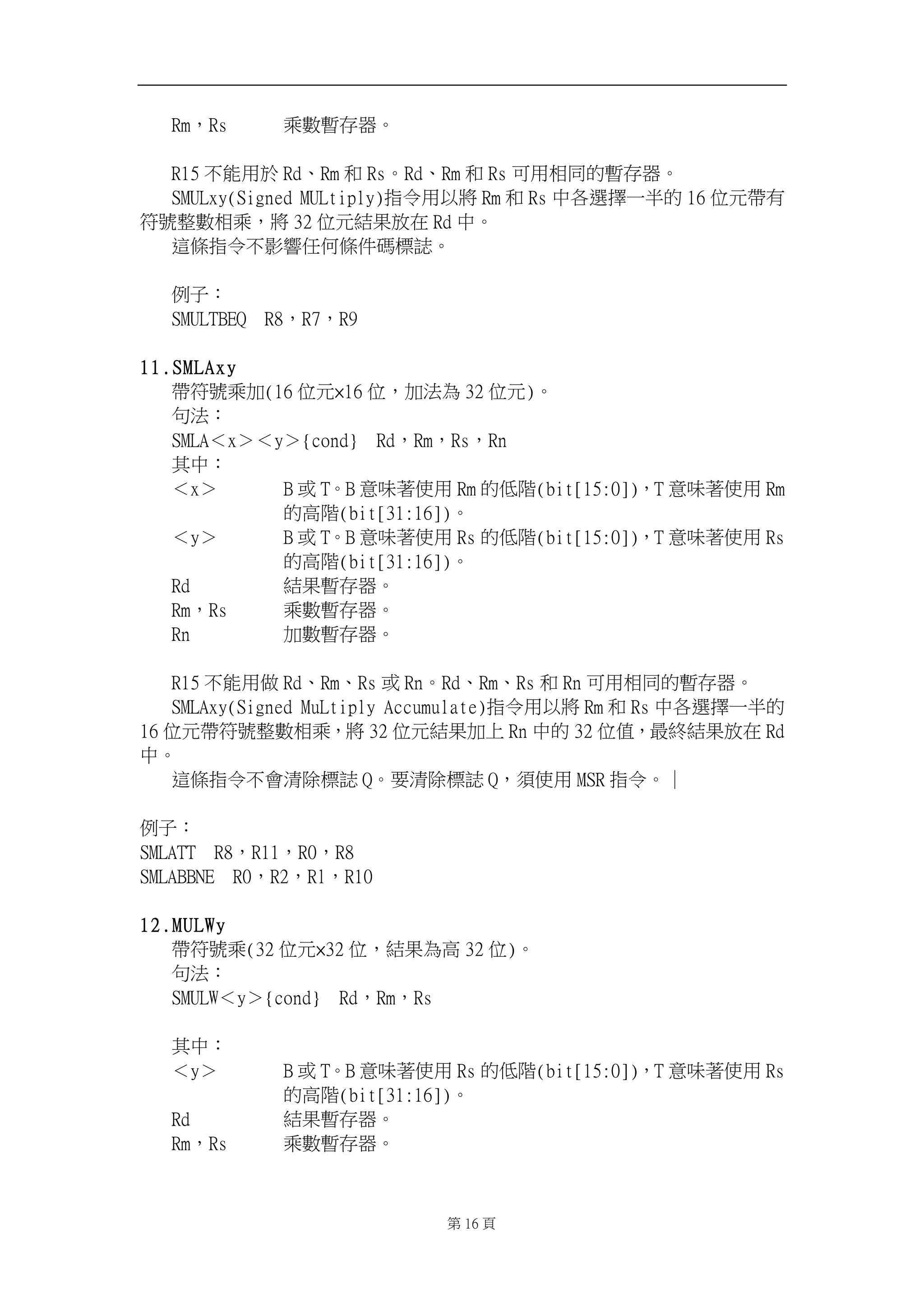

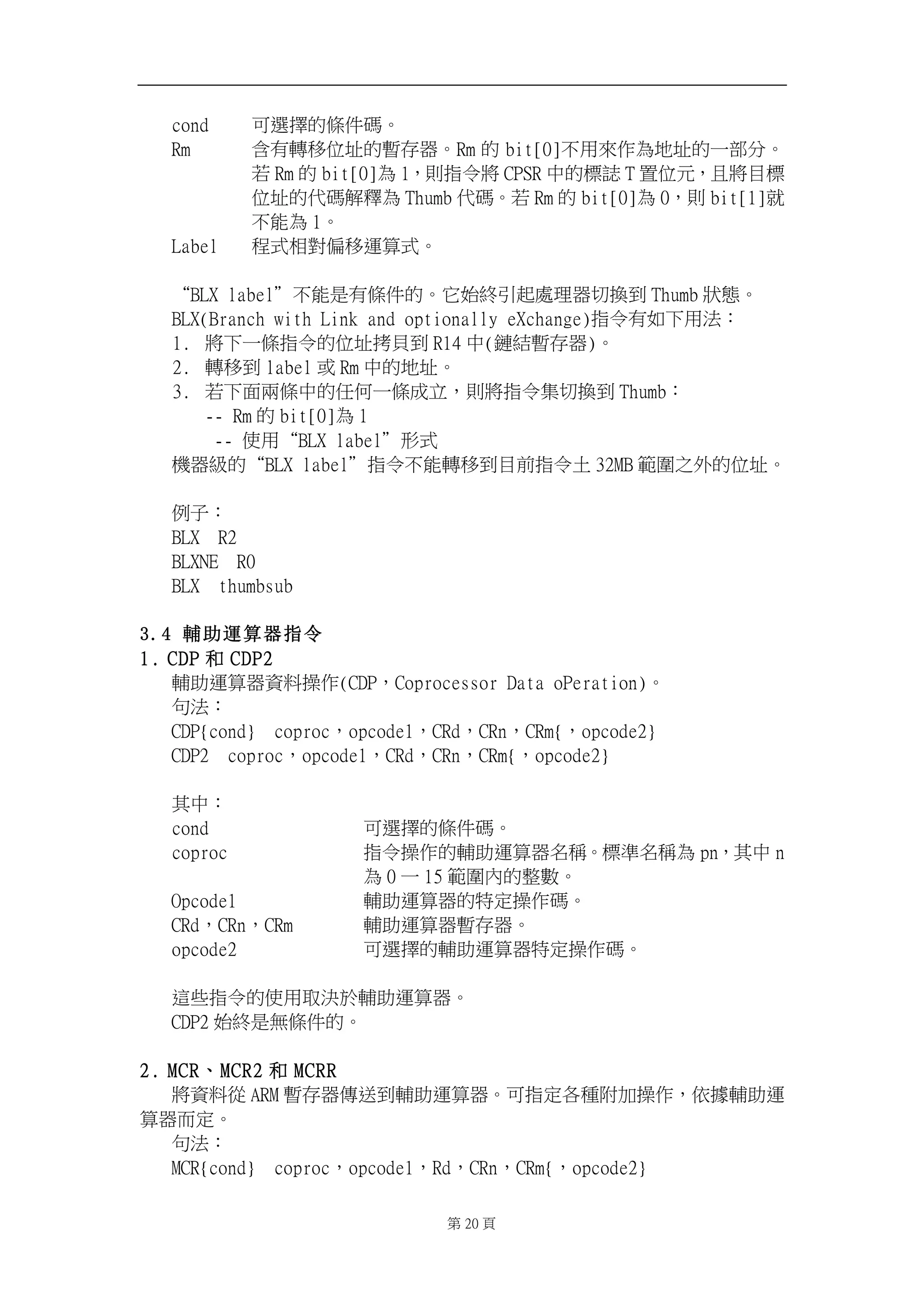

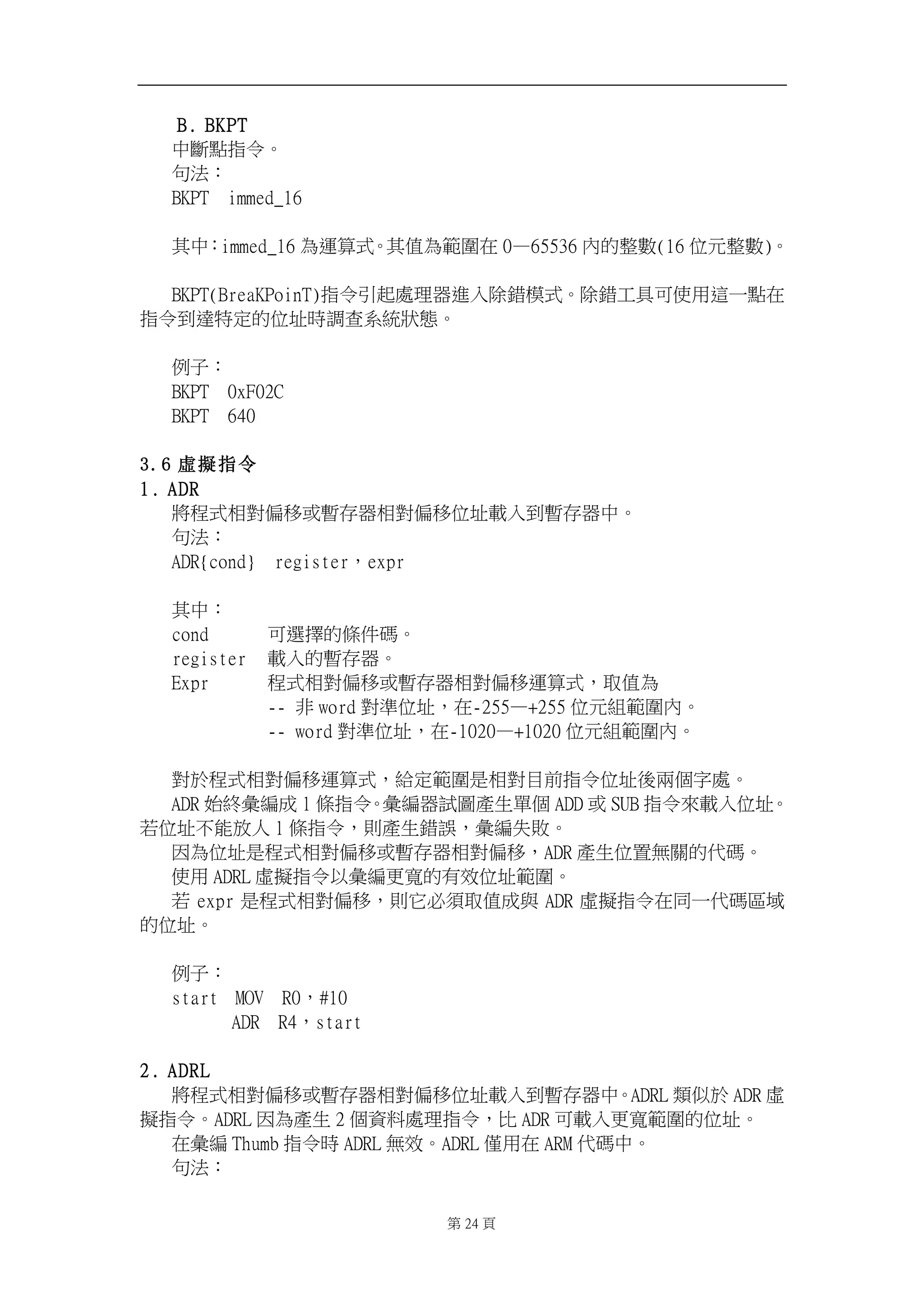

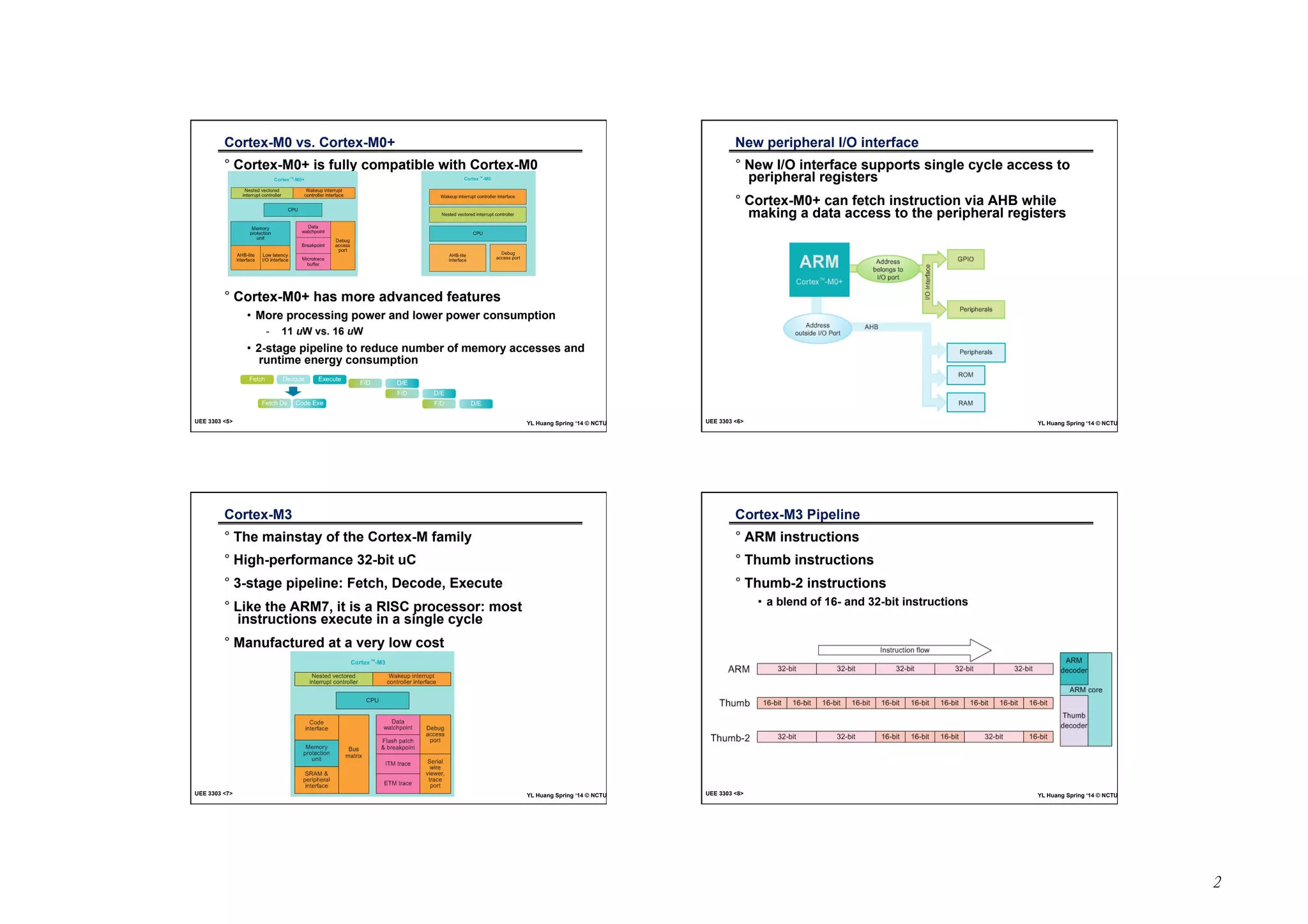

![7

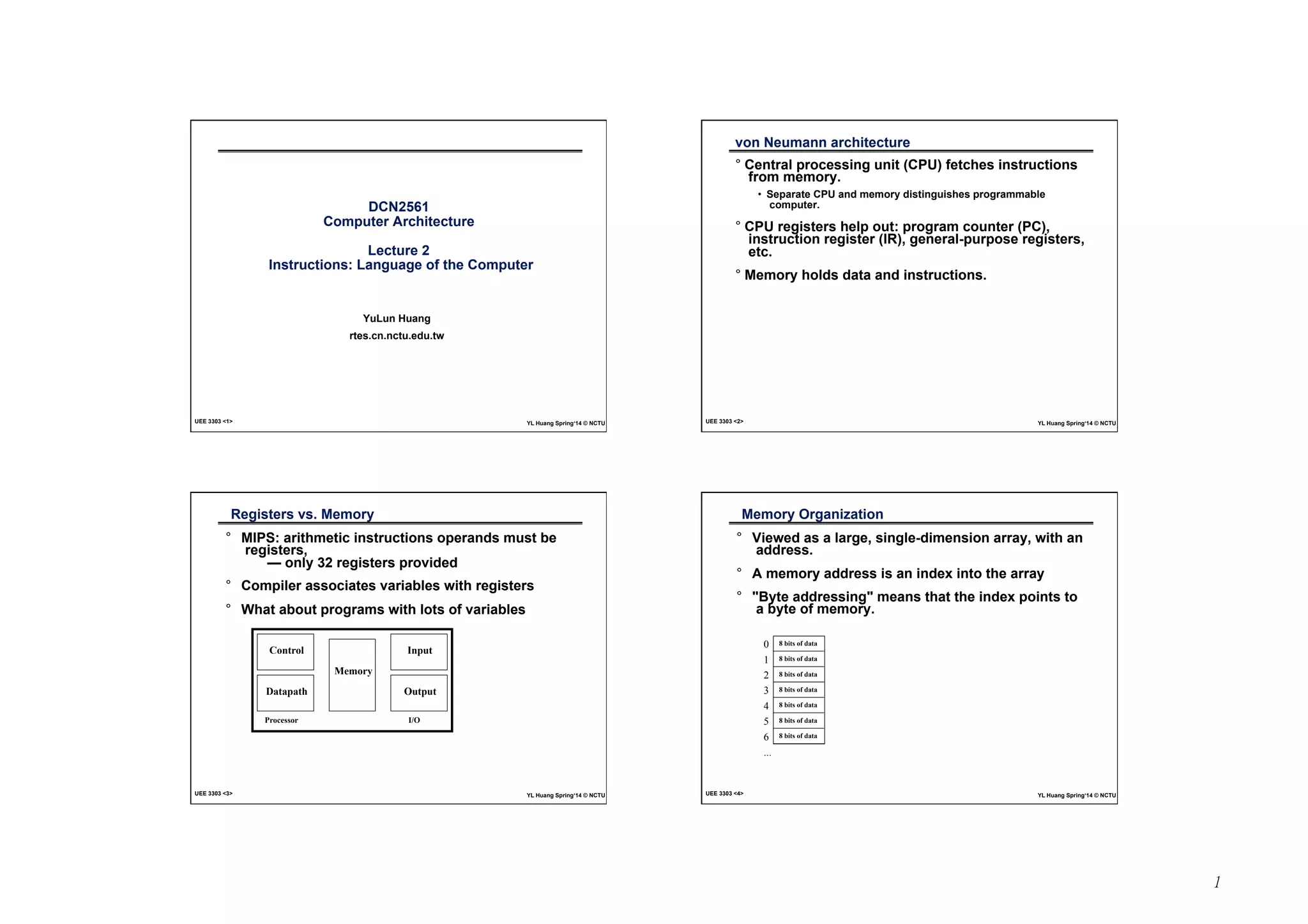

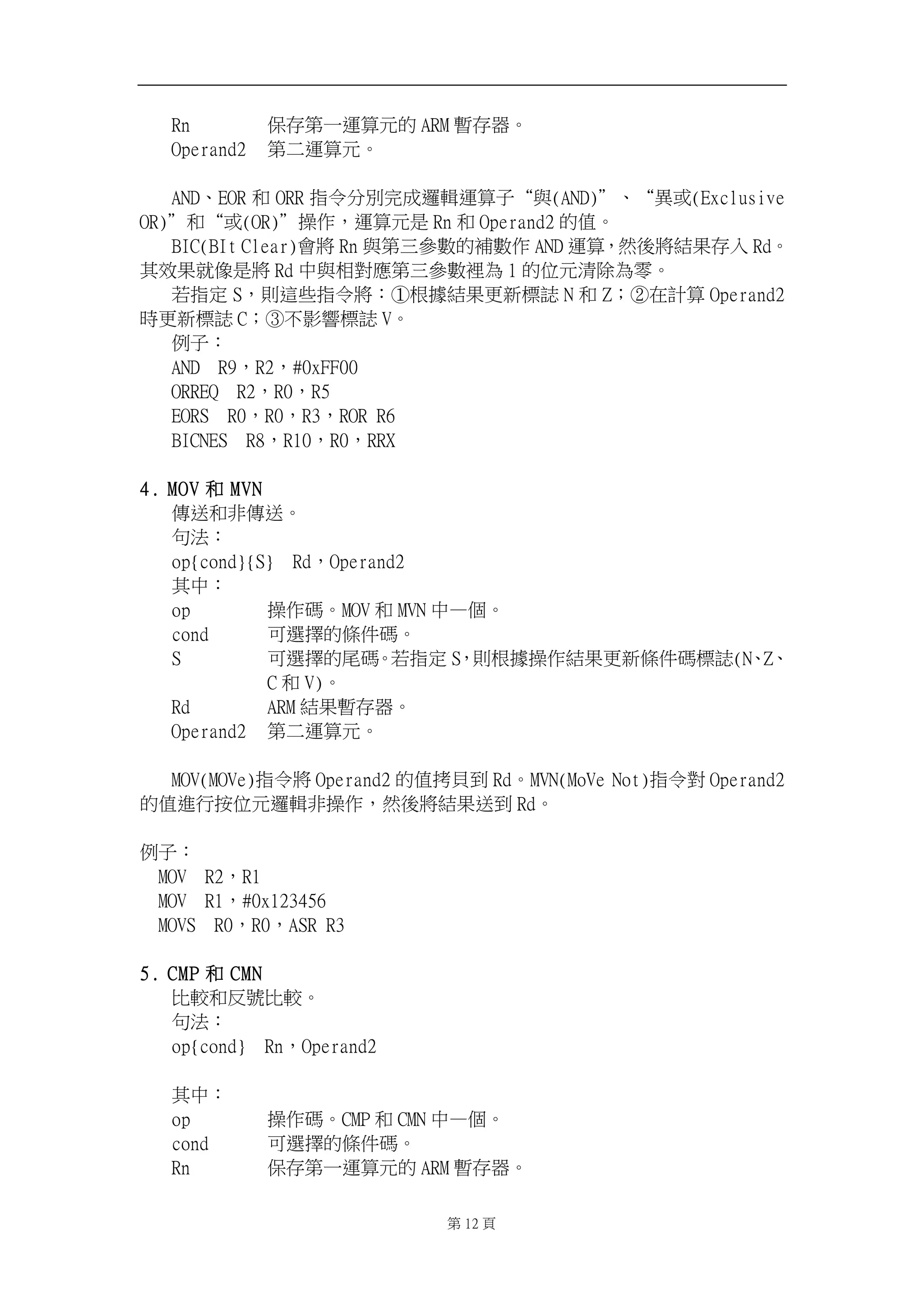

Types of ARM InstructionsĎ

° Arithmetic operations

° Comparisons (no results - just set condition codes)

° Logical operations

° Data movement between registersĎ

UEE 3303 <25> YL Huang Spring ‘14 © NCTU

Arithmetic OperationsĎ

° Syntax

• <Operation>{<cond>}{S} Rd, Rn, Operand2

° Operations are

• ADD operand1 + operand2

• ADC operand1 + operand2 + carry

• SUB operand1 - operand2

• SBC operand1 - operand2 + carry -1

° Examples

ADD r0, r1, r2

SUBGT r3, r3, #1

UEE 3303 <26> YL Huang Spring ‘14 © NCTU

ComparisonsĎ

° The only effect of the comparisons is to

• UPDATE THE CONDITION FLAGS. (no need to set S bit.)

° Syntax:

• <Operation>{<cond>} Rn, Operand2

° Operations are:

• CMP operand1 - operand2, but result not written

• CMN operand1 + operand2, but result not written

• TST operand1 AND operand2, but result not written

• TEQ operand1 EOR operand2, but result not written

° Examples:

CMP r0, r1

TSTEQ r2, #5Ď

UEE 3303 <27> YL Huang Spring ‘14 © NCTU

Logical OperationsĎ

° Syntax:

• <Operation>{<cond>}{S} Rd, Rn, Operand2

° Operations are:

• AND operand1 AND operand2

• EOR operand1 EOR operand2

• ORR operand1 OR operand2

• BIC operand1 AND NOT operand2 [ie bit clear]

° Examples

AND r0, r1, r2

BICEQ r2, r3, #7

EORS r1,r3,r0Ď

UEE 3303 <28> YL Huang Spring ‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-14-2048.jpg)

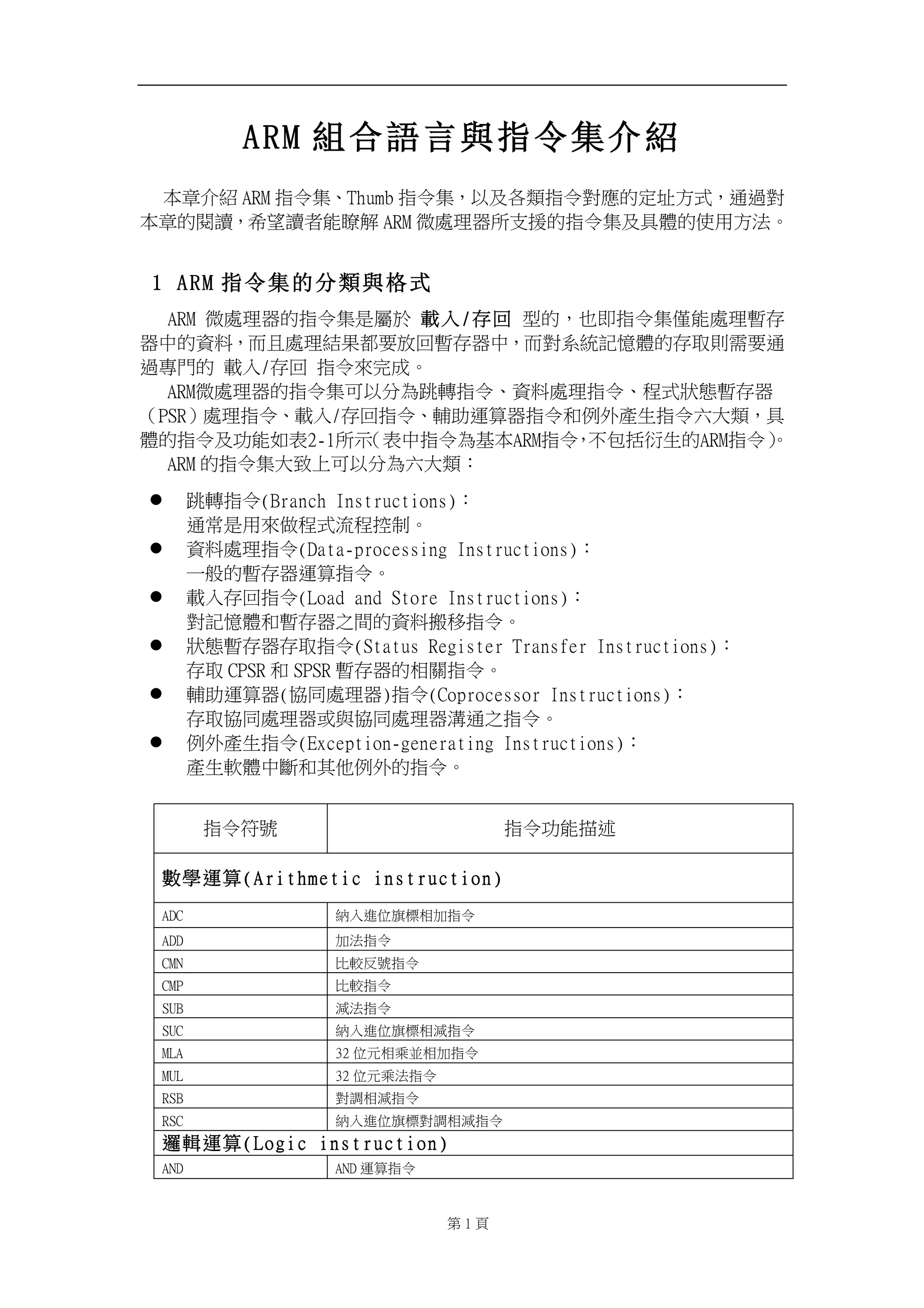

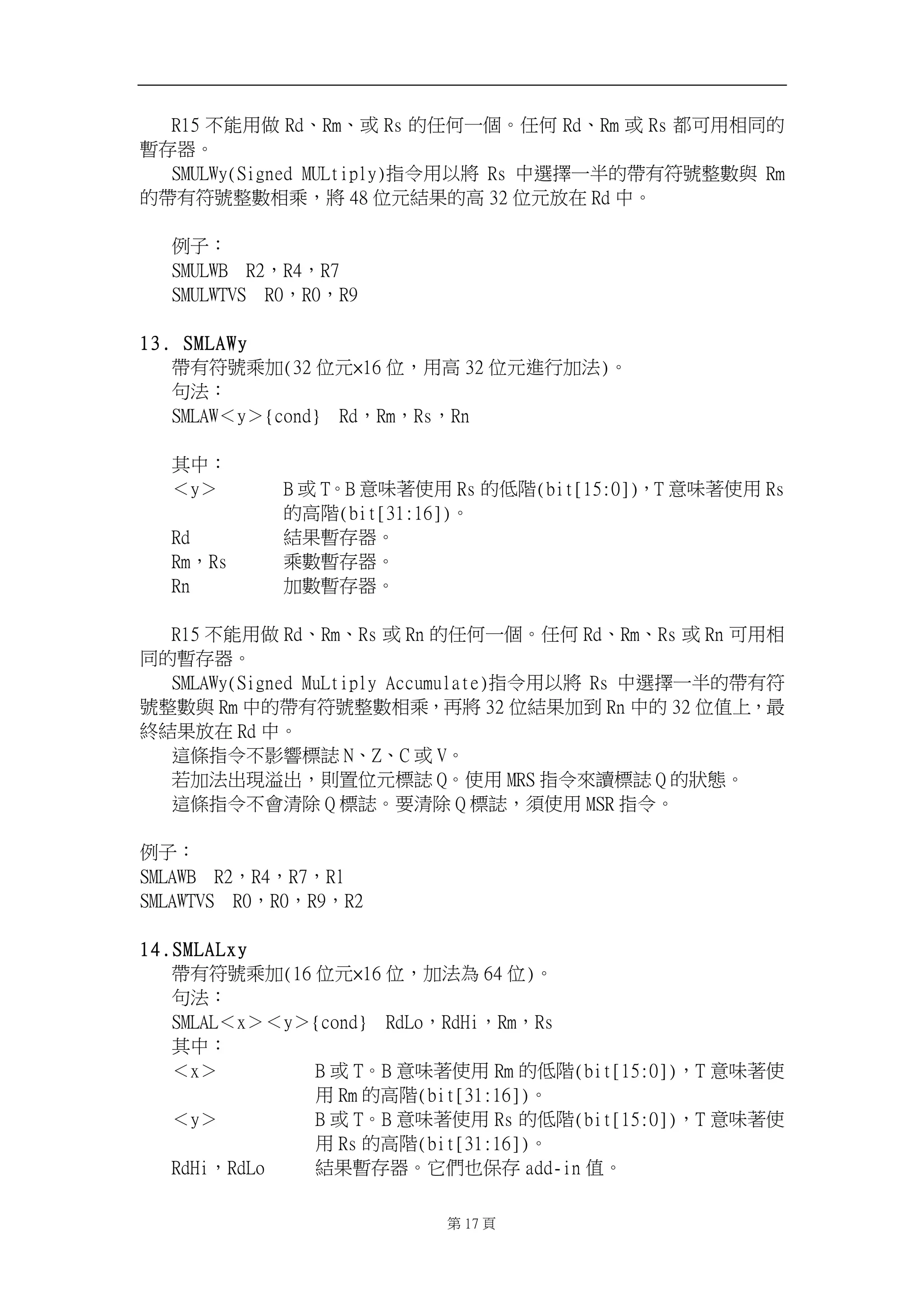

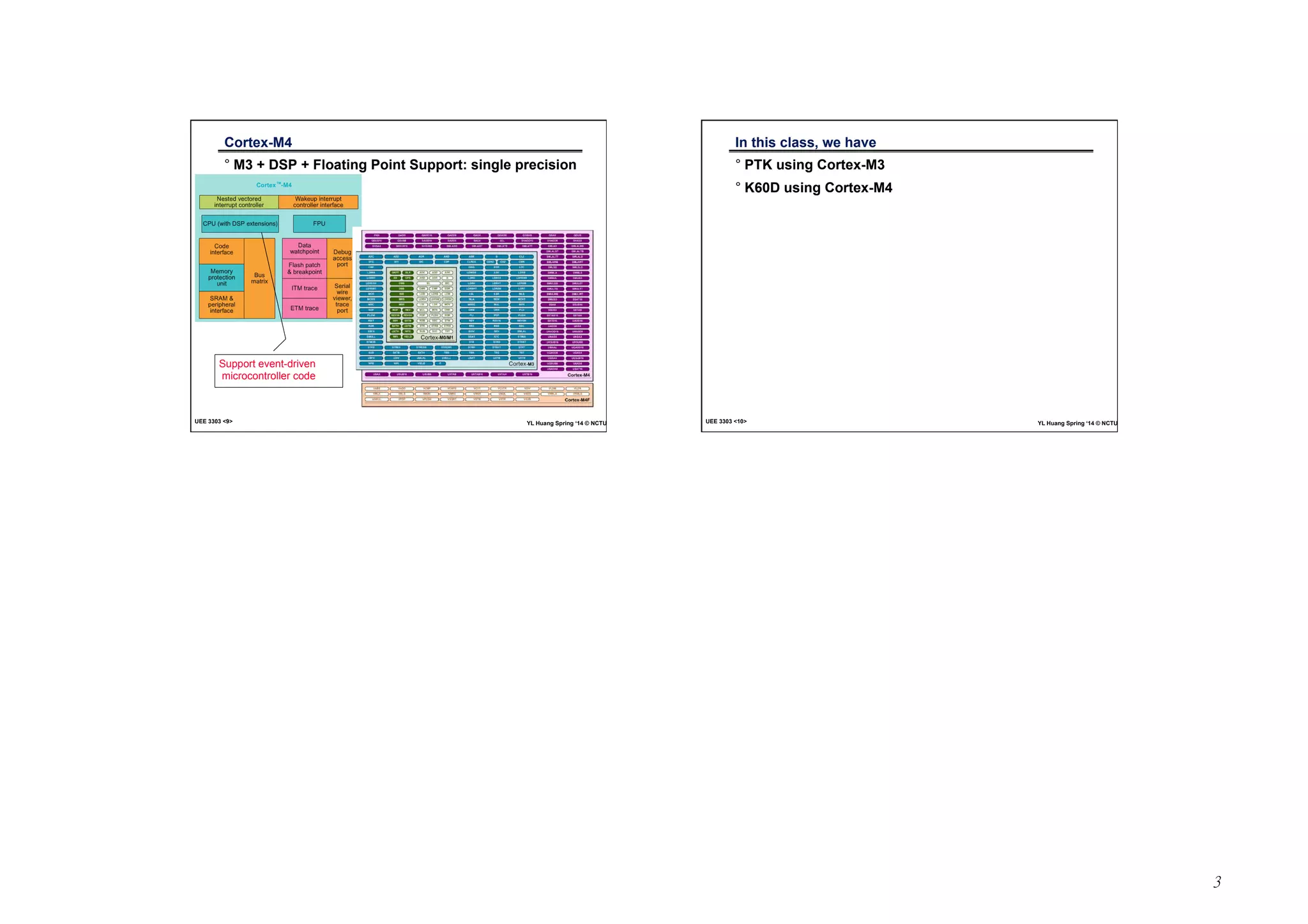

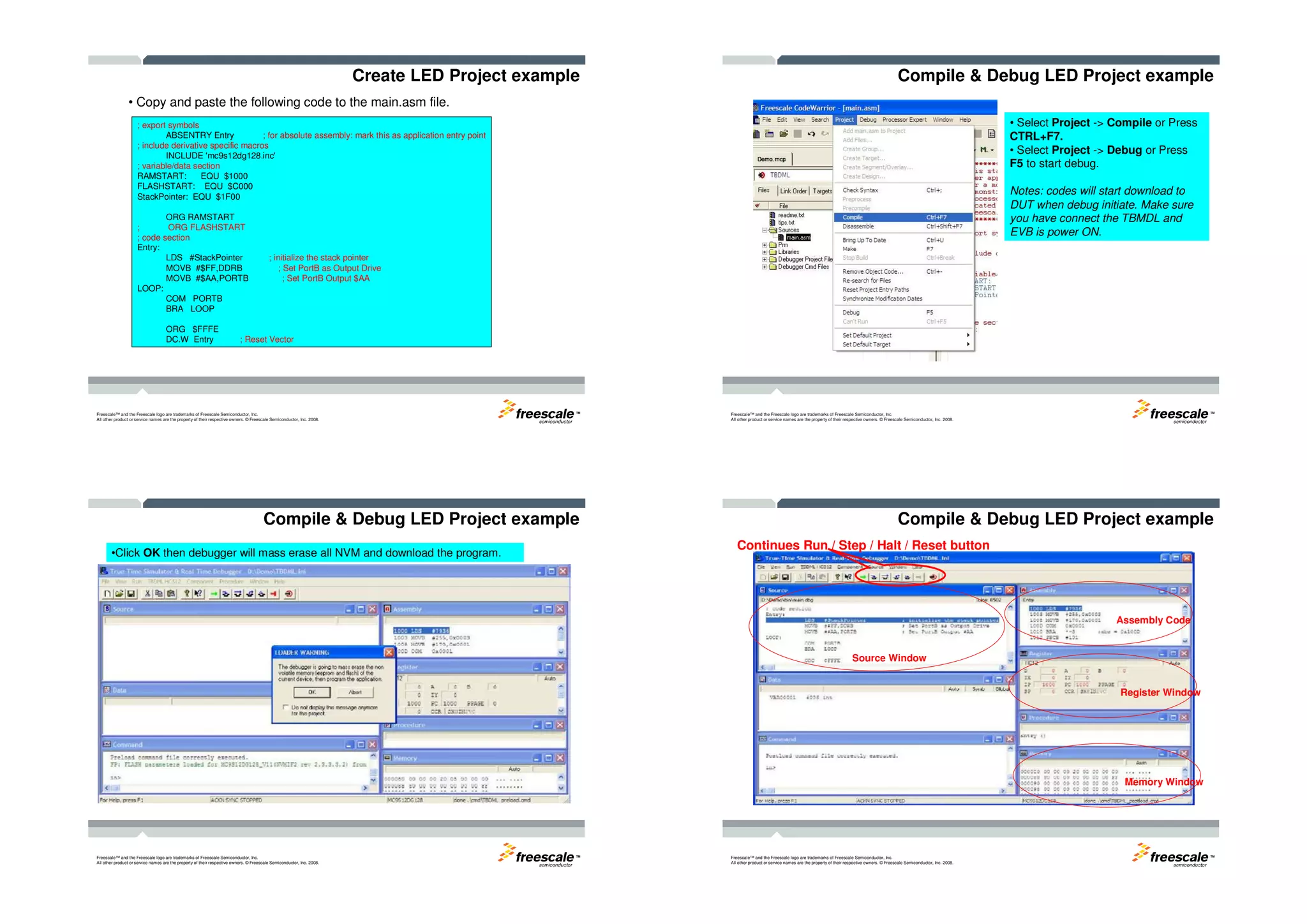

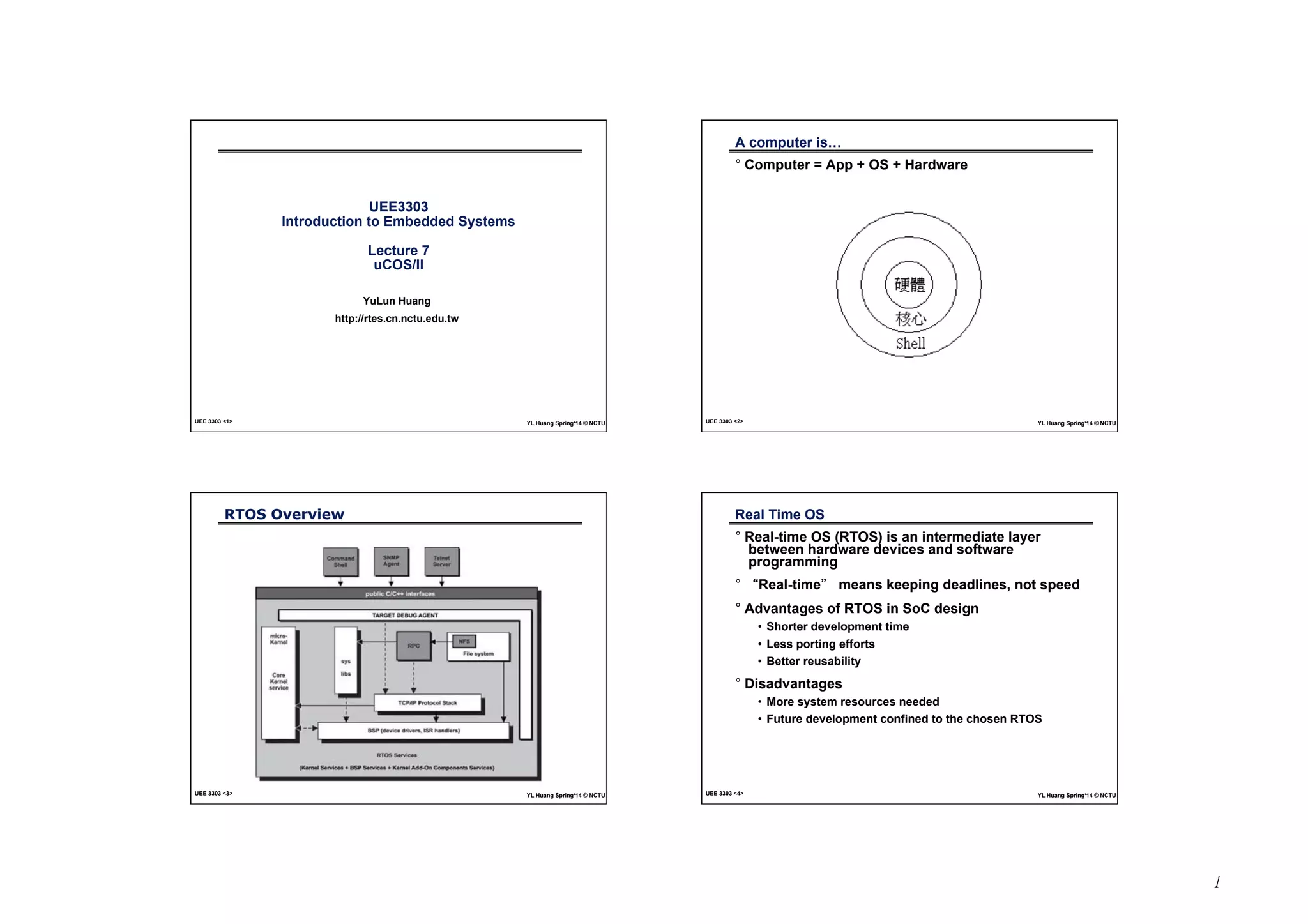

![10

Our QEMU supports..Ď

codeĎ targetĎ codeĎ targetĎ

syborgĎ Symbian Virtual

PlatformĎ

borzoiĎ PDA, PXA270Ď

musicpalĎ Marvell 88w8618Ď terrierĎ PDA, PXA270Ď

mainstoneĎ PXA27xĎ connexĎ Gumstix PXA255Ď

N800, n810Ď Nokia N800/N810 tabletĎ verdexĎ Gumstix PXA270Ď

cheetahĎ Palm TungstenĎ lm3s811evbĎ StellarisĎ

sx1Ď Siemens SX1 v2Ď lm3s6965evbĎ StellarisĎ

sx1-v1Ď Siemens SX1 v1Ď realview-ebĎ ARM926Ď

tosaĎ PDA, PXA255Ď realview-eb-mpcore

Ď

ARM11Ď

akitaĎ PDA, PXA270Ď realview-pb-a8Ď Cortex-A8Ď

spitzĎ PDA, PXA270Ď versatilepbĎ …Ď

UEE 3303 <37> YL Huang Spring ‘14 © NCTU

忚ℍġqemu ᷳ⼴Ď

° ⛐➟埴ġQEMU ⼴炻㚫↢䎦ˬ(qemu)˭ġ䘬㍸䣢ˤ⛐忁ᾳ㍸䣢ᶳ⎗ẍ廠ℍ

ᶨṃ㊯ẌἮ㑵ἄġQEMUˤ

° QEMU ㊯Ẍ

• help ㆾġ? [cmd]: 栗䣢婒㖶㔯⫿Ď

• info: 栗䣢䲣䴙䉨ンˤἳ烉Ď

• info network - 栗䣢䵚嶗ṳ朊䉨ンĎ

• info block - 栗䣢⃚⬀墅伖䉨ンĎ

• info registers - 栗䣢ġCPU 䘬㙓⬀☐䉨ンĎ

• info history - 栗䣢㬟⎚㊯ẌĎ

• What else?

UEE 3303 <38> YL Huang Spring ‘14 © NCTU

infoĎ

° info version -- show the version of QEMU

° info network -- show the network state

° info chardev -- show the character

devices

° info block -- show the block devices

° info blockstats -- show block device

statistics

° info registers -- show the cpu registers

° info cpus -- show infos for each CPU

° info history -- show the command line

history

° info irq -- show the interrupts statistics (if

available)

° info pic -- show i8259 (PIC) state

° info pci -- show PCI info

° info jit -- show dynamic compiler info

° info kvm -- show KVM information

° info numa -- show NUMA information

° info usb -- show guest USB devices

° info usbhost -- show host USB devices

° info profile -- show profiling information

° info capture -- show capture information

° info snapshots -- show the currently

saved VM snapshots

° info status -- show the current VM status

(running|paused)

° info pcmcia -- show guest PCMCIA

status

° info mice -- show which guest mouse is

receiving events

° info vnc -- show the vnc server status

° info name -- show the current VM name

° info uuid -- show the current VM UUID

° info usernet -- show user network stack

connection states

° info migrate -- show migration status

° info balloon -- show balloon information

° info qtree -- show device tree

° info qdm -- show qdev device model list

° info roms -- show roms

UEE 3303 <39> YL Huang Spring ‘14 © NCTU

忚ℍġqemu ᷳ⼴Ď

° q ㆾġquit:ġ斄攱㧉㒔☐

° eject [-f] device烉徨↢墅伖ˤġ-f 堐䣢⻟⇞徨↢

° change device filename:ġ㚜㎃㉥⍾⺷⨺橼炻⤪庇䡇䇯ㆾ䡇䇯ˤ

° screendump filename: ㇒⍾坊ⷽ䔓朊炻⃚⬀ㆸġPPM ⼙⁷ˤġlog

item1[,...]: ⮯㊯⭂䘬枭䚖ᷳġLOG ⮓ℍġ/tmp/qemu.log ᷕˤ

° savevm filename: ⮯㔜ᾳ㧉㒔☐䉨ン⃚⬀军㨼㟰ᷕ

° loadvm filename: 䓙㨼㟰ᷕ庱ℍ㧉㒔☐䉨ン

° Stop: 㬊㧉㒔

° c ㆾġcont: 两临㧉㒔

° sendkey keys: ⁛復㝸ᾳkey䴎㧉㒔☐ˤἧ䓐ġ- Ἦ忋䳸墯⎰挝ˤ

• ἳ烉``sendkey ctrl-alt-f1”ġ堐䣢⁛復ġ<Ctrl><Alt><F1> 䴎㧉㒔☐ˤ

° system_reset:ġ慵㕘┇≽䲣䴙ˤĎ

UEE 3303 <40> YL Huang Spring ‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-17-2048.jpg)

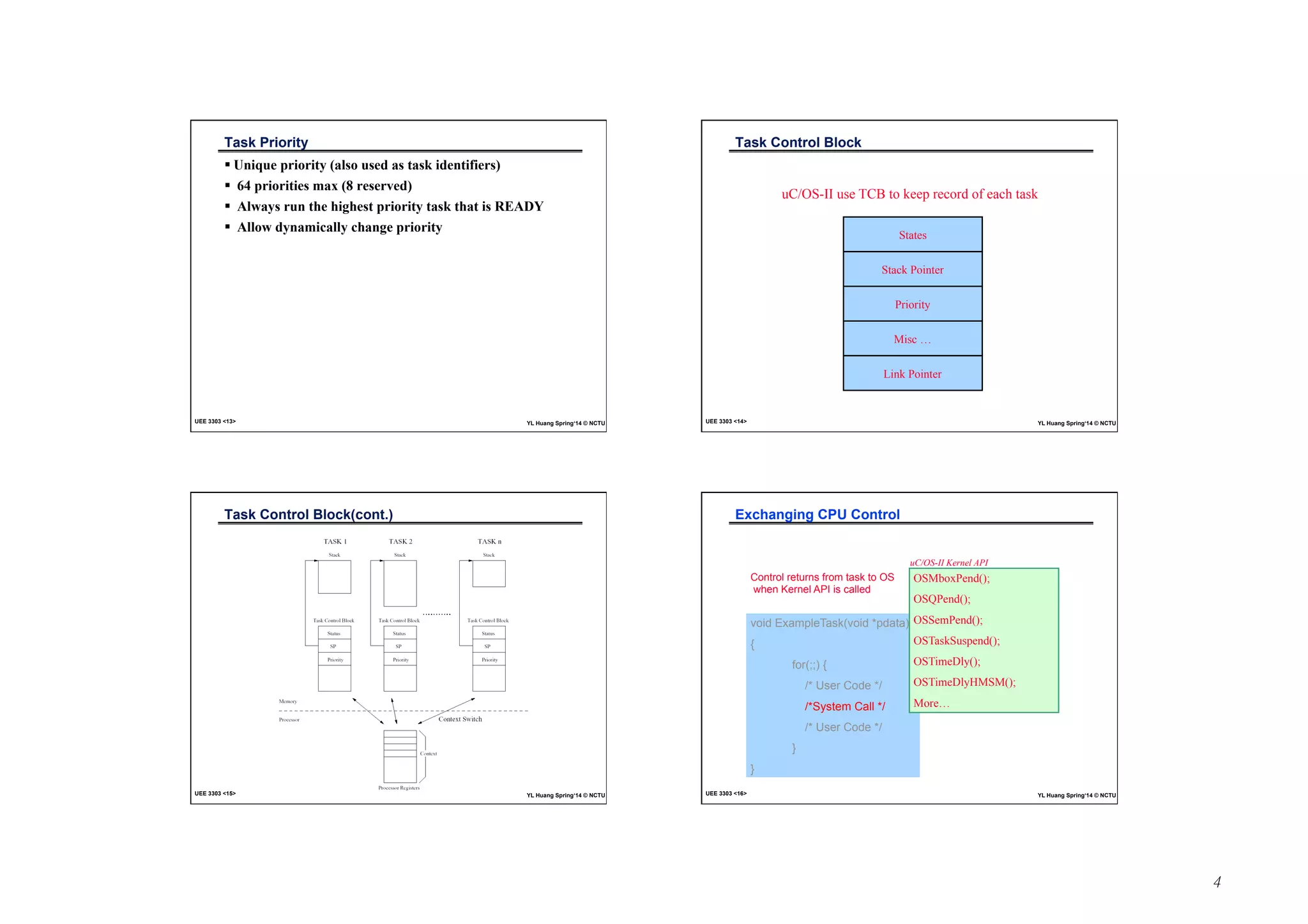

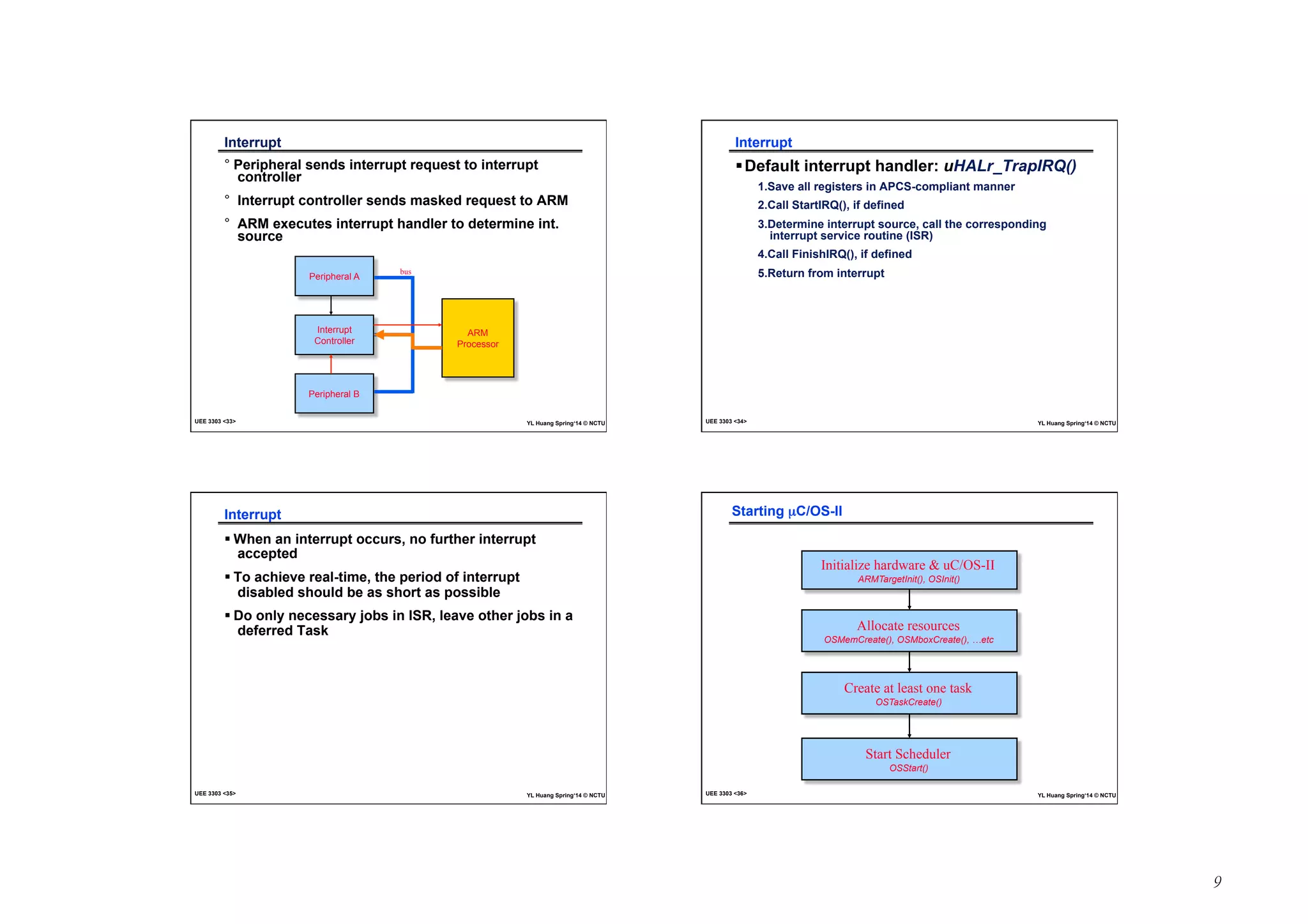

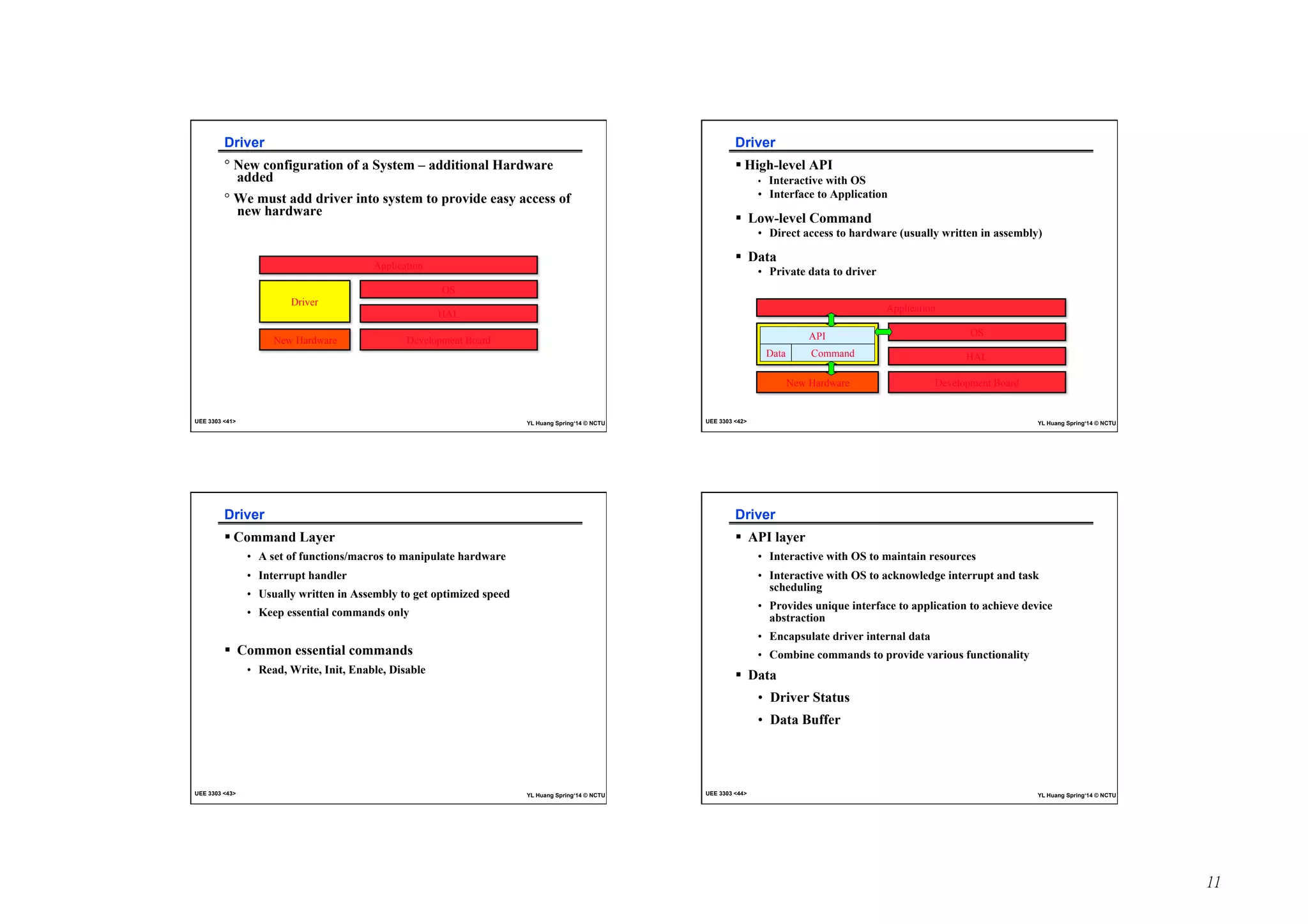

![12

Driver

° Why divide driver into two parts

• Easy to replace underlying hardware

• Unique interface to applications

• Easy to adopt pre-written assembly code

UEE 3303 45 YL Huang Spring‘14 © NCTU

Driver

° API Example

Available commands:

• Read_Byte

• Write_Byte

• Init_Device

• Enable_Device

• Disable_Device

Set_serial_baudrate(int baud)

{

OS_Request_Device();

Disable_Device();

Write_Byte(CONF_BASE, baud);

Enable_Device();

OS_Release_Device();

}

UEE 3303 46 YL Huang Spring‘14 © NCTU

Driver

° API Example

Send_serial(char data[], int len)

{

OS_Request_Device();

for(I=0;Ilen;I++)

Write_Byte(IO_BASE, data[I]);

OS_Release_Device();

}

Available commands:

• Read_Byte

• Write_Byte

• Init_Device

• Enable_Device

• Disable_Device

UEE 3303 47 YL Huang Spring‘14 © NCTU

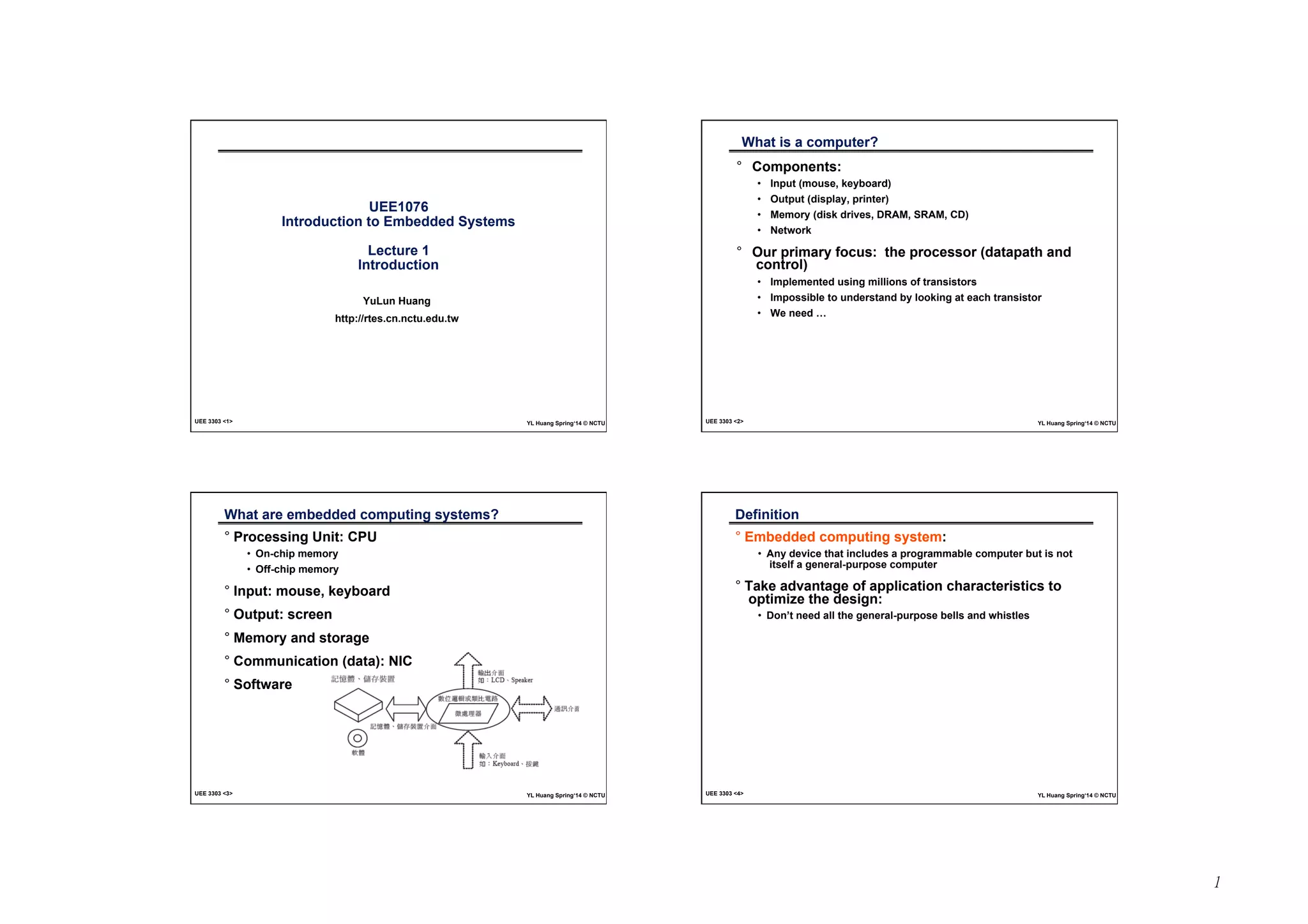

Driver Design Flow

start

Decide I/O interface

(I/O address, I/O method)

Write Assembly code

to control hardware

Pack assembly code

into commands

Write interrupt handler

Write API base on previously

Developed commands

Test Driver

end

Test assembly code

UEE 3303 48 YL Huang Spring‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-76-2048.jpg)

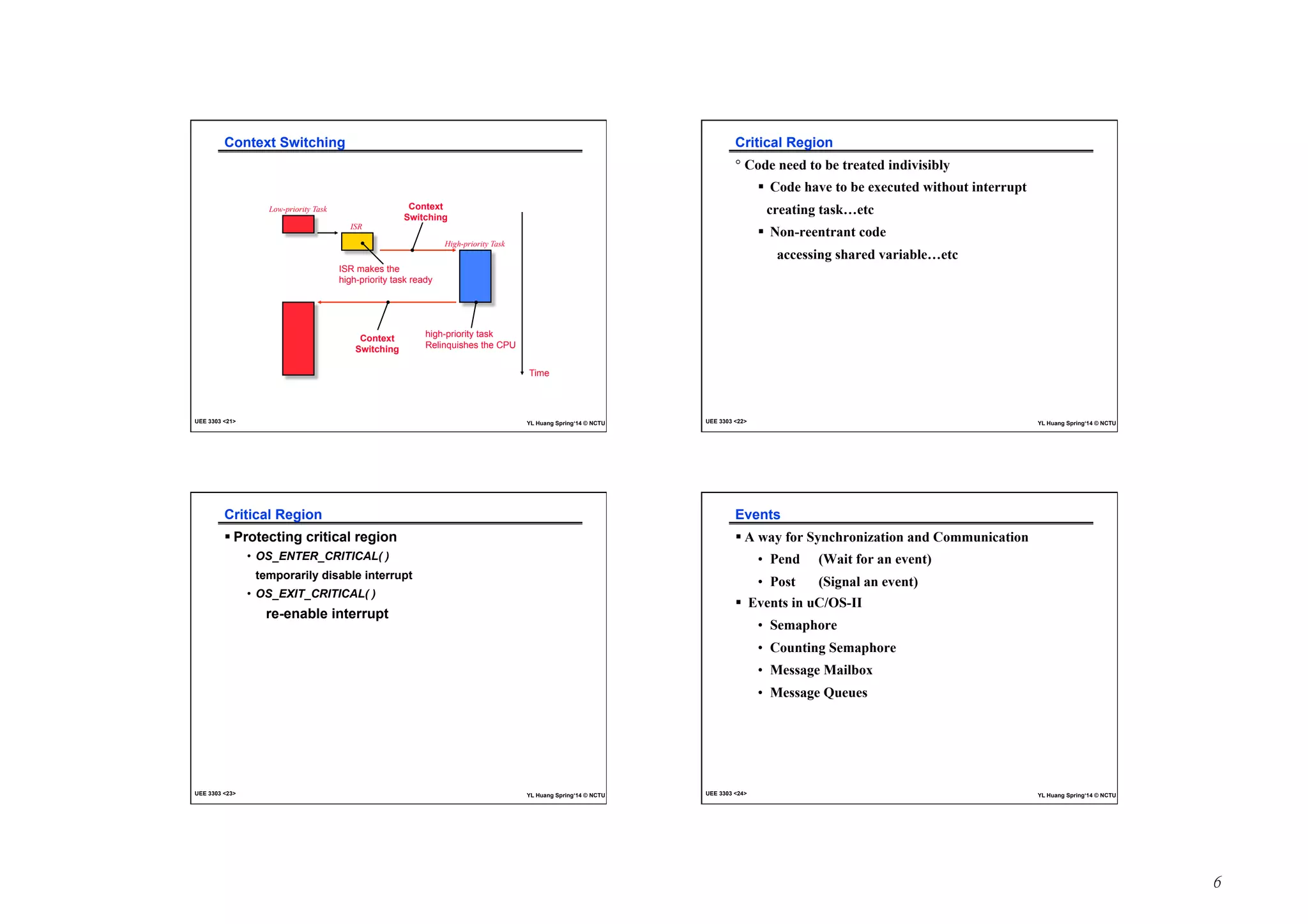

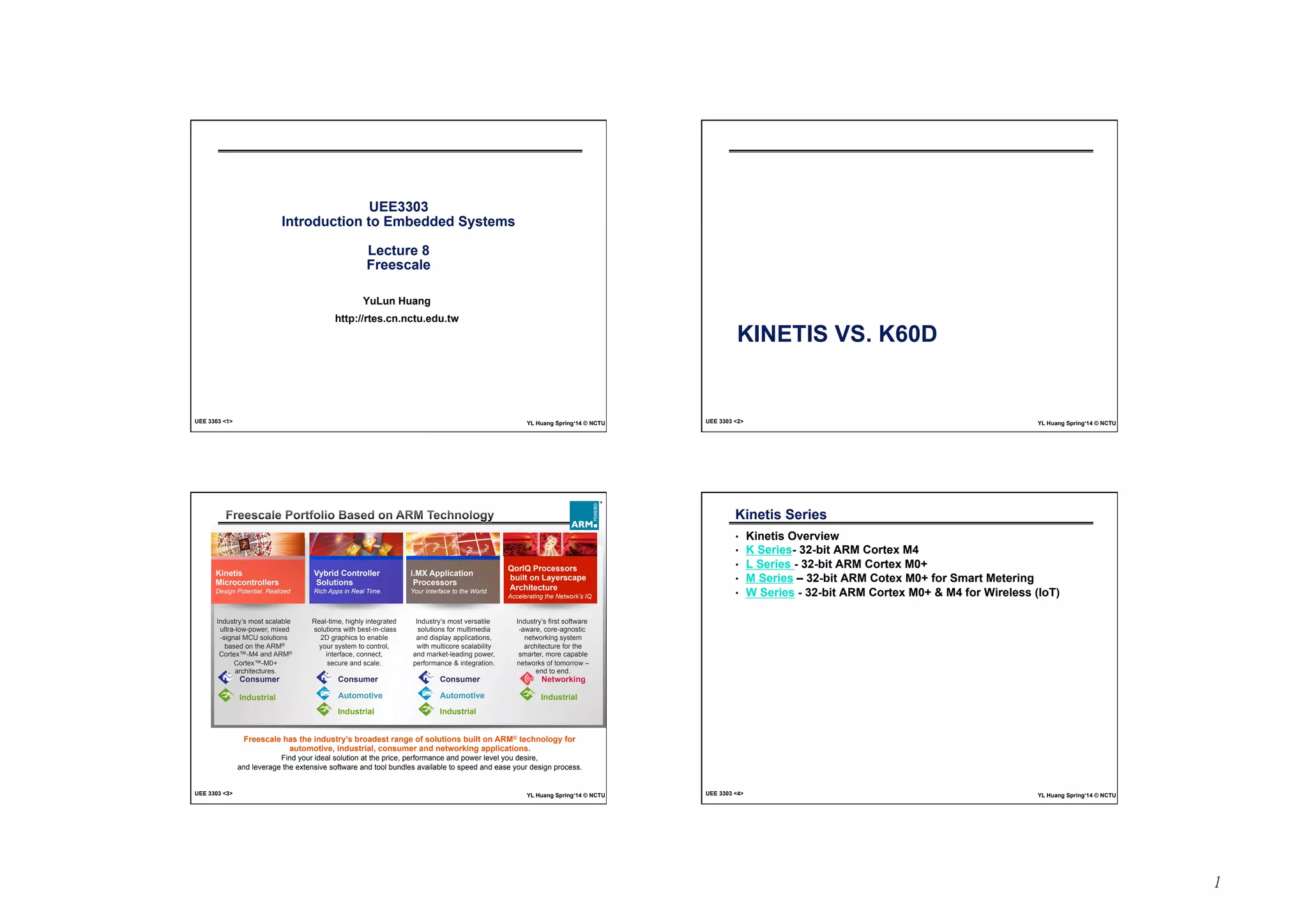

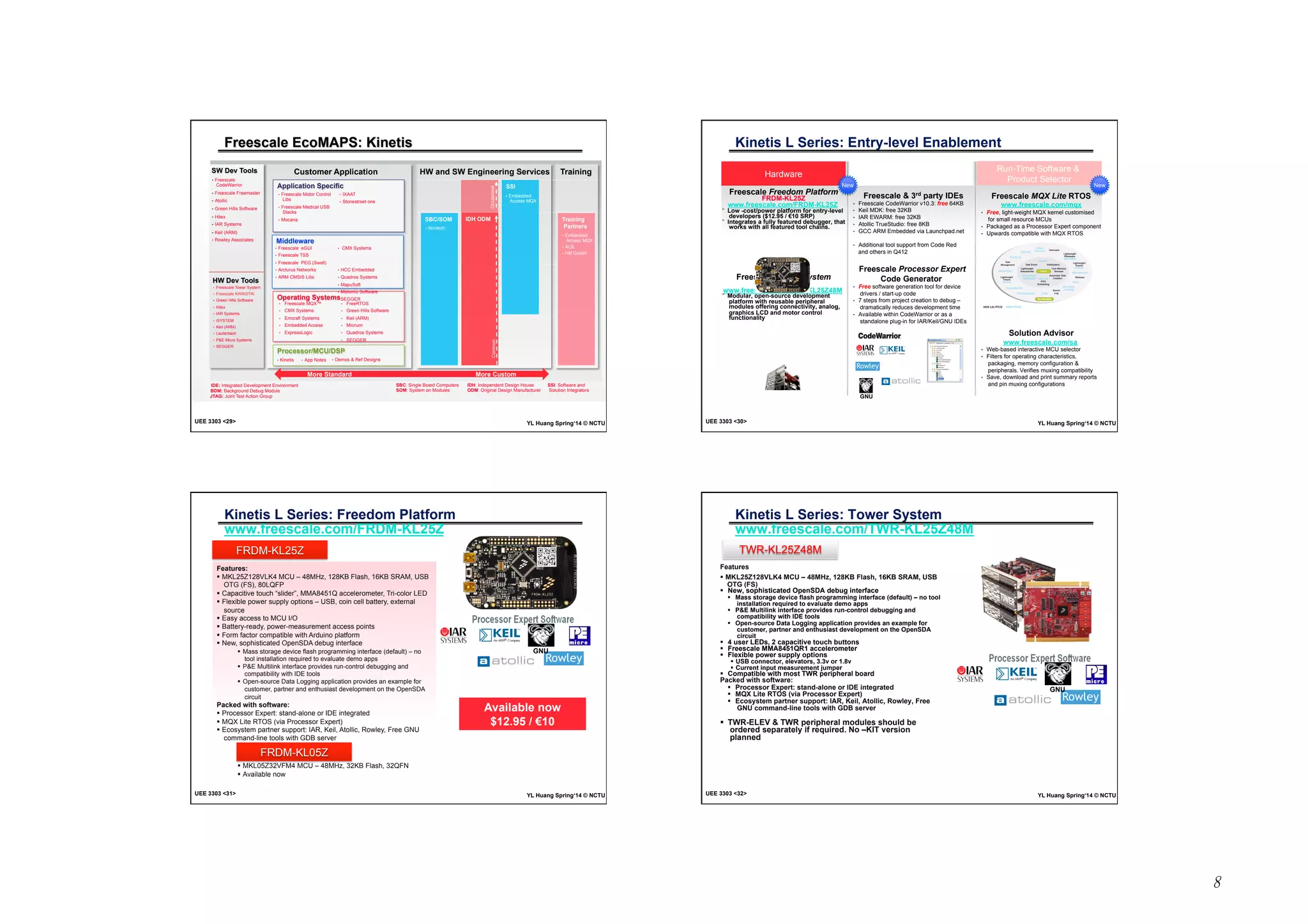

![3

Kinetis K/L Series: Packaging

32QFN

5 x 5 mm

0.5mm pitch

(K10/20)

(KL0/1/2)

Common Packages

Kinetis K Series Package

Kinetis L Series Package

64MAPBGA

5 x 5 mm

0.5mm pitch

(K10/20)

(KL1*/2*/3*/4*)

48LQFP

7 x 7 mm

0.55mm pitch

(K10/20)

(KL0/1*/2*)

64LQFP

10 x 10 mm

0.5mm pitch

(K10/20/30/40/50)

(KL1/2/3/4)

80LQFP

12 x 12 mm

0.5mm pitch

(K10/20/30/40/50)

(KL1/2/3*/4*)

100LQFP

14 x 14 mm

0.5mm pitch

(K10/20/30/40/50/60)

(KL3/4)

Kinetis L Series Only Kinetis K Series Only

90WLCSP

3.9x4.4x0.56 mm

0.4mm pitch

(K10/20*)

144LQFP

20 x 20 mm

0.5mm pitch

(K10/20/30/40/50/60)

48QFN

7 x 7 mm

0.5mm pitch

(K10/20)

(KL0/1*/2*)

110WLCSP

3.9x4.4x0.56 mm

0.4mm pitch

(K10/20*)

144MAPBGA

13 x 13 mm

1.0mm pitch

120WLCSP

5.3x5.3x0.56 mm

0.4mm pitch

(K10/20/60)

(K10/20/30/40/50/60)

121MAPBGA

8 x 8 mm

0.65mm pitch

(K10/20/30/40/50/60)

(KL2/3/4)

143WLCSP

6.5x5.6x0.56 mm

0.4mm pitch

(K61)

256MAPBGA

17 x 17 mm

1.0mm pitch

(K60/70)

35WLCSP

2.55x3x0.56 mm

0.4mm pitch

(KL1*/2*)

32LQFP

7 x 7 mm

0.8mm pitch

(KL0)

25WLCSP

2.3x2.3x0.56 mm

0.4mm pitch

(KL0*)

20WLCSP

2x2x0.56 mm

0.4mm pitch

(KL0)

24QFN

4 x4x1 mm

0.5mm pitch

(KL0x)

16QFN

3x3x1 mm

0.5mm pitch

(KL02)

UEE 3303 9 YL Huang Spring‘14 © NCTU

*proposed

(Development Tools)

ENABLEMENT OVERVIEW

UEE 3303 10 YL Huang Spring‘14 © NCTU

Kinetis Tower System: Reusable, modular development platform

www.freescale.com/tower www.towergeeks/org

MCU Families

Supported

TWR Part

Number Contents Price

(SRP)

K20

TWR-K20D50M 64 LQFP MCU module. USB communication supported

without TWR-SER (recommended for UART) $99

TWR-K20D72M 100 LQFP MCU module. USB communication

supported without TWR-SER $119

TWR-K21D50M 81 MAPBGA MCU module. Hardware security features

supported. $119

K30/40

TWR-K40X256

TWR-K40D100M

TWR-K40X256 Rev 1.0 (144MBGA), TWRPI-SLCD

TWR-K40D100M Rev 2.0 Silicon (144MBGA) $69

TWR-K40X256-KIT TWR-K40X256 (144MBGA), TWRPI-SLCD

TWR-SER, TWR-ELEV $139

K50

TWR-K53N512 TWR-K53N512 (144MBGA), TWRPI-SLCD $109

TWR-K53N512-KIT TWR-K53N512 (144MBGA), TWRPI-SLCD,

TWR-SER, TWR-ELEV $179

K10/20/60

TWR-K60N512

TWR-K60D100M

TWR-K60N512 Rev 1.0 Silicon (144MBGA)

TWR-K60D100M Rev 2.0 Silicon (144MBGA)

TWR-K60N512-KIT TWR-K60N512 (144MBGA), TWR-SER, TWR-ELEV $139

TWR-K60N512-IAR TWR-K60N512-KIT (144MBGA),

TWR-PROTO, Segger J-Link Lite Debug Probe, IAR

EWARM IDE (eval. version)

NEW

TWR-K60N512-KEIL TWR-K60N512-KIT (144MBGA),

UNLINK-ME Debug Probe,

KEIL MDK IDE (eval. version)

• IDEs: FSL CodeWarrior, IAR Embedded Workbench, Keil MDK,

• Freescale MQX RTOS

• OSJTAG Debug circuitry – program debug with USB cable

$69

$99

$239

$199

TWR-SENSOR

-PAK

TWR-LCD

TWR-WIFI-RS2101

• Low power touch sensing plug-in socket for expansion:

Sensors, Radio, etc…

• Fully compatible with all Tower peripheral modules UEE 3303 12 YL Huang Spring‘14 © NCTU

UEE 3303 11 YL Huang Spring‘14 © NCTU

Kinetis IDE Support

Availability

1. Freescale (CodeWarrior 10.1) [available now]

- Includes MQX Task Aware Debug plug-in option

- MCU v10.4 [available now]

2. IAR (Embedded Workbench) [available now]

- EWARM: Supports all ARM7/9 and all Cortex Devices

- EWARM-BaseLine (BL): All the features of EWARM but is limited in code space up to 256KB

- EWARM-CM: Supports any Cortex-M series devices including (M4)

- EWARM-CM-FSL: Supports any Kinetis Cortex-M4 series device

– Will be re-sold via FSL Buy Direct program only. $2500 for 1 year license

– Includes MQX Task Aware Debug plug-in option

– http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=EWARM-CM-FSLfsrch=1sr=2

3. Keil (MDK) [available now]

- MQX Task Aware Debug plug-in planned .

4. Greenhills (MULTI) [available now]

5. CodeSourcery (Sourcery G++) [available now]

- MQX Task Aware Debug plug-in planned.](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-79-2048.jpg)

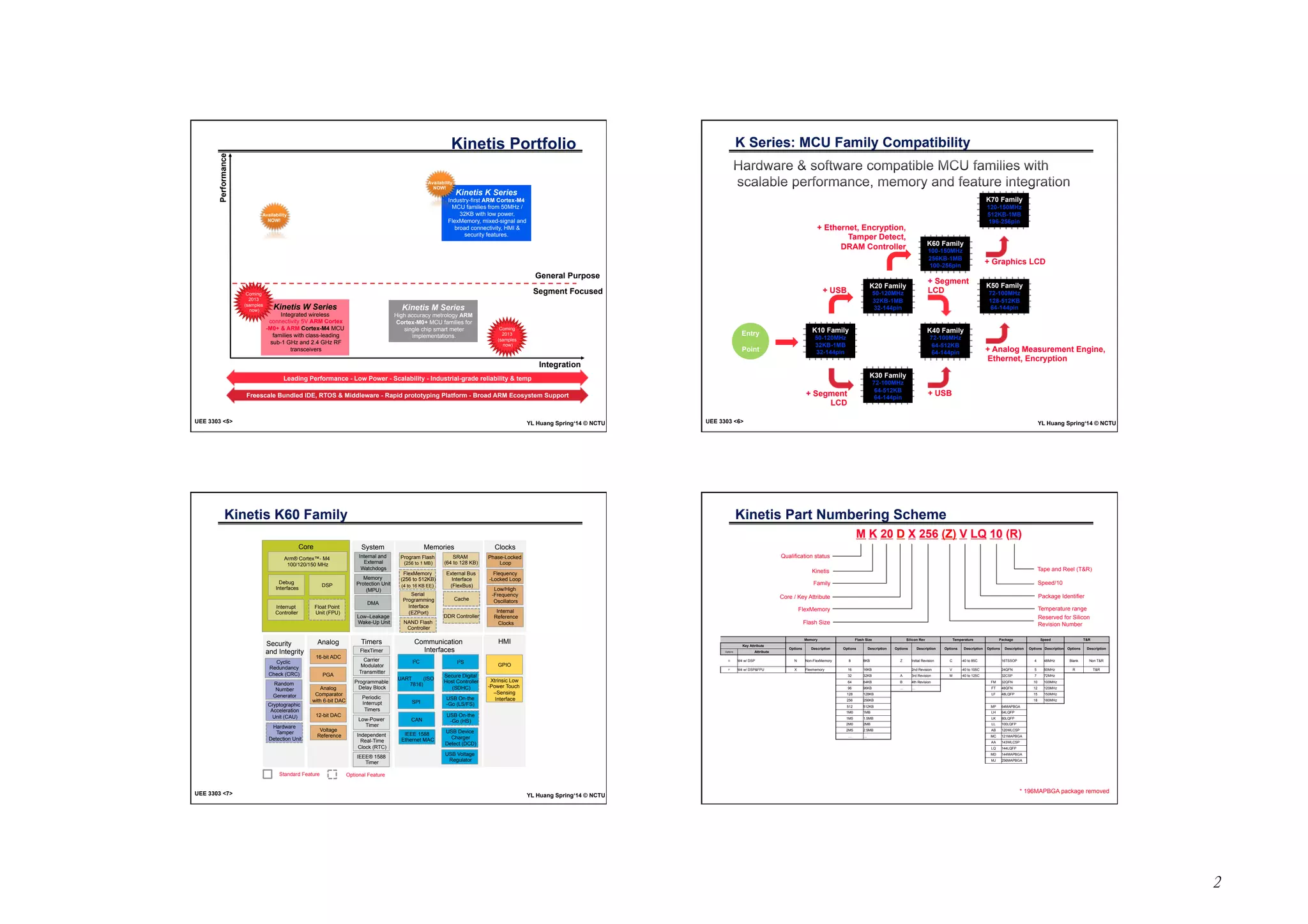

![6

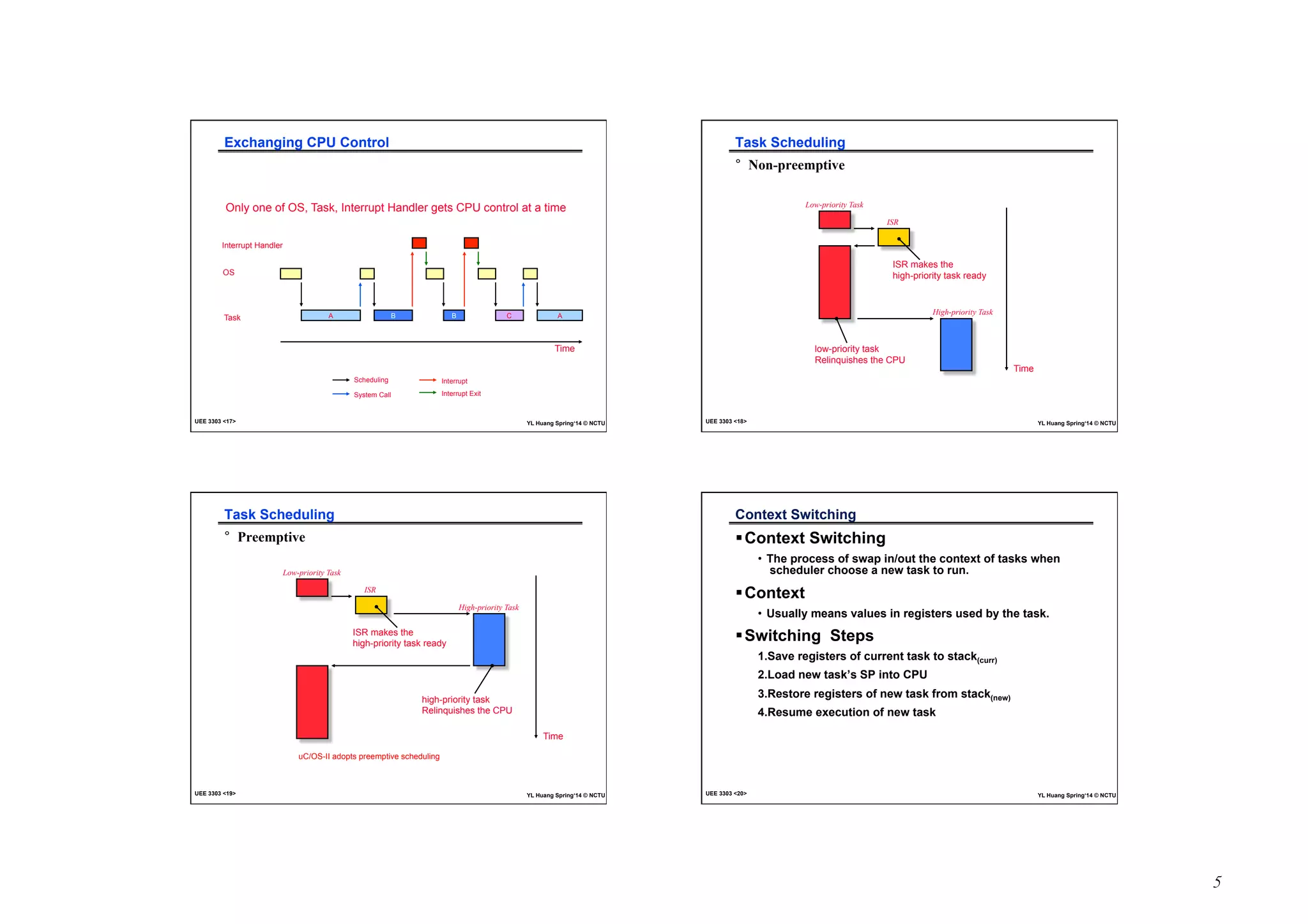

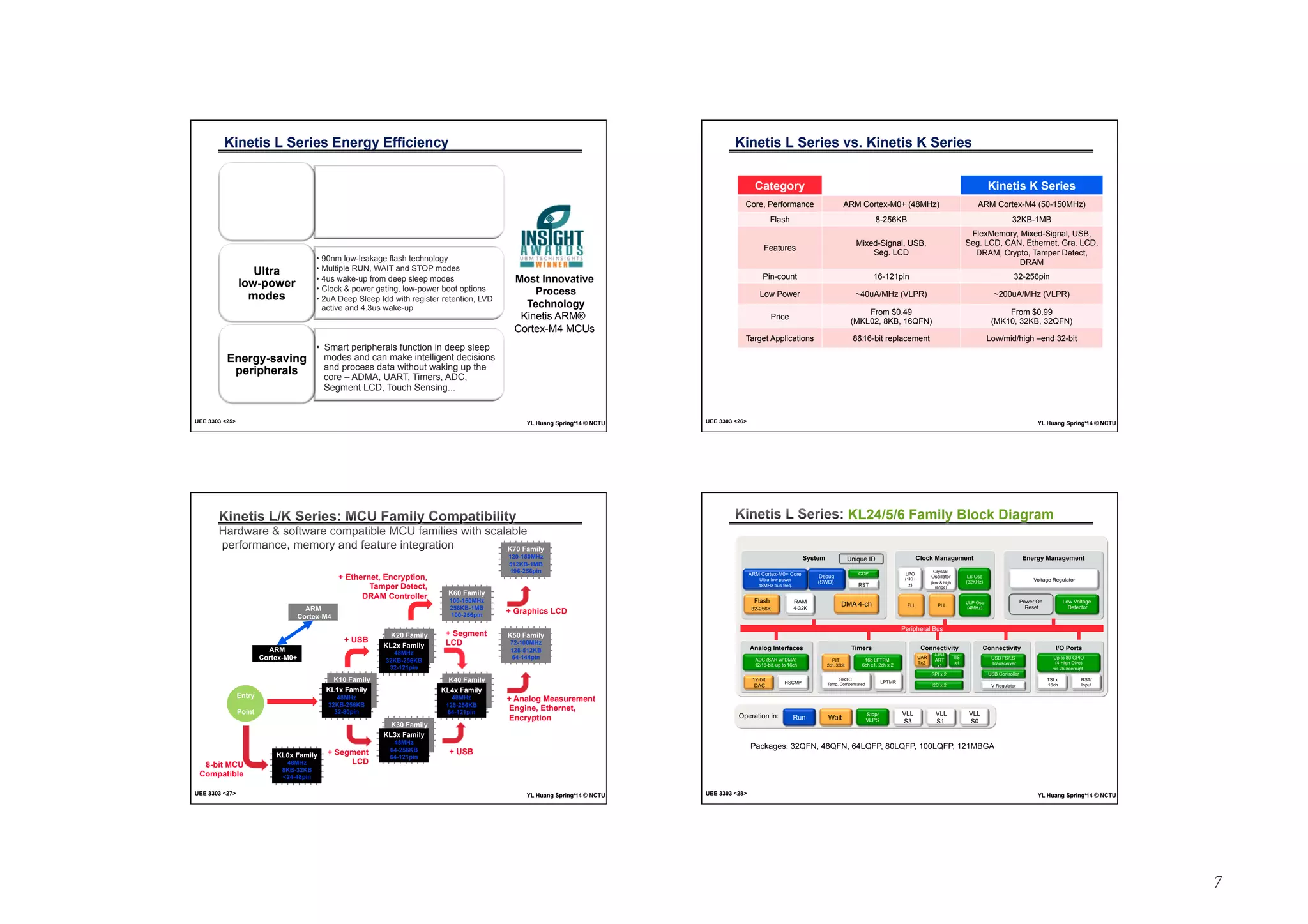

Moving from 8/16-bit to 32-bit ARM Cortex-M0+

Benefits

• Linear 4GB address space

• Full-featured interrupt

controller

• Huge scalability

• Huge ARM ecosystem

• Micro Trace Buffer

• 12-35kgates (similar to

8/16bit)

• Excellent code density

• 2x to 40x more than 8/16-

bit, 9% more than Cortex-

M0

• Fast 32-bit math

processing

• Fast single-cycle access

to I/O

• 2x CoreMark/mA than

closest 8/16-bit MCU,

+30% / CM0

Performance Ease-of-

Development

Energy- Low Cost

Efficiency

UEE 3303 21 YL Huang Spring‘14 © NCTU

K

L

M

W

E

X

Kinetis L Series:

Reduce cycles for optimized power efficiency

! Supported operations

• Decorated Stores

• Logical AND, OR, XOR

• Bit field insert (BFI)

! Supported operations

• Load-and-Clear 1 bit (LAC1)

• Load-and-Set 1 bit (LAS1)

• Unsigned Bit Field Extract (UBFX)

Task Normal C Code Size BME Code Size Improvement

Logical XOR operation 12Bytes 6Bytes 50%

Bit Field Insert 24Bytes 6Bytes 75%

GPIOA_PDOR ^= 0x02; // Logical XOR

0000005E 0x.... LDR R0,?

?DataTable6_5 ;; 0x400ff000

00000060 0x6800 LDR R0,[R0, #+0]

00000062 0x2102 MOVS R1,#+2

00000064 0x4041 EORS R1,R1,R0

00000066 0x.... LDR R0,?

?DataTable6_5 ;; 0x400ff000

00000068 0x6001 STR R1,[R0, #+0]

Uses 12 Bytes

// Macro used to generate hardcoded XOR address

#define BME_XOR_ADDR(ADDR) (*(volatile uint32_t *

)(((uint32_t)ADDR) | (326)))

BME_XOR_ADDR(GPIOA_PDOR) = 0x02;

00000014 0x.... LDR R0,??DataTable6_6 ;;

0x4c0ff000

00000016 0x2102 MOVS R1,#+2

00000018 0x6001 STR R1,[R0, #+0]

Uses 6 Bytes

UEE 3303 22 YL Huang Spring‘14 © NCTU

ARM Cortex-M0+ Processor:

Fast I/O Port

ARM Cortex-M0+ Fast IO Port

! Single access Processor

! Most suited to critical GPIO

and Peripherals

Advantages for the application

! Higher GPIO toggling frequency

! Bit-bang the I/O as on a 8-bit

! Save precious cycles, e.g. set

faster peripherals for low

-power

! “Harvard-like”: access GPIO

/Peripheral while processor

fetch the next instruction

UEE 3303 23 YL Huang Spring‘14 © NCTU

ARM Cortex-M0+ Processor:

A faster route to a bug free application

ARM Micro Trace Buffer (MTB)

! Lightweight Trace

! Trace stored in RAM

! Non intrusive

! Read over Serial Wire /JTAG

Freescale extensions:

! Additional address (and optionally

data) watch points

! Define specific memory references

were the trace start and stop

AHB

MTB Controller

RAM

I/F

store trace

information

SRAM

Appl.Data

+

Trace Data

read trace

information

UEE 3303 24 YL Huang Spring‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-82-2048.jpg)

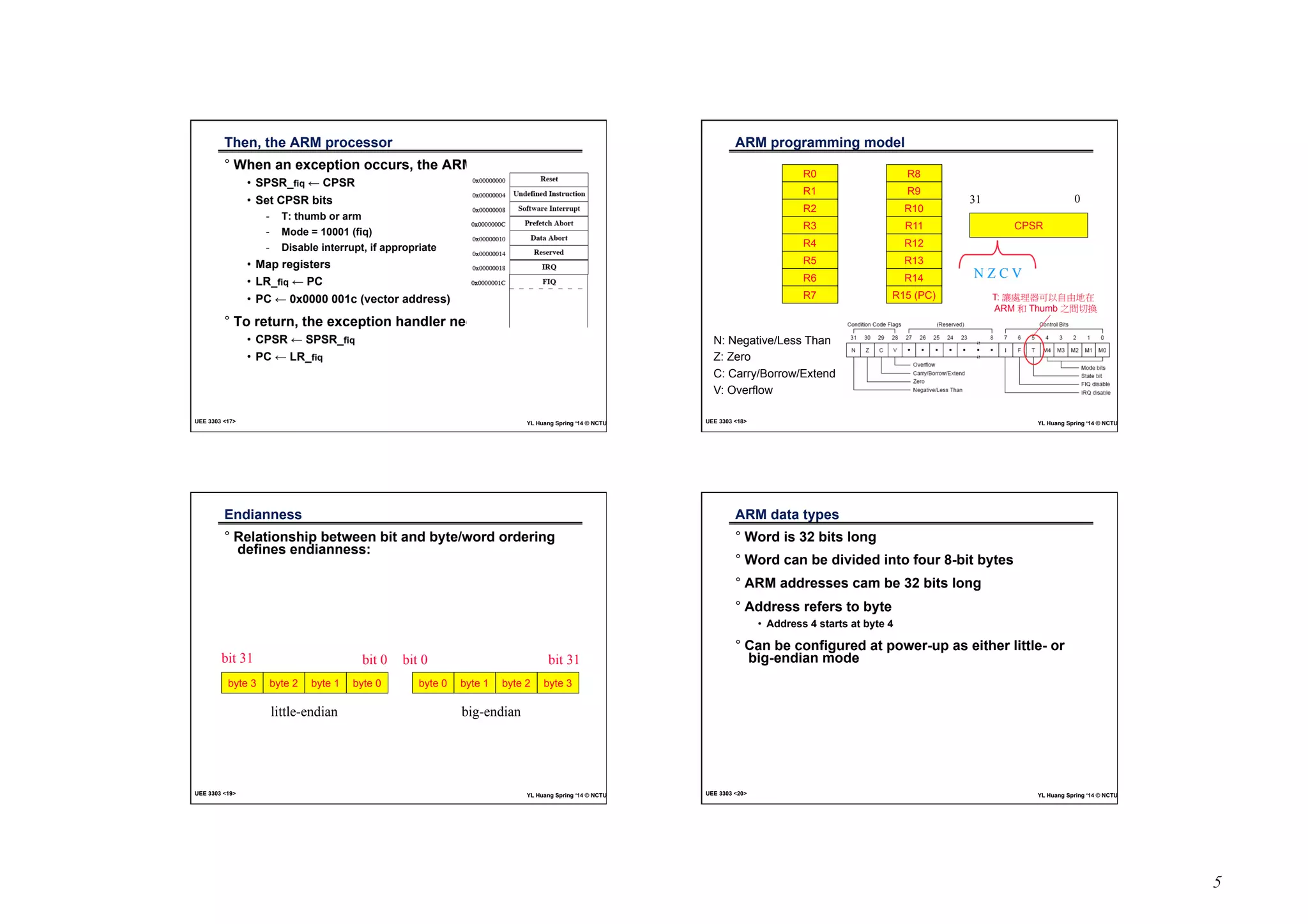

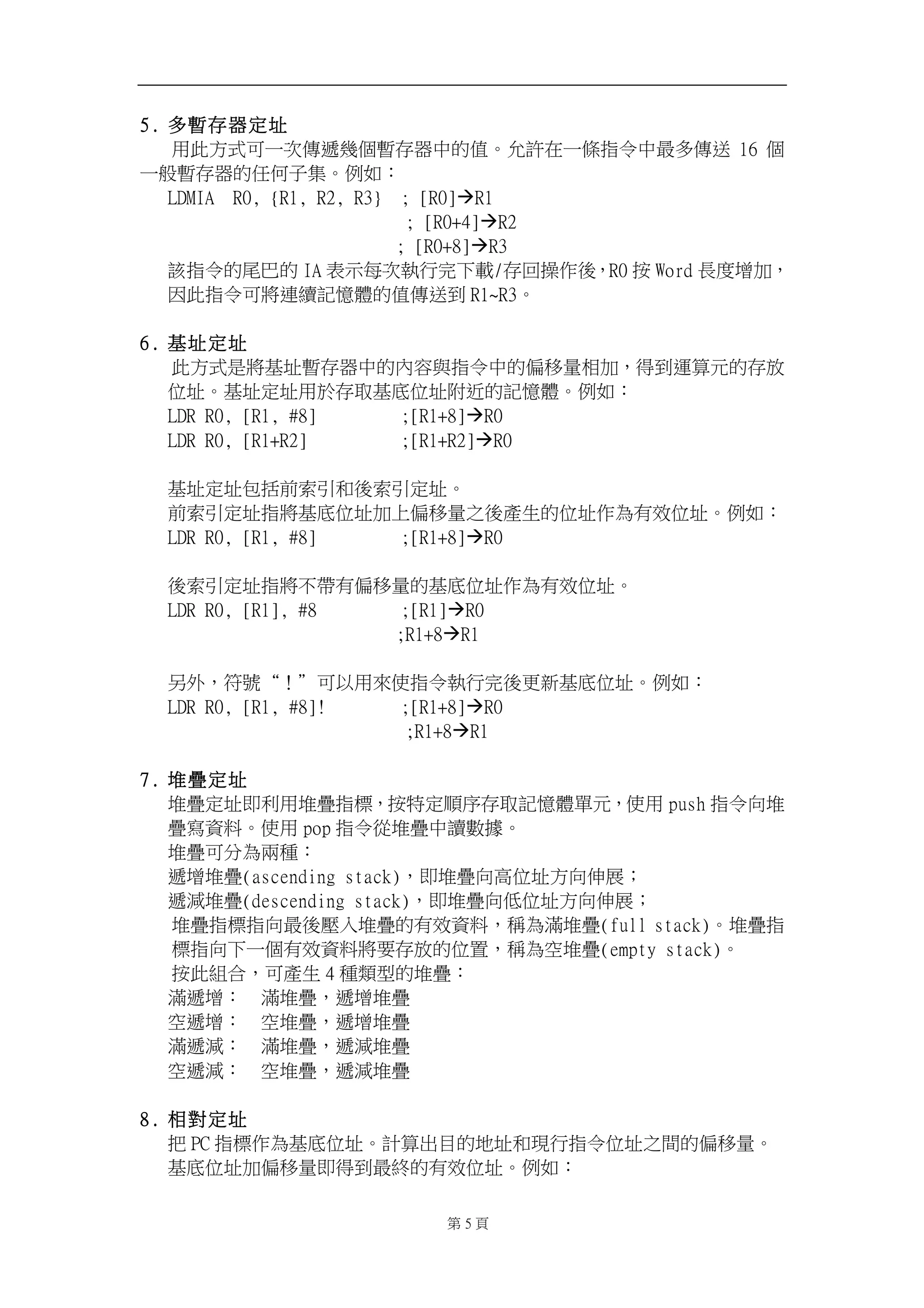

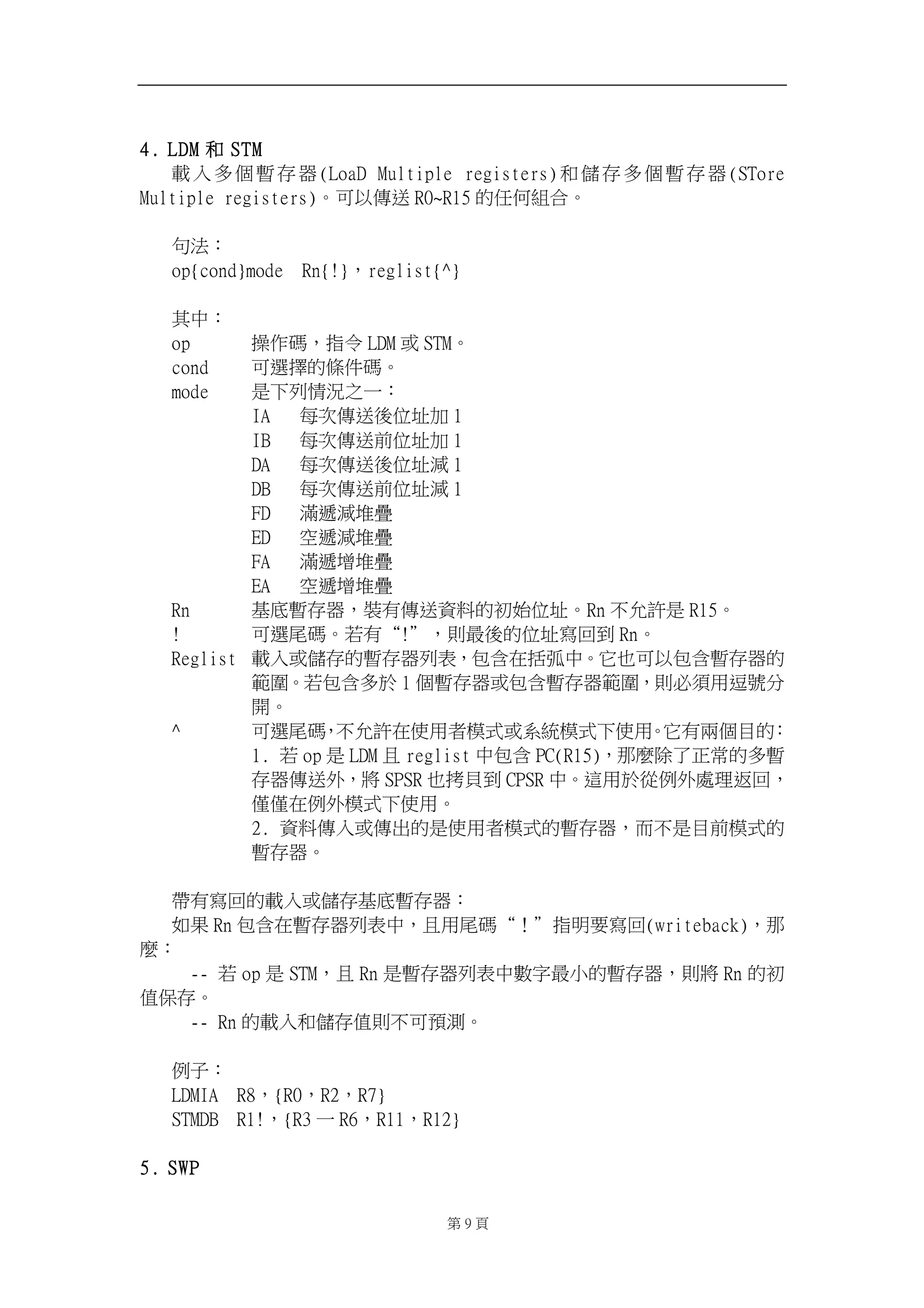

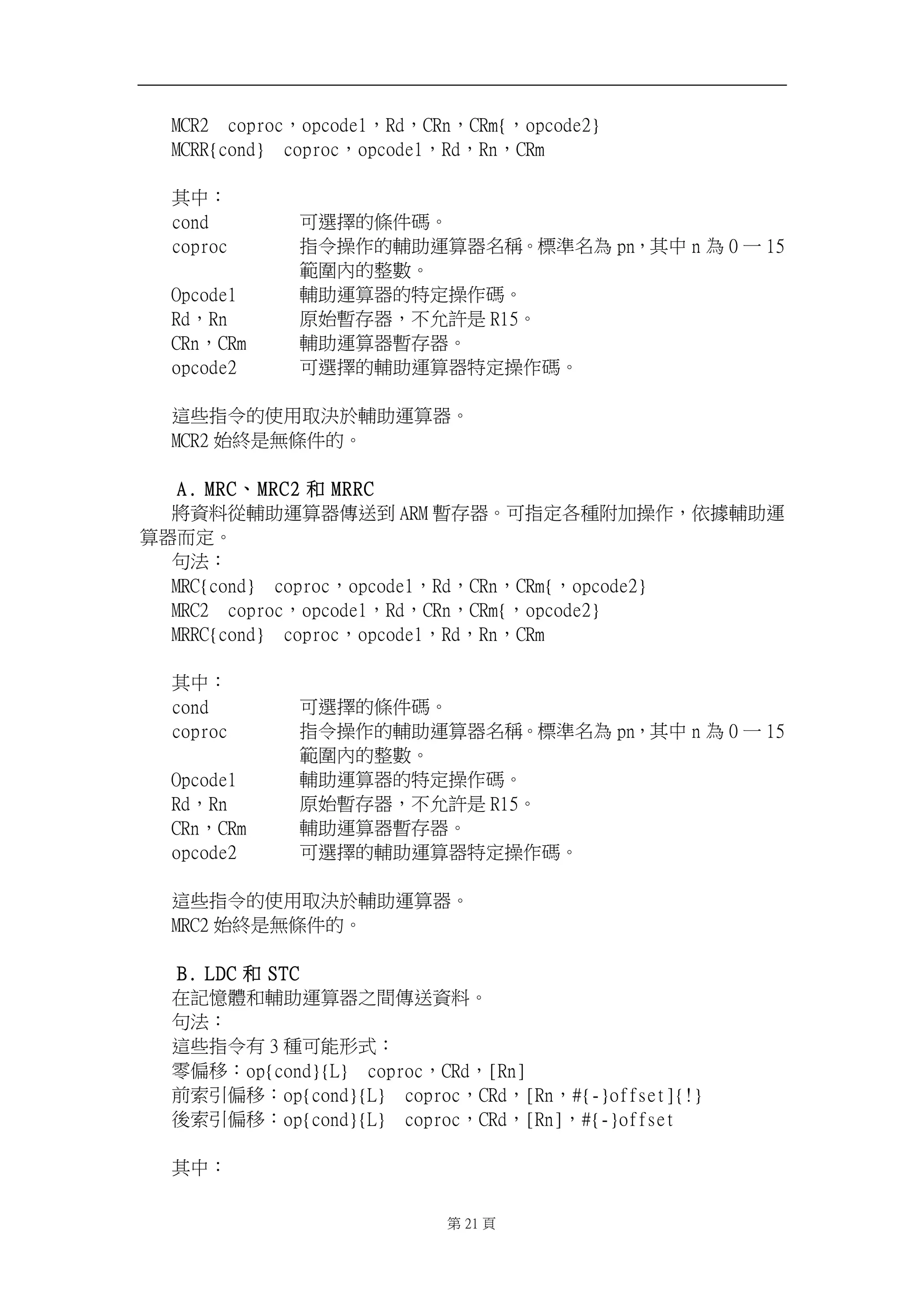

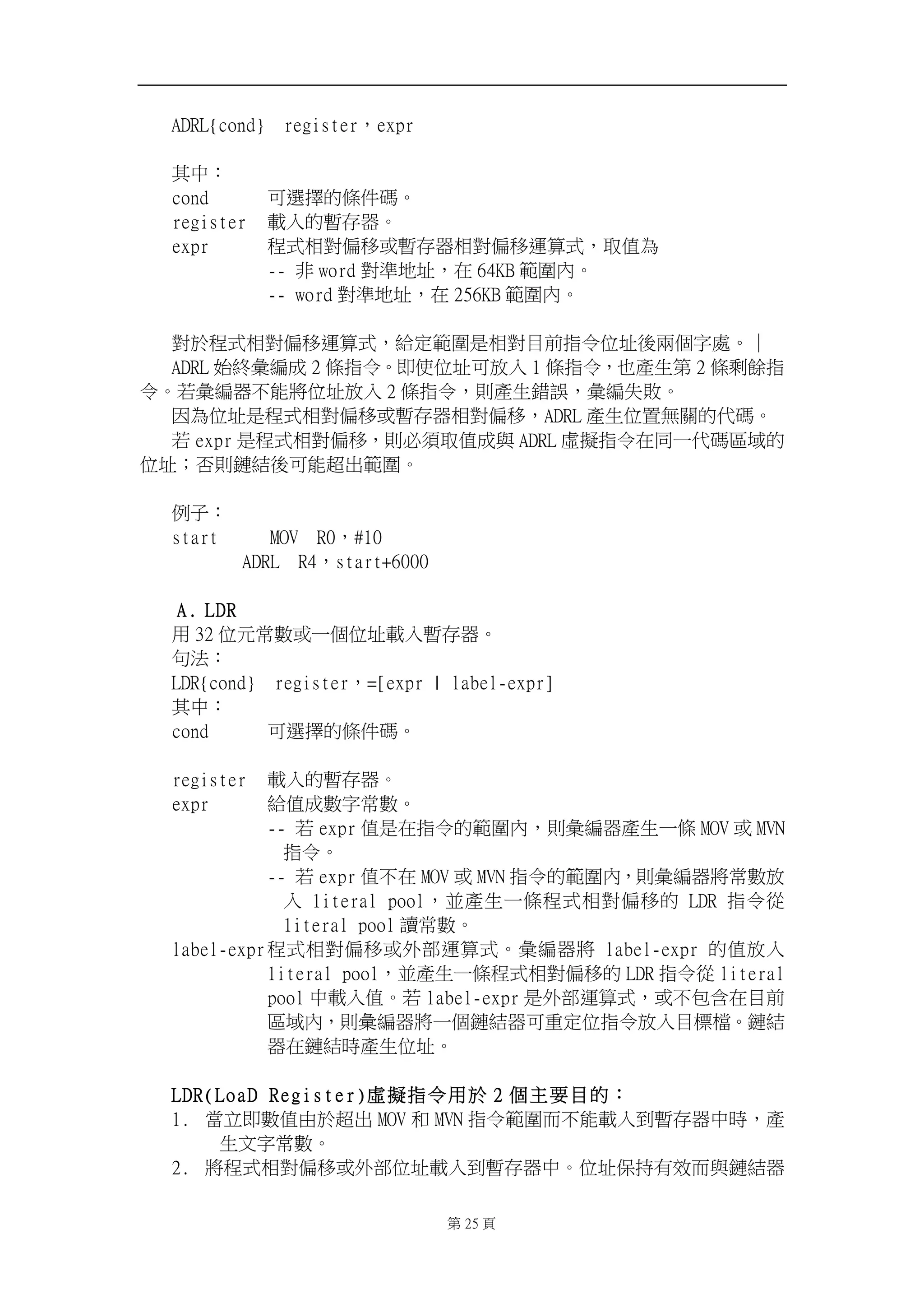

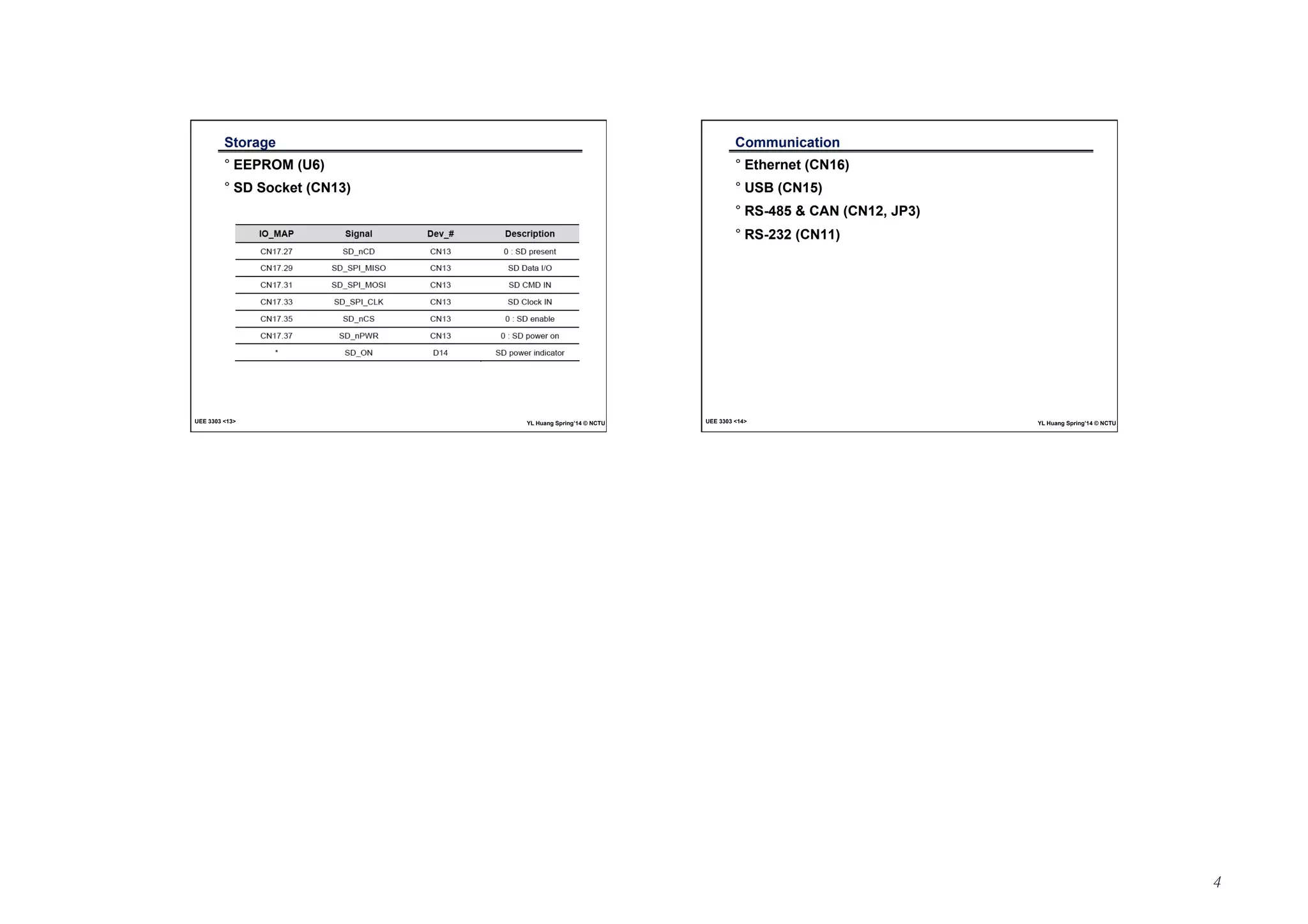

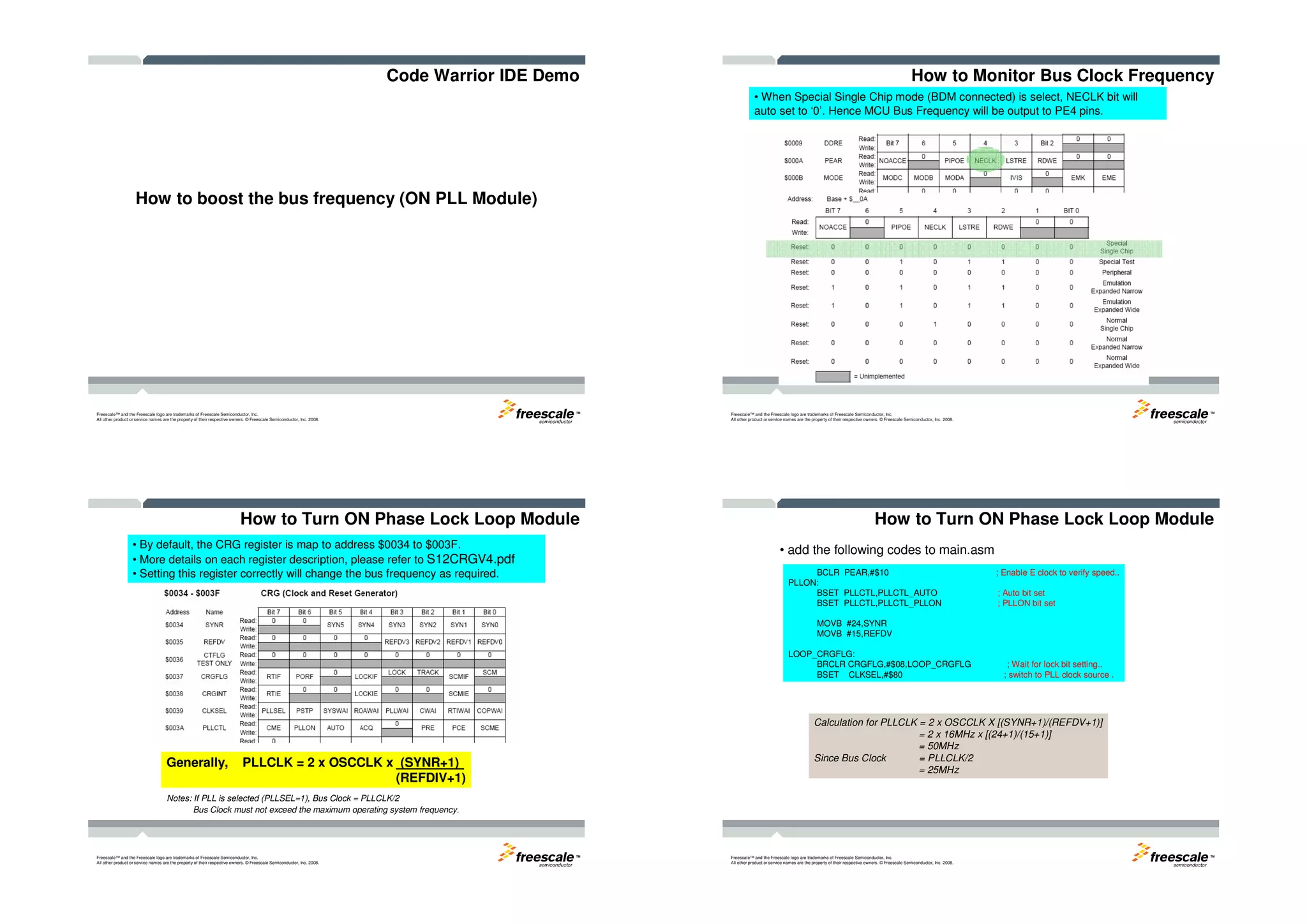

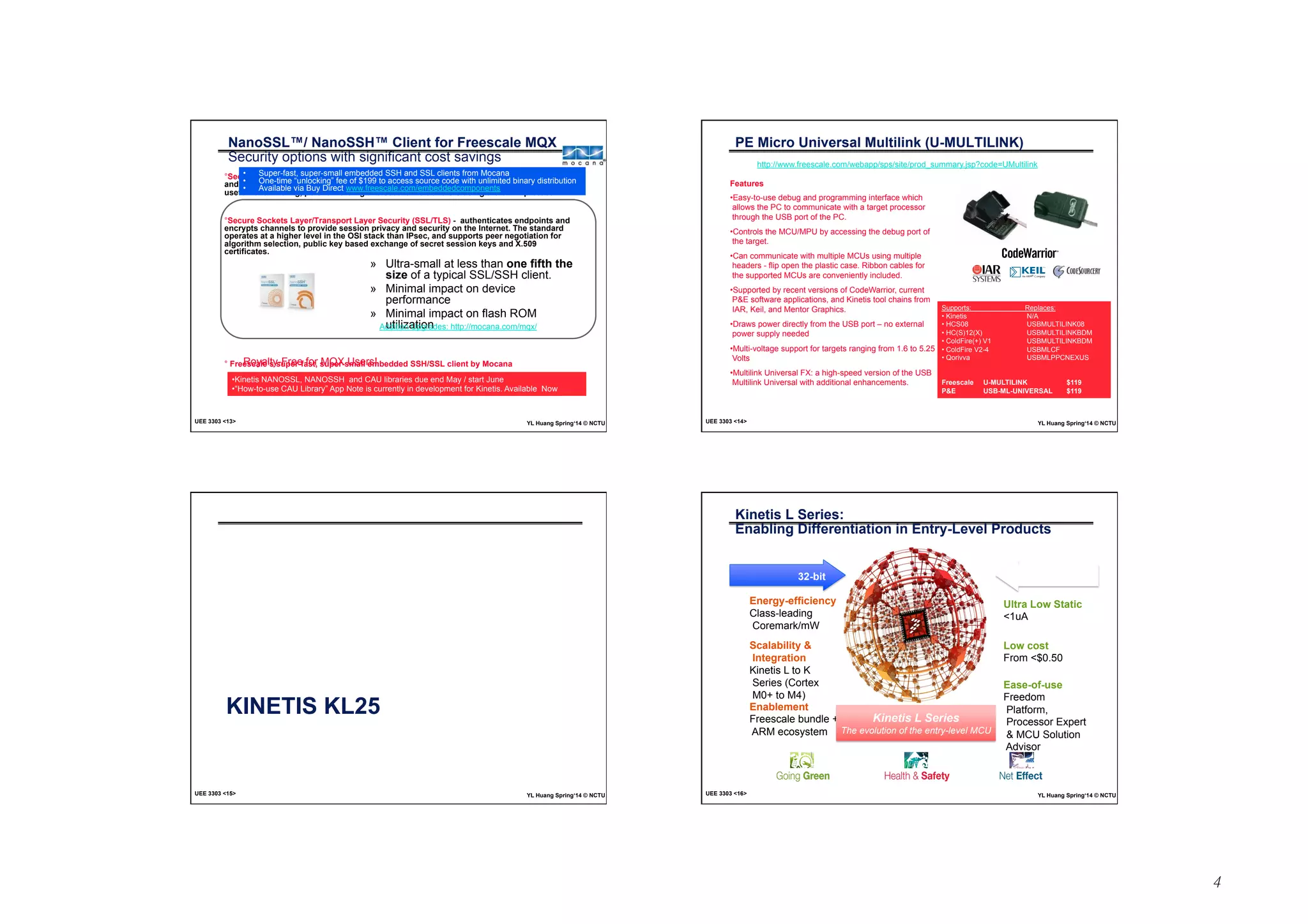

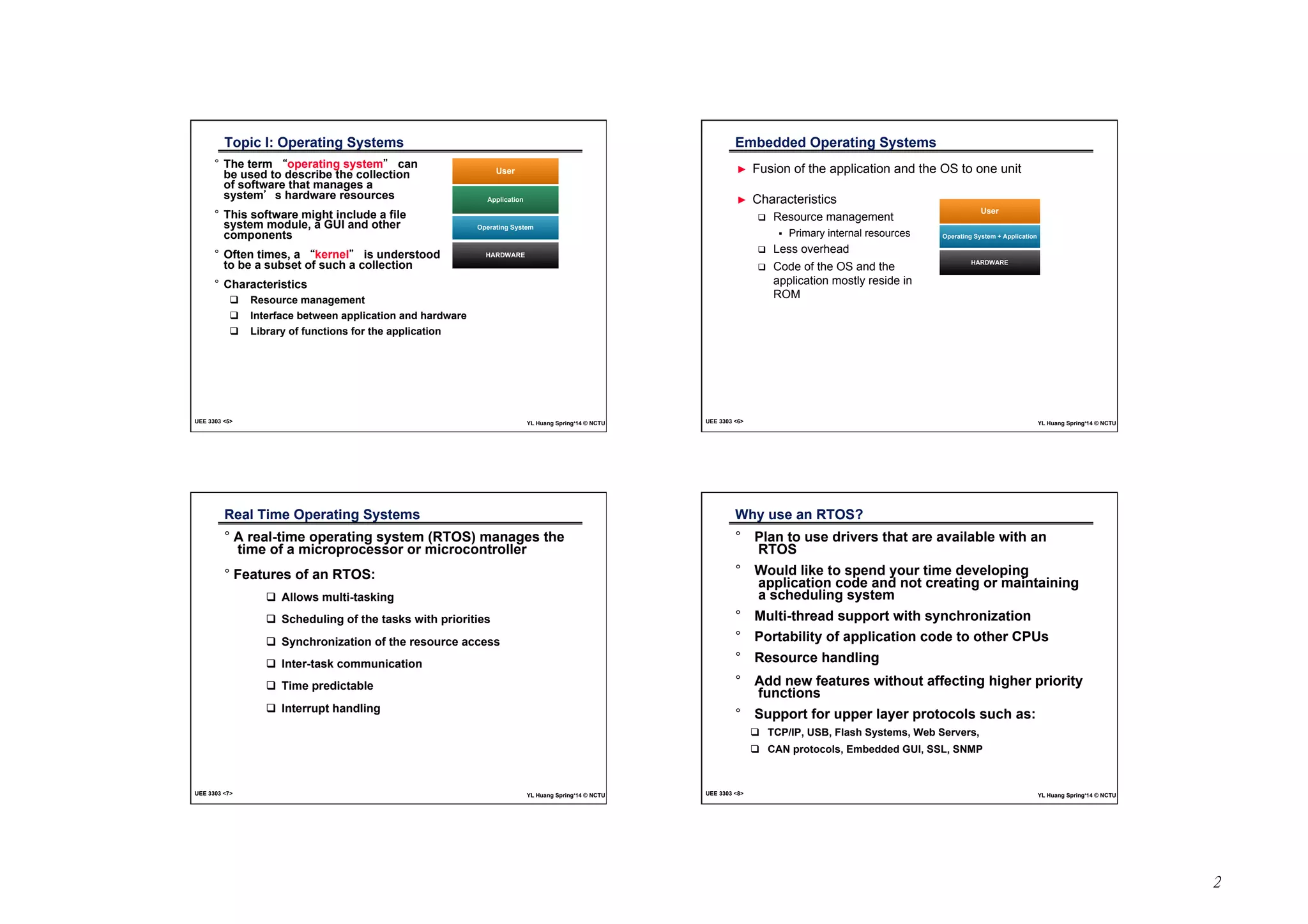

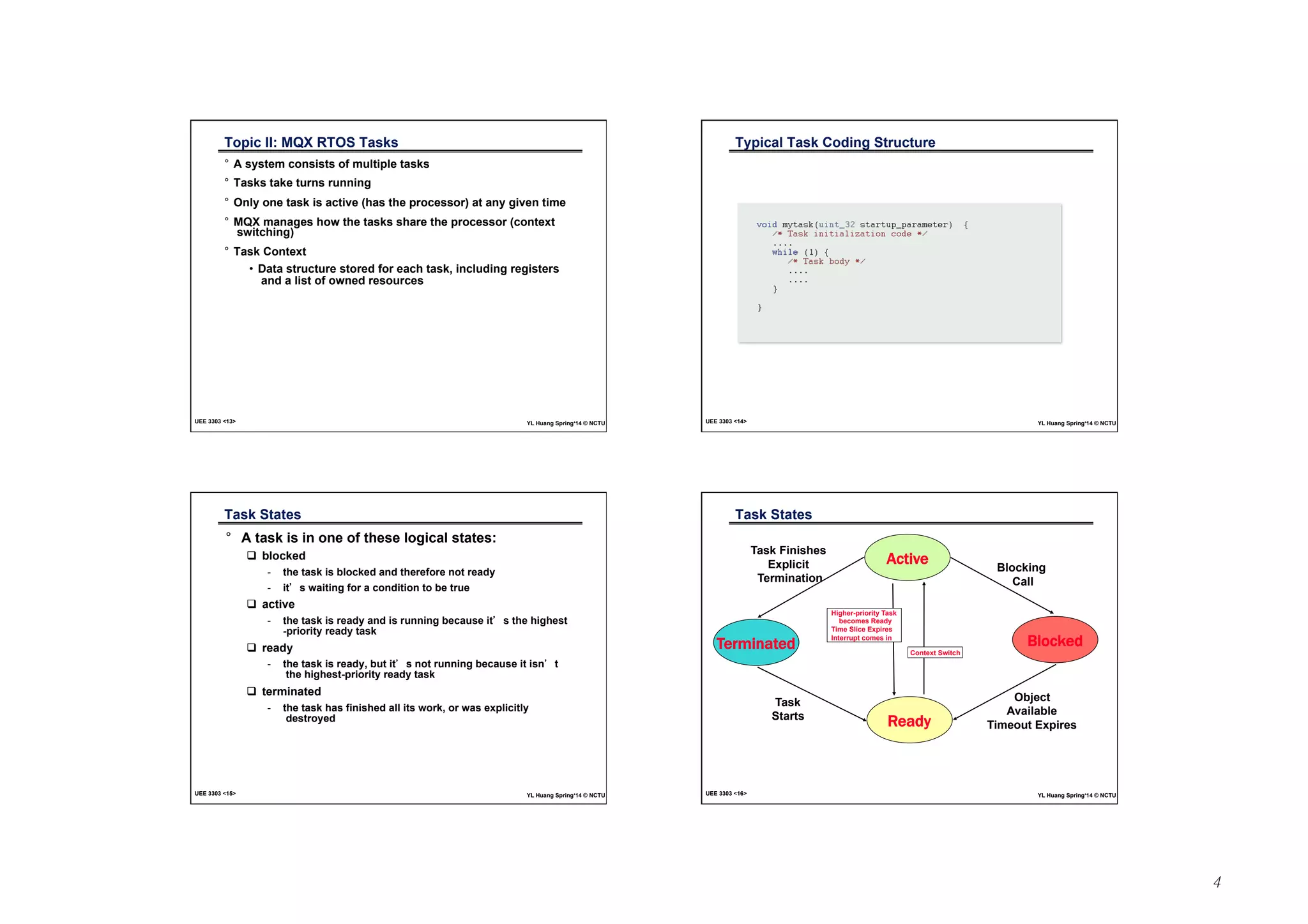

![6

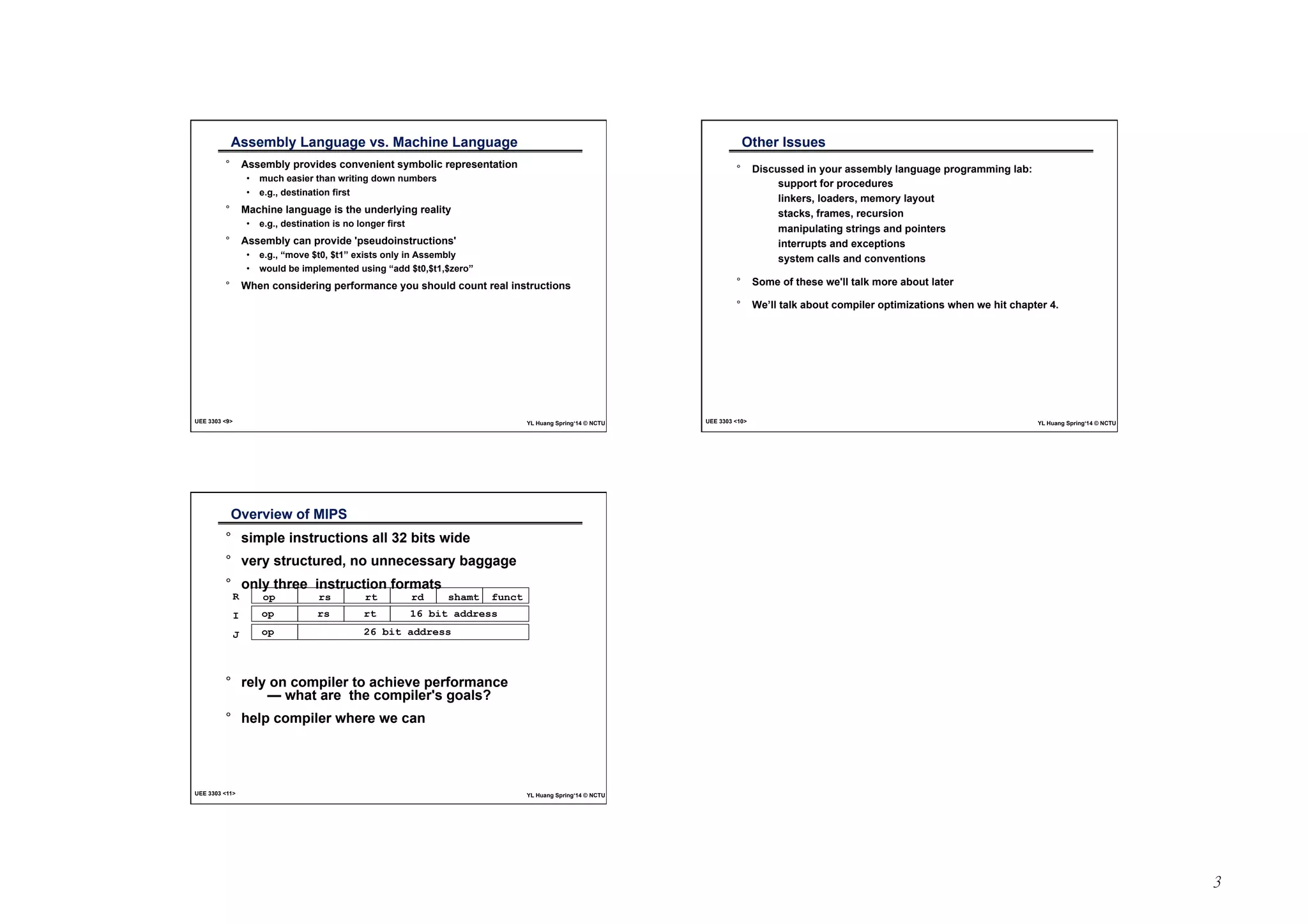

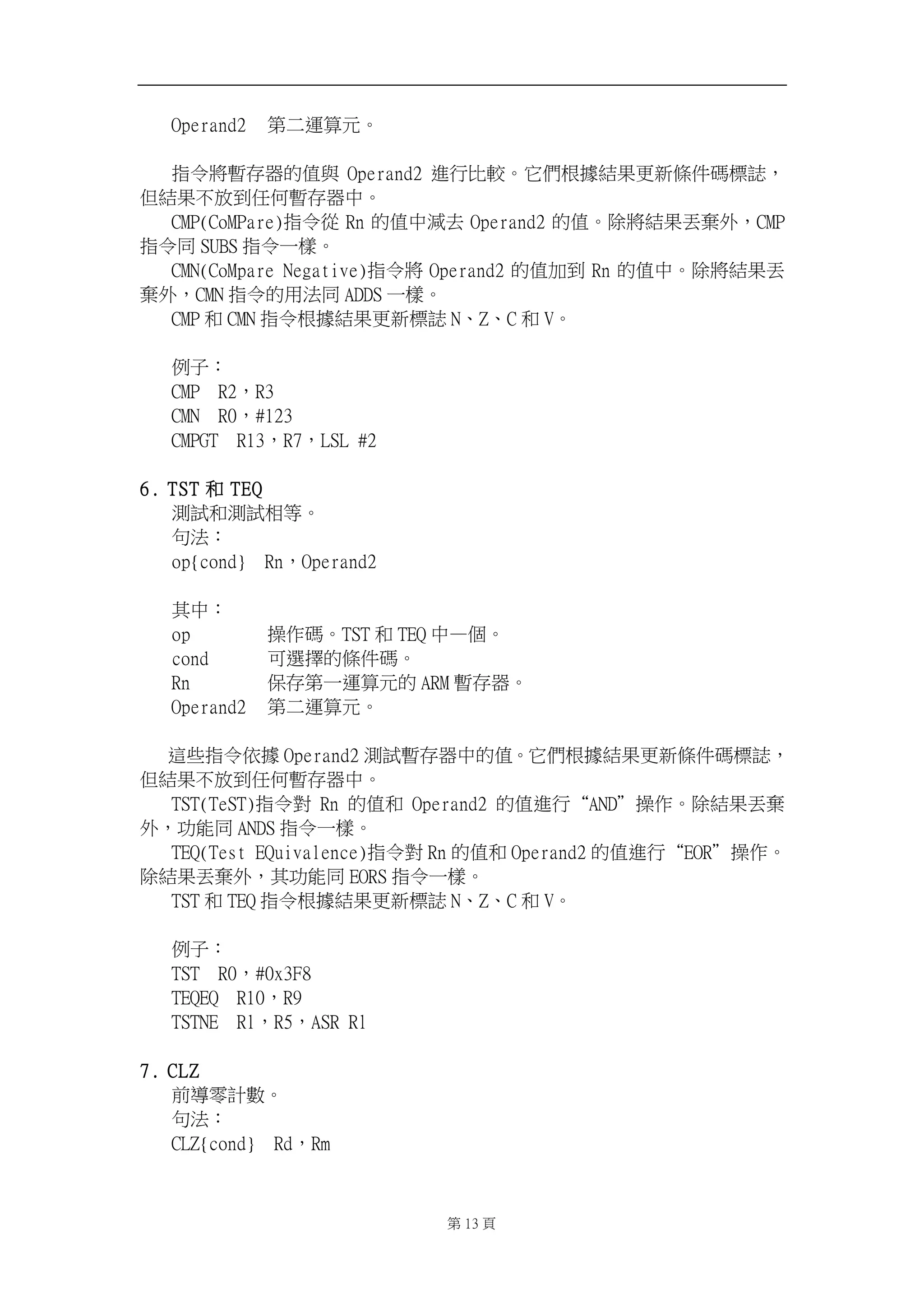

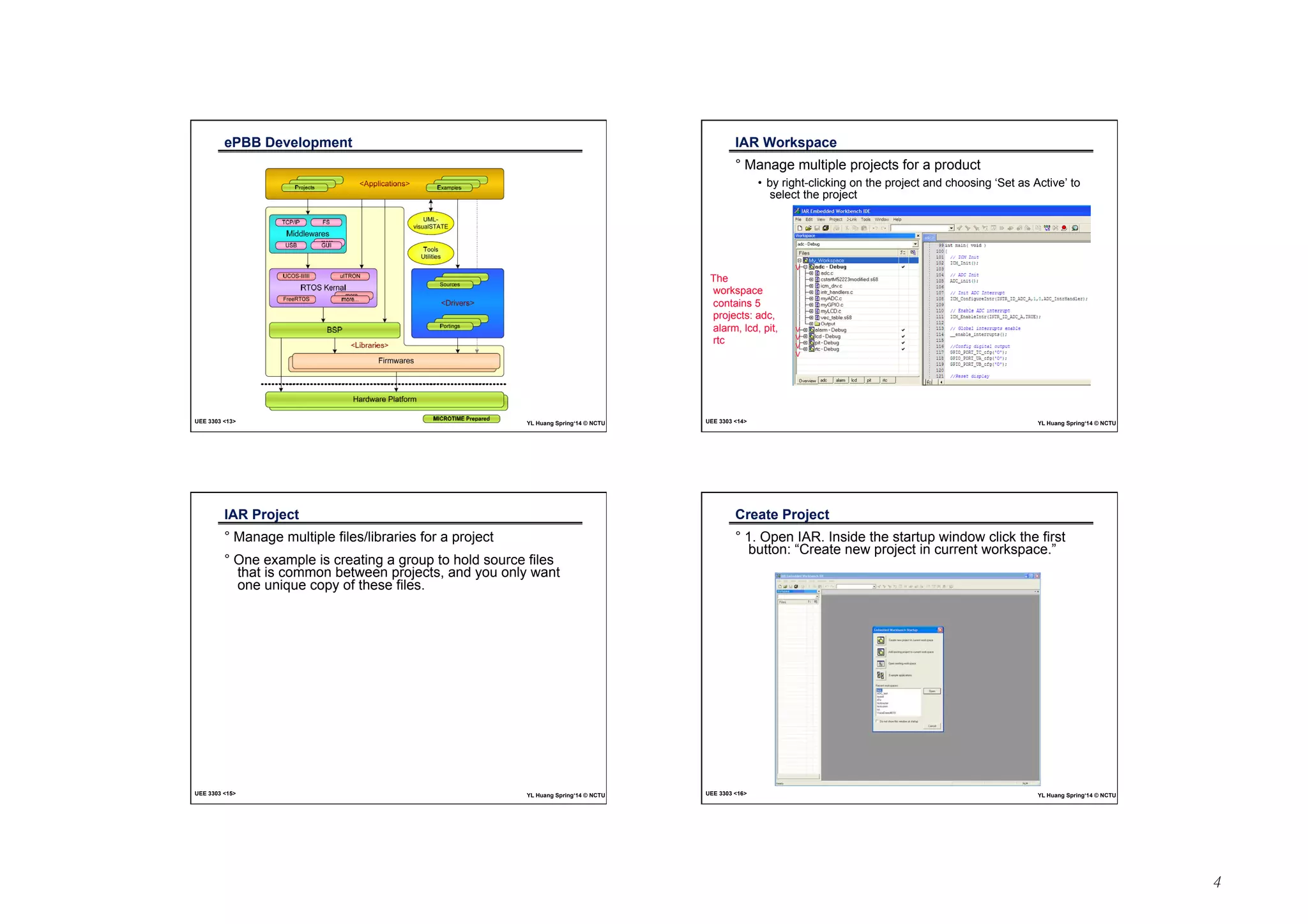

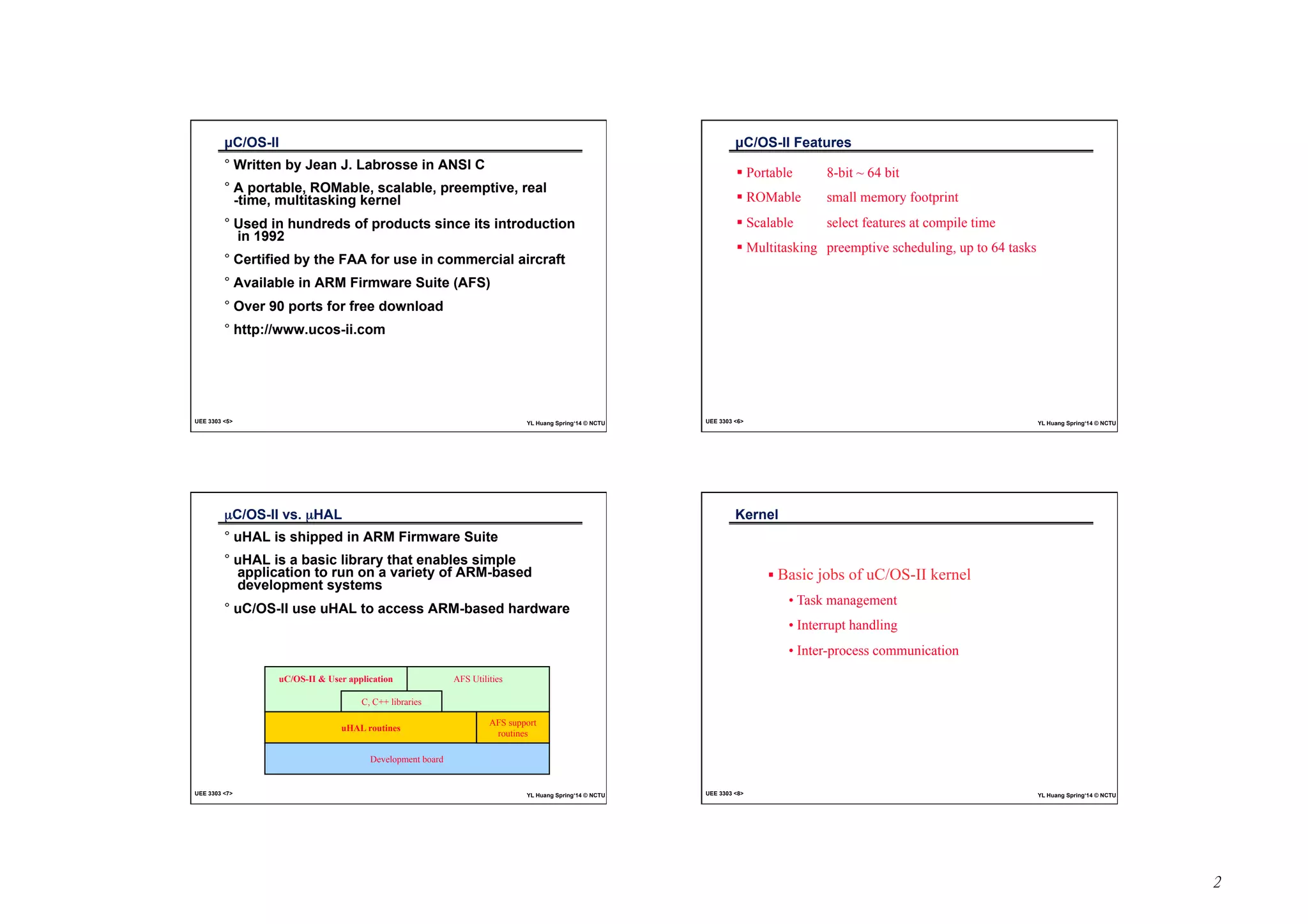

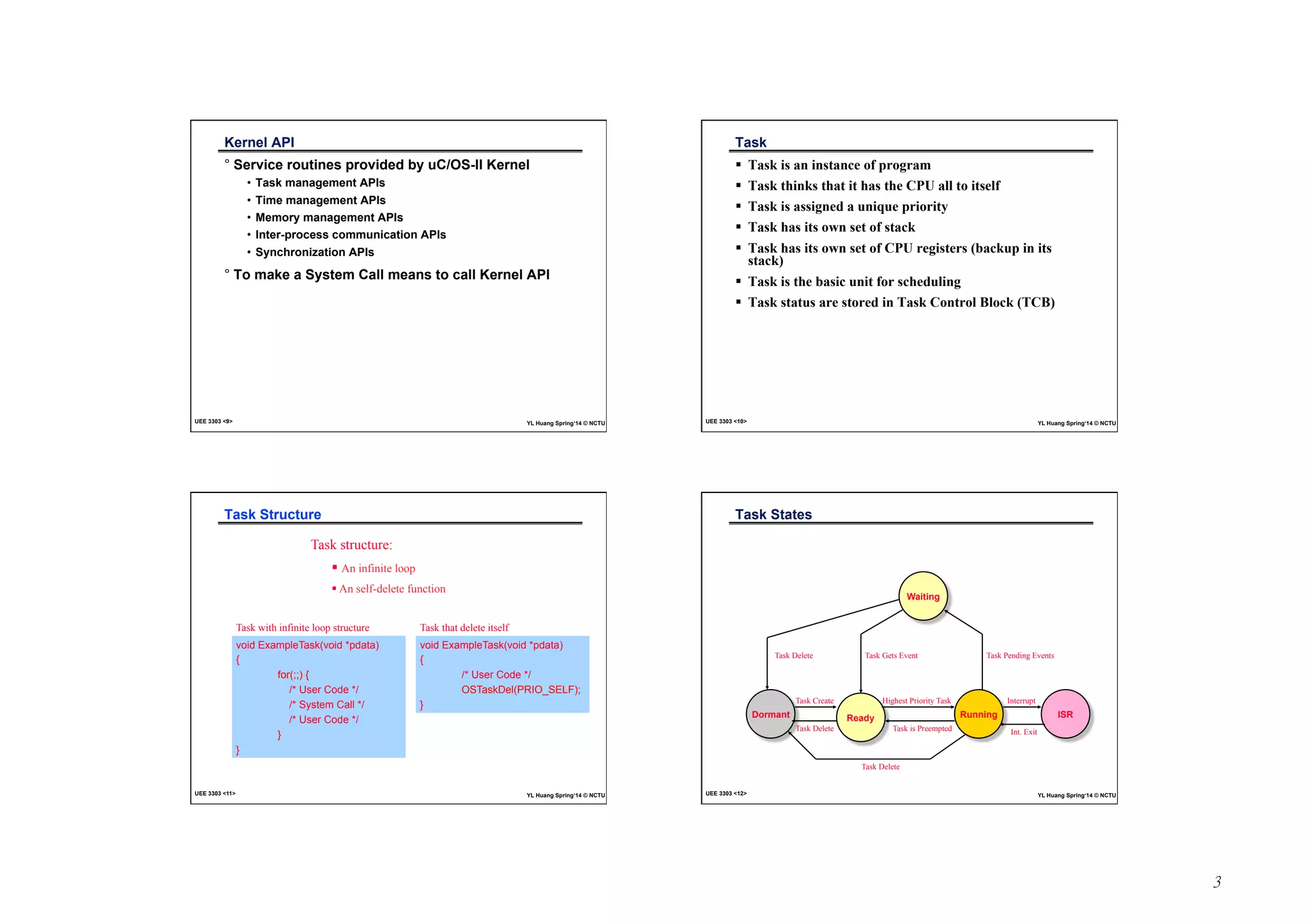

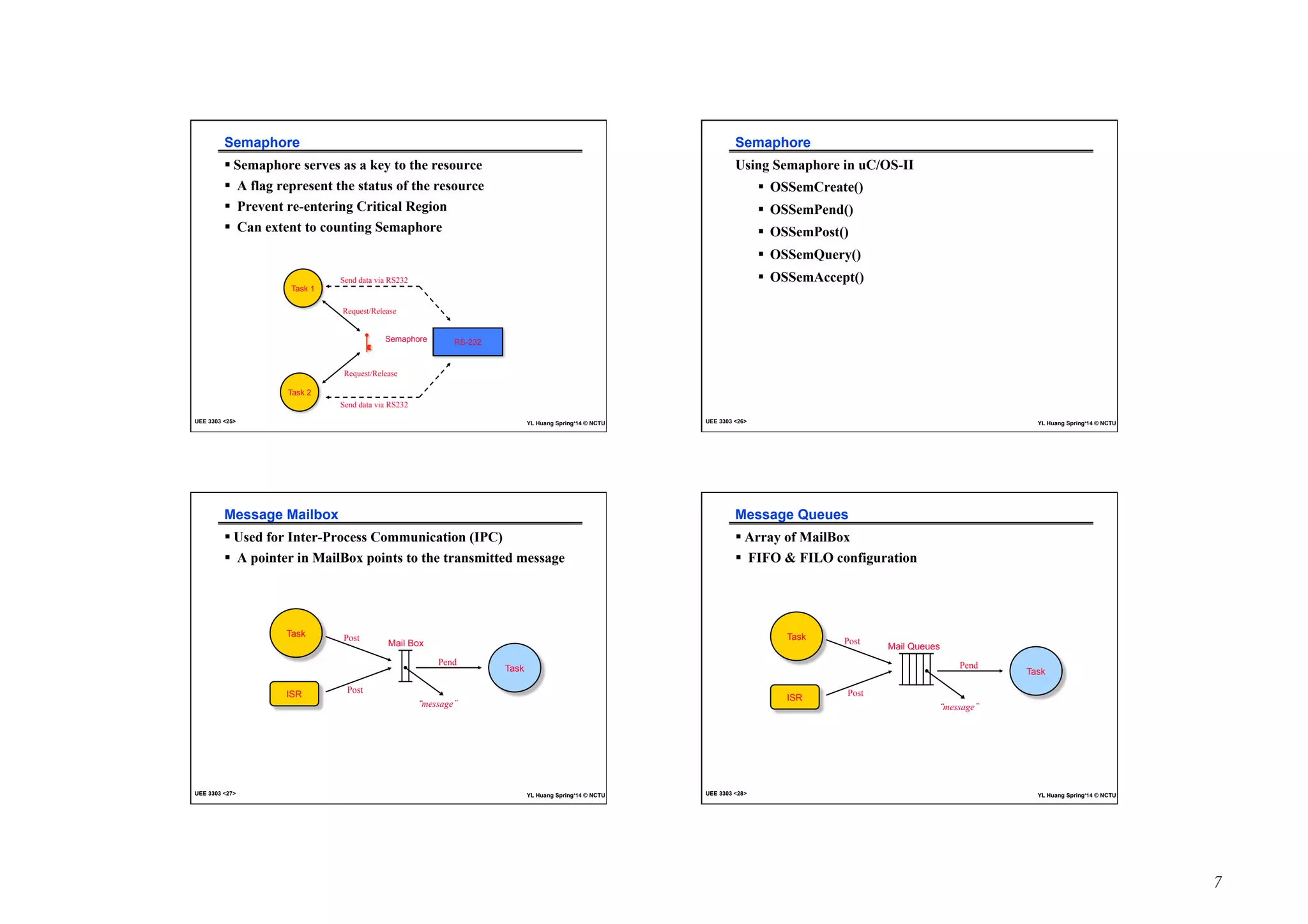

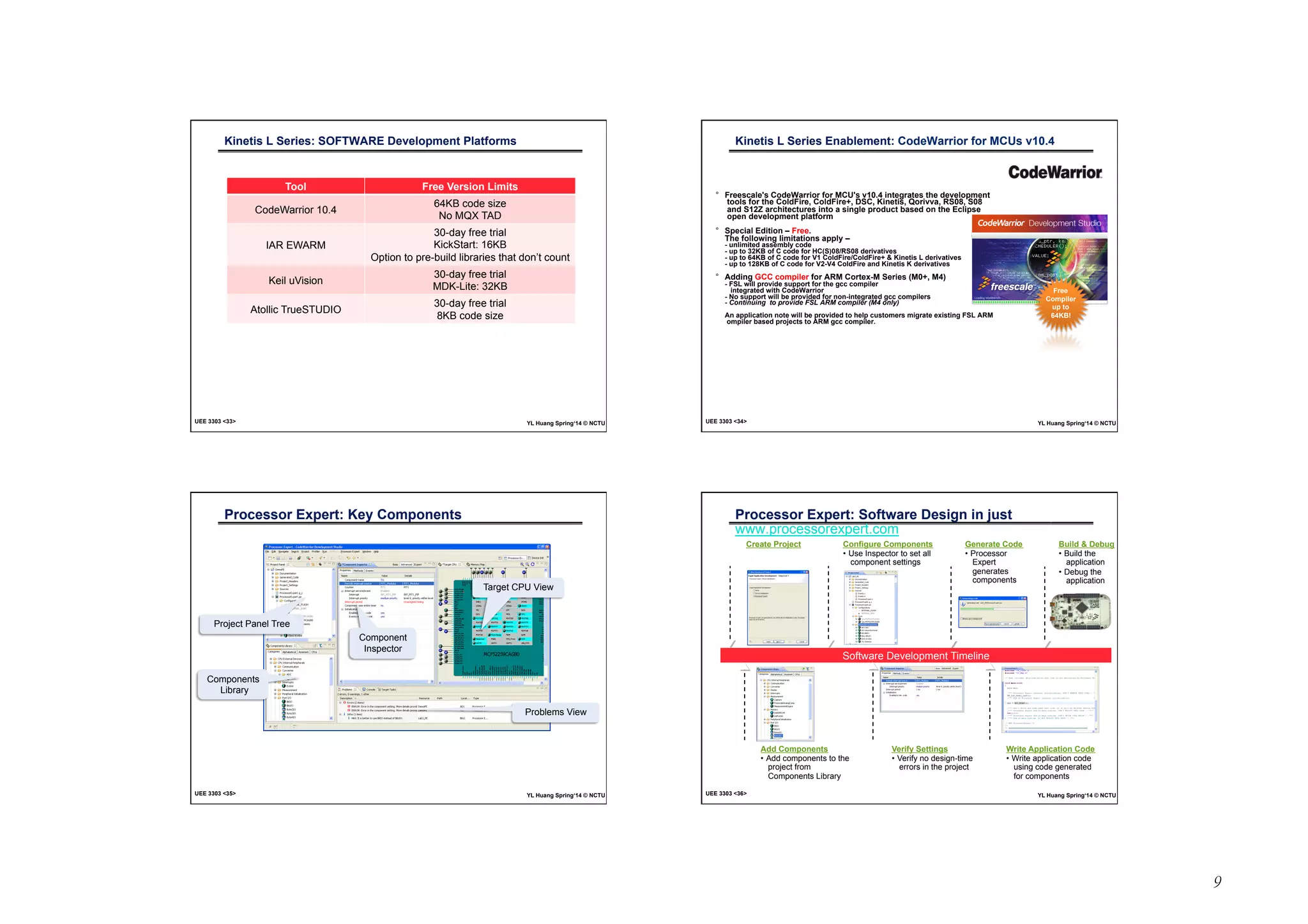

Priority Based FIFO Scheduling

high priority low

FIFO

list of

ready

tasks

Ready

CPU

Scheduler processor time

active

UEE 3303 21 YL Huang Spring‘14 © NCTU

Round-Robin Scheduling

75ms

Task 1

Task 2

50ms

Same

Priority

Time Slice = 50ms Task 3

60ms

Ready

time

Task1 Task2 Task3 Task1 Task3

T0 50ms 100ms 150ms 200ms time

UEE 3303 22 YL Huang Spring‘14 © NCTU

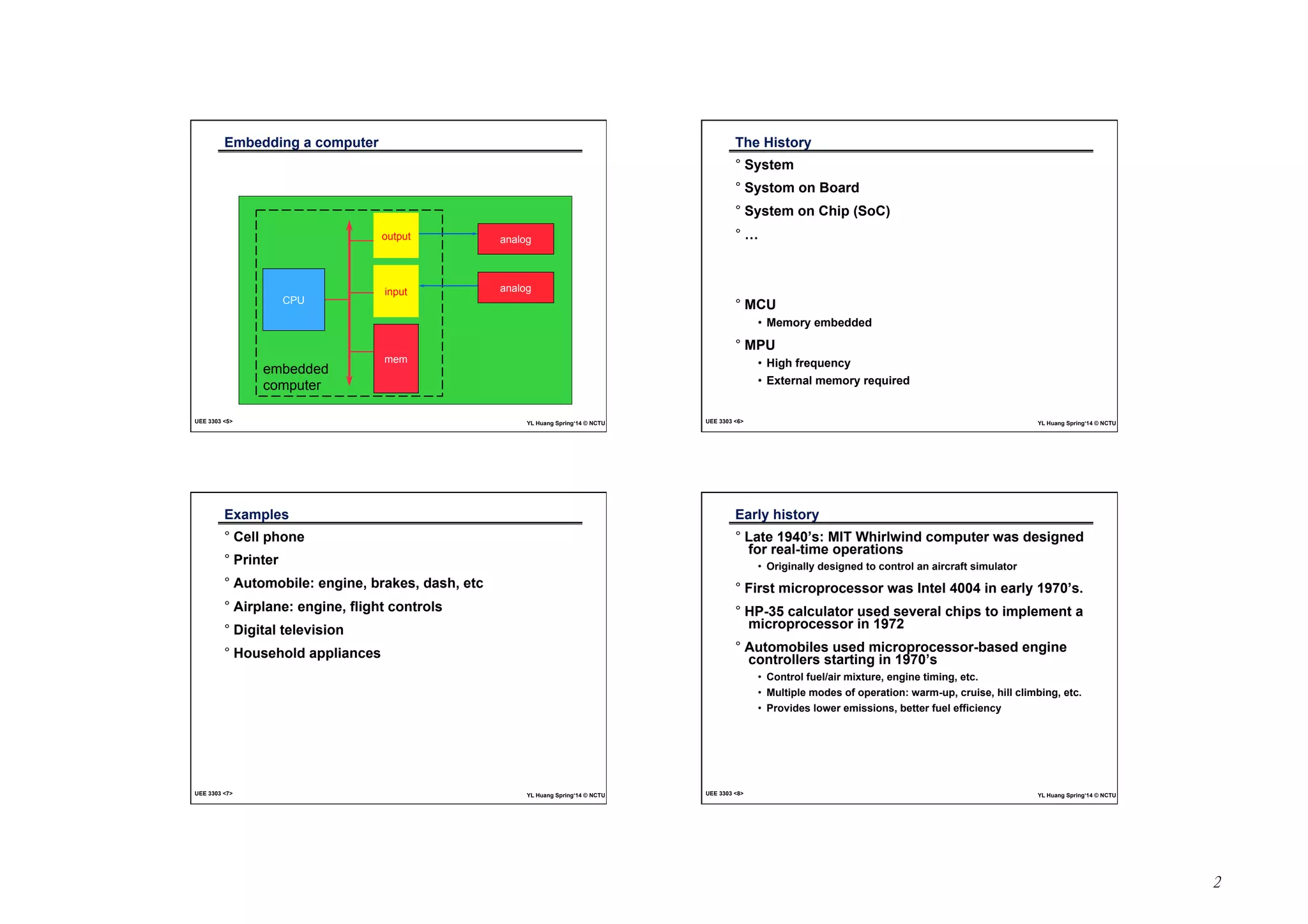

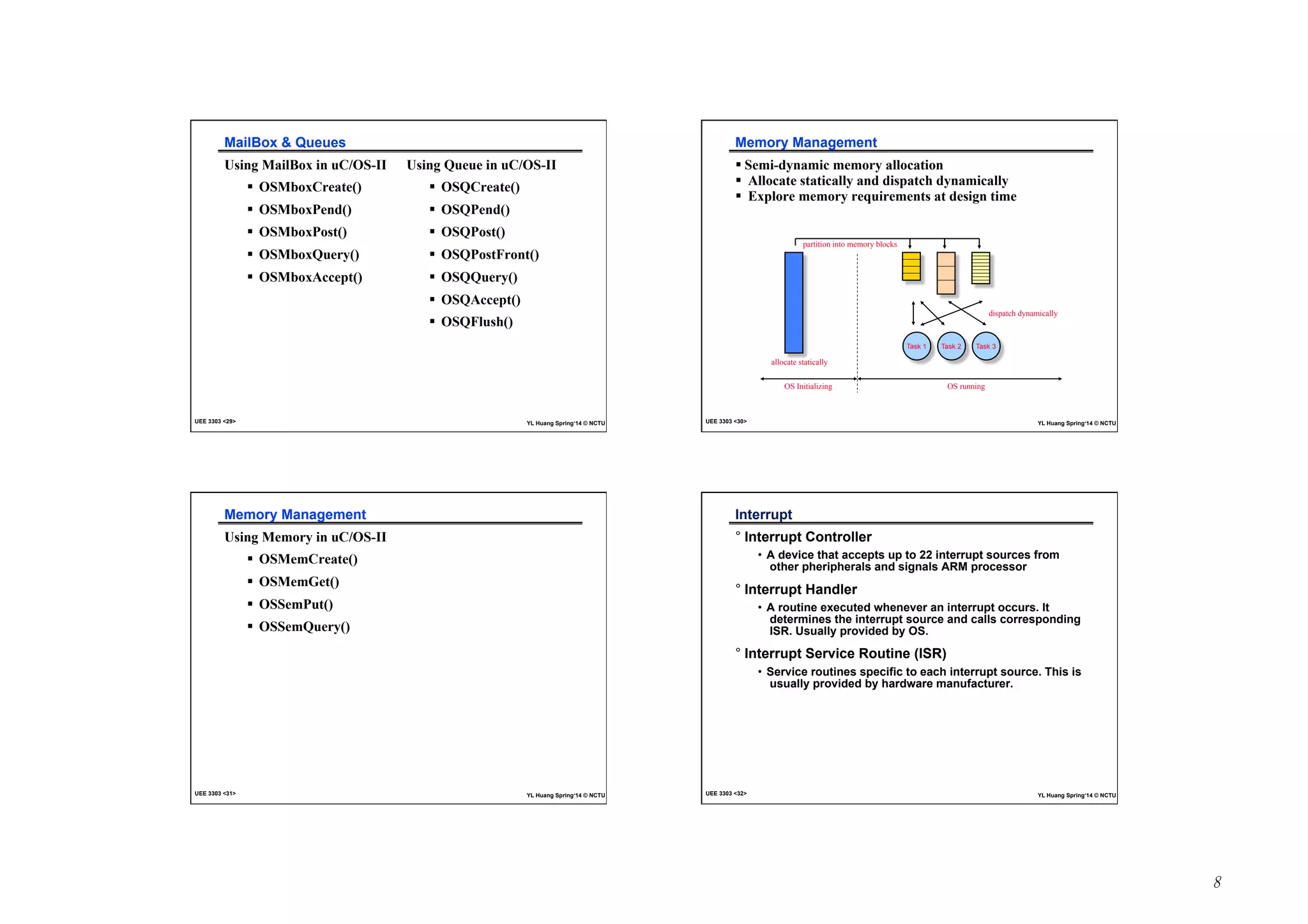

MQX Tasks

° Tasks can be automatically

created when MQX Starts;

also, any task can create

another task by calling

_task_create() or

_task_create_blocked()

° The function

_task_create() puts the

child task in the ready state

and the scheduler puts the

higher priority task to run

° If _task_create_blocked

is used the task is not ready

until _task_ready() is

called

_task_abort

_task_destroy

Terminated

_task_create

Active

Ready

_task_block

Blocked

_task_ready

UEE 3303 23 YL Huang Spring‘14 © NCTU

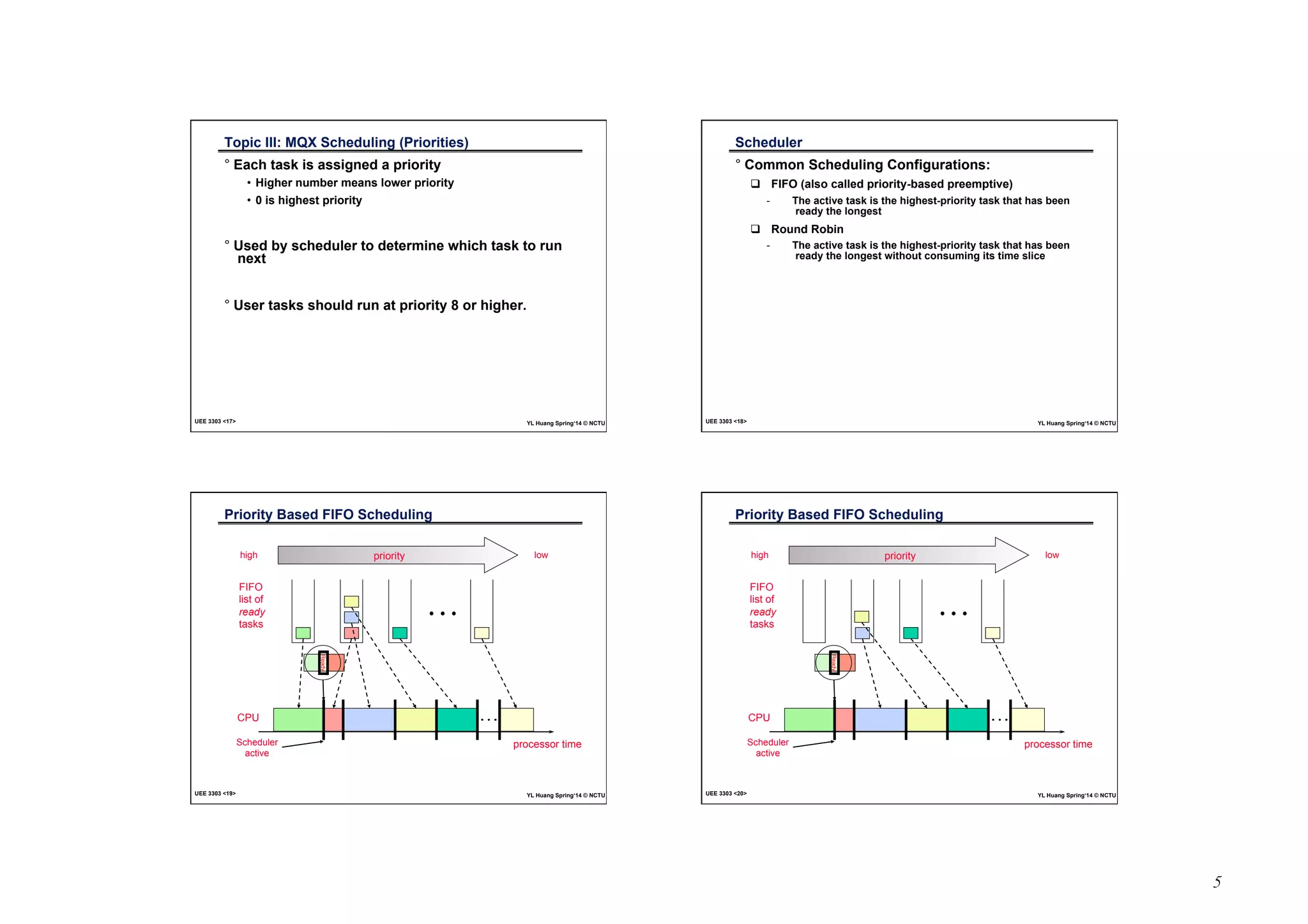

Creating a Task

° When creating a task you have to:

! Make the task prototype and index definition

#define INIT_TASK 5

extern void init_task(uint_32);

! Add the task in the Task Template List

TASK_TEMPLATE_STRUCT MQX_template_list[] =

{

{ TASK_INDEX, TASK, STACK, TASK_PRIORITY,

TASK_NAME, TASK_ATTRIBUTES, CREATION_PARAMETER,

TIME_SLICE}

}

Using the init_task example:

TASK_TEMPLATE_STRUCT MQX_template_list[] =

{

{INIT_TASK, init_task, 1500, 9, init,

MQX_AUTO_START_TASK, 0, 0},

}

UEE 3303 24 YL Huang Spring‘14 © NCTU](https://image.slidesharecdn.com/random-140905124409-phpapp02/75/slide-92-2048.jpg)