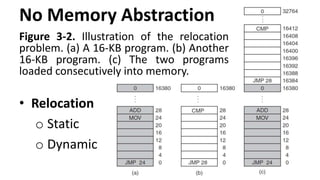

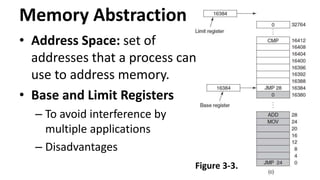

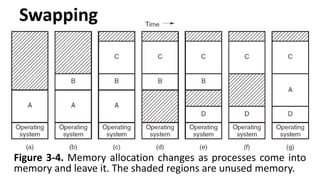

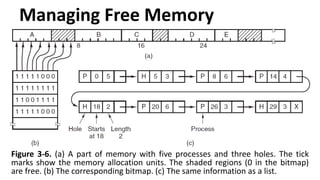

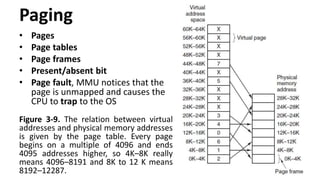

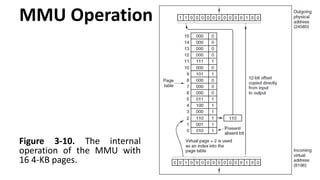

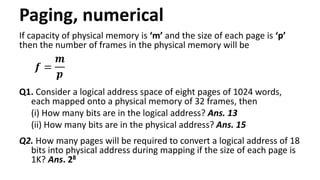

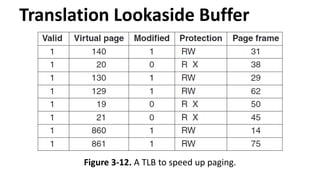

The document discusses memory management in operating systems, focusing on concepts like virtual memory, swapping, and paging. It covers memory abstraction techniques, including the management of free memory and the operation of memory management units (MMUs), and highlights the importance of page tables and translation lookaside buffers (TLBs) for efficient memory access. Additionally, it presents examples and numerical analyses related to logical and physical address mapping.