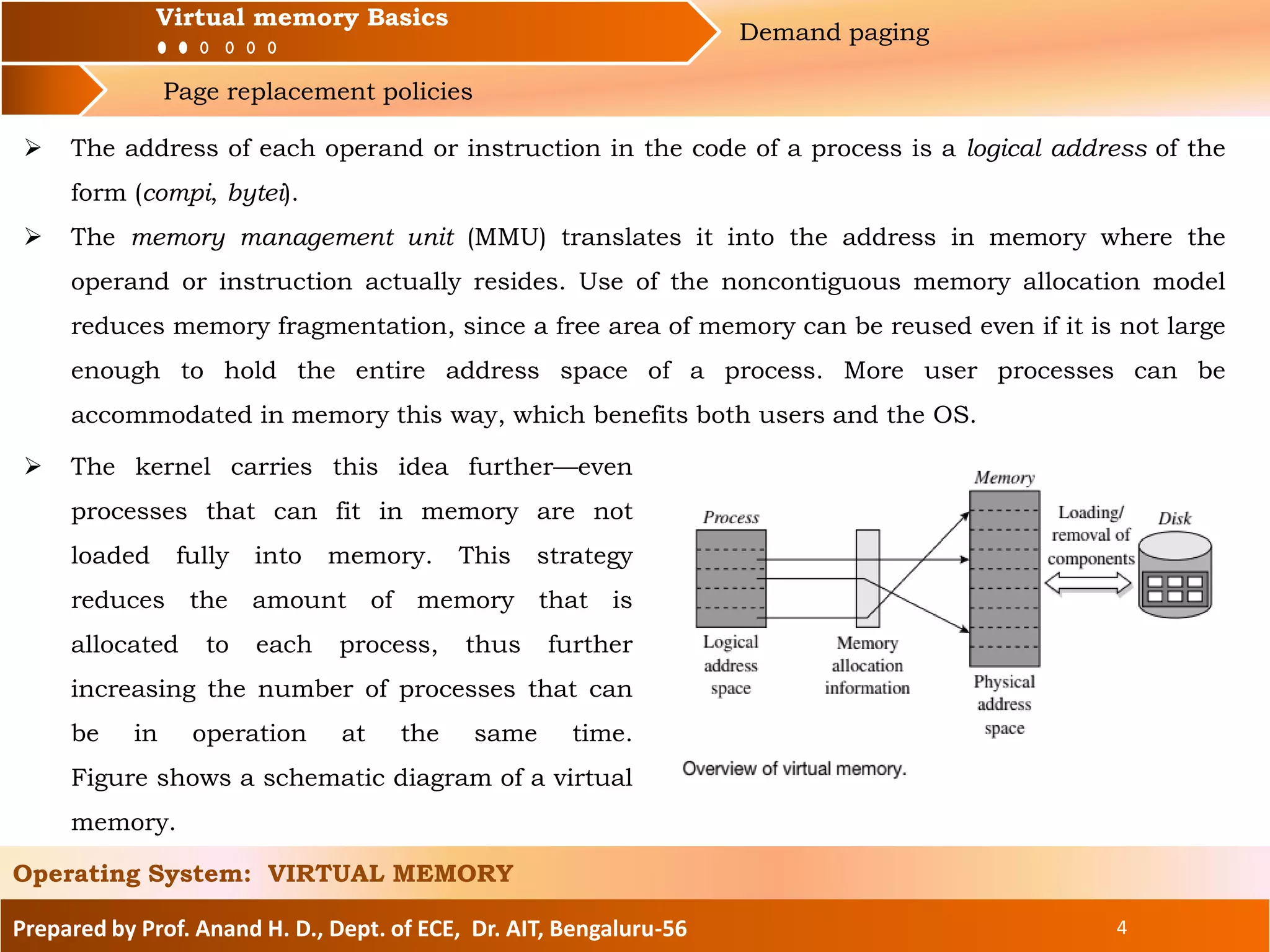

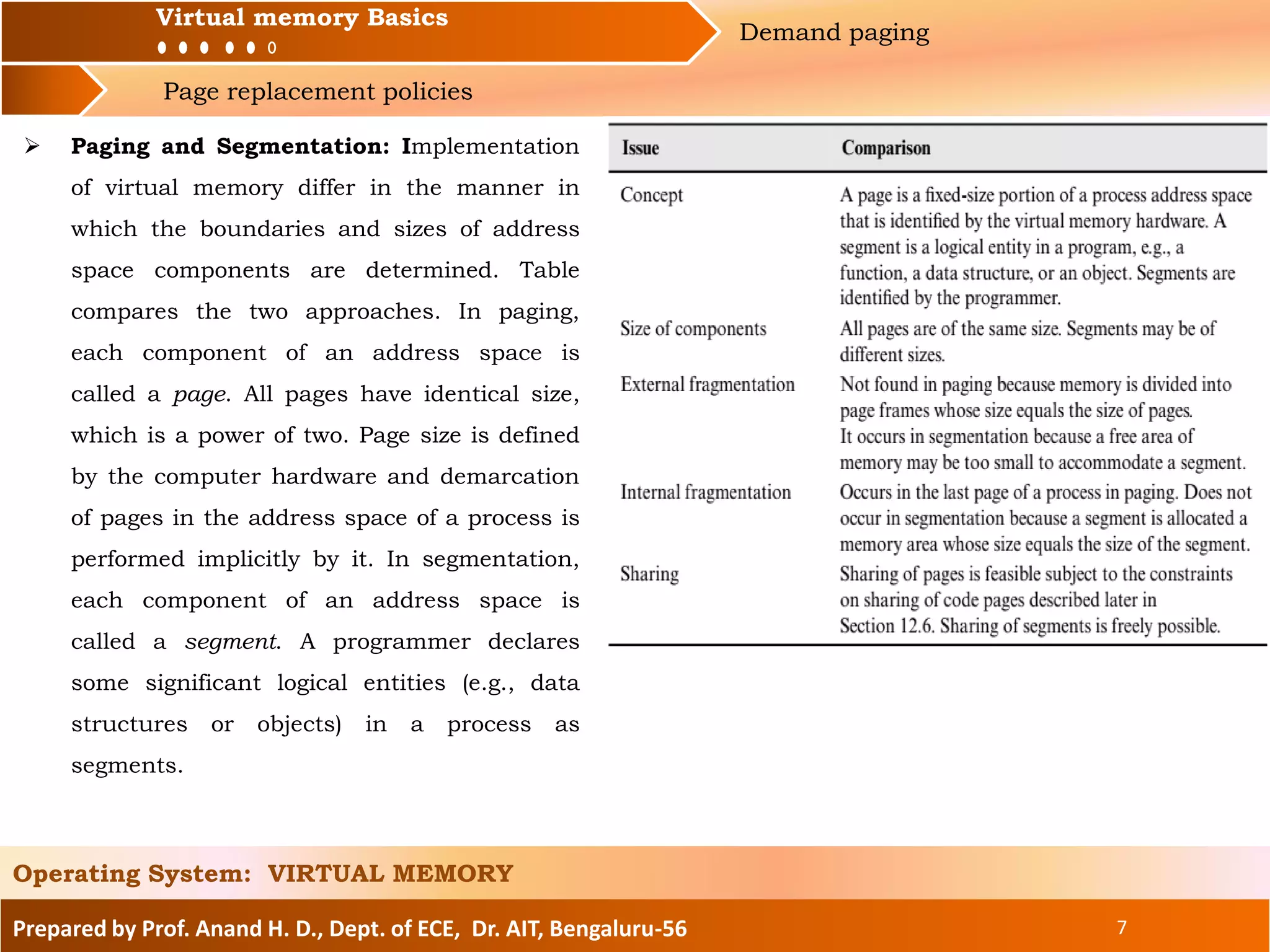

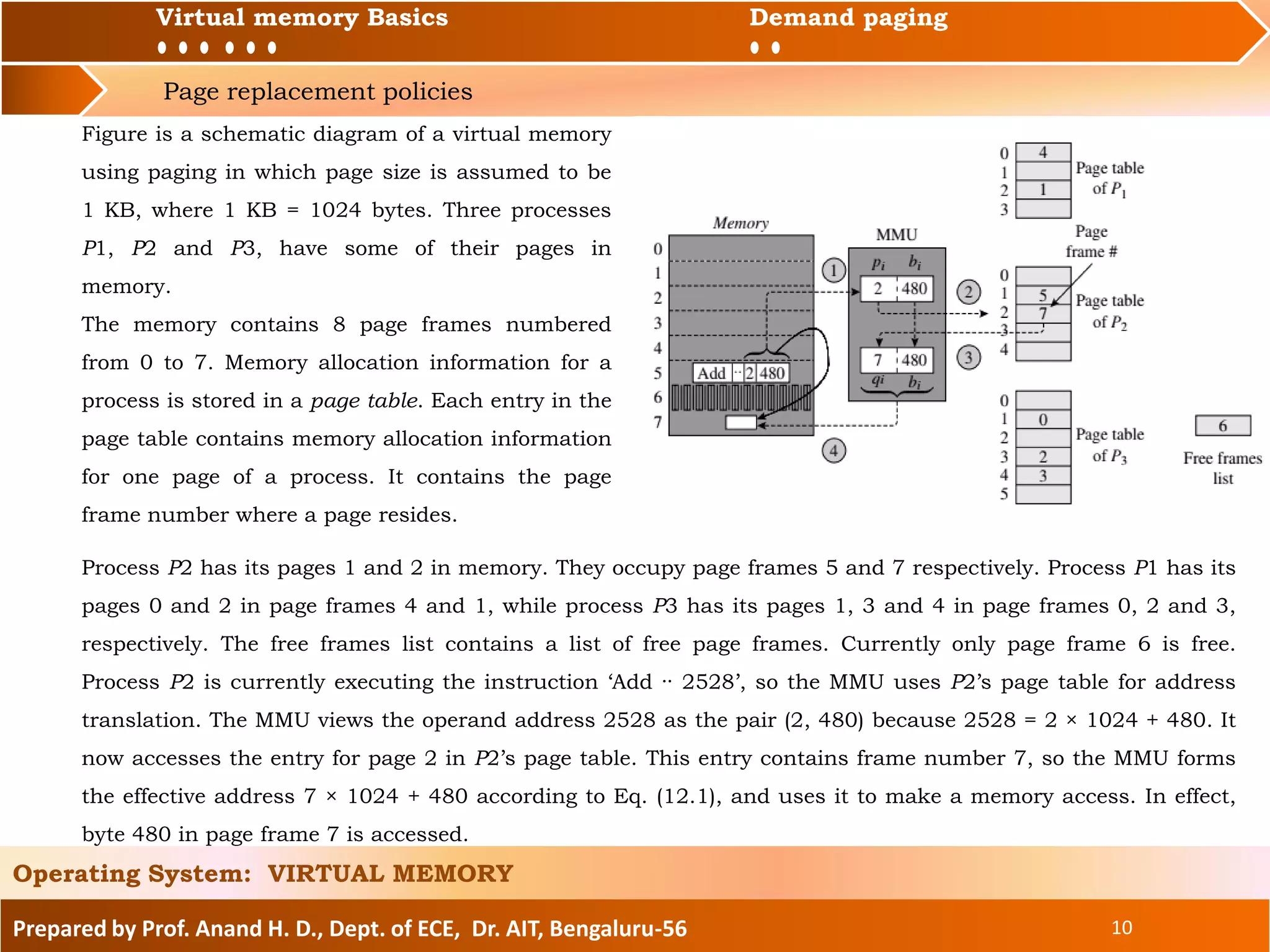

The document discusses virtual memory and page replacement policies in operating systems. It begins with an overview of virtual memory basics such as using a combination of hardware and software to create an illusion of memory larger than physical RAM. It describes how processes are divided into pages that can be loaded and removed from memory as needed. The document then covers demand paging, where only needed pages are loaded, and page replacement policies including optimal, FIFO, and LRU which aim to replace pages least likely to be used soon. It concludes with contact information for the author.