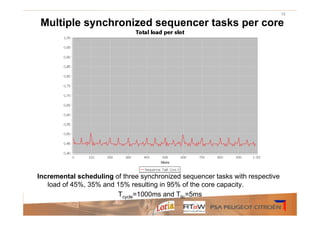

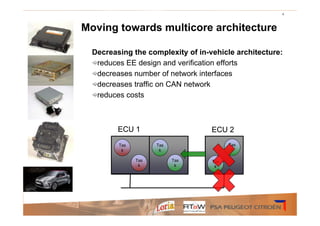

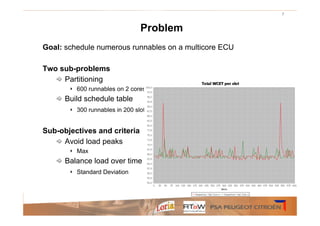

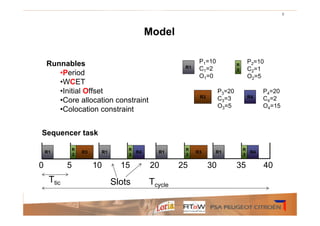

The document discusses the scheduling challenges of runnables on multicore ECUs in automotive architectures, highlighting the increase in ECUs from around 20 in 2000 to over 40 in 2010. It presents methods such as load balancing algorithms to optimize scheduling and meet automotive standards, along with experimental results demonstrating the effectiveness of proposed solutions. Conclusion notes the need for new software architecture designs and scheduling heuristics compatible with AUTOSAR standards as multicore ECUs become prevalent.

![9

Solution

Partitioning is dealt with as a bin packing problem

Worst fit decreasing algorithm with fixed number of bins

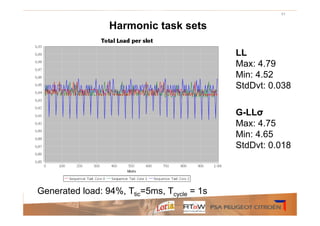

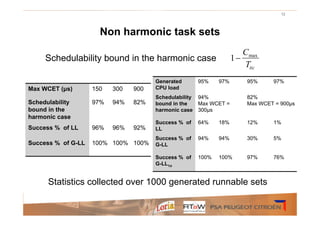

Load Balancing is done with the Least Loaded algorithm (LL)

inspired from CAN domain [Grenier and Navet ERTSS2008]

Extended to handle non harmonic runnable sets (G-LL)

Improved so as to reduce further load peaks (G-LLσ)

Implemented in a tool

Freely available soon at http://www.realtimeatwork.com](https://image.slidesharecdn.com/ertss2010multicorescheduling-100605070656-phpapp01/85/Multicore-scheduling-in-automotive-ECUs-9-320.jpg)