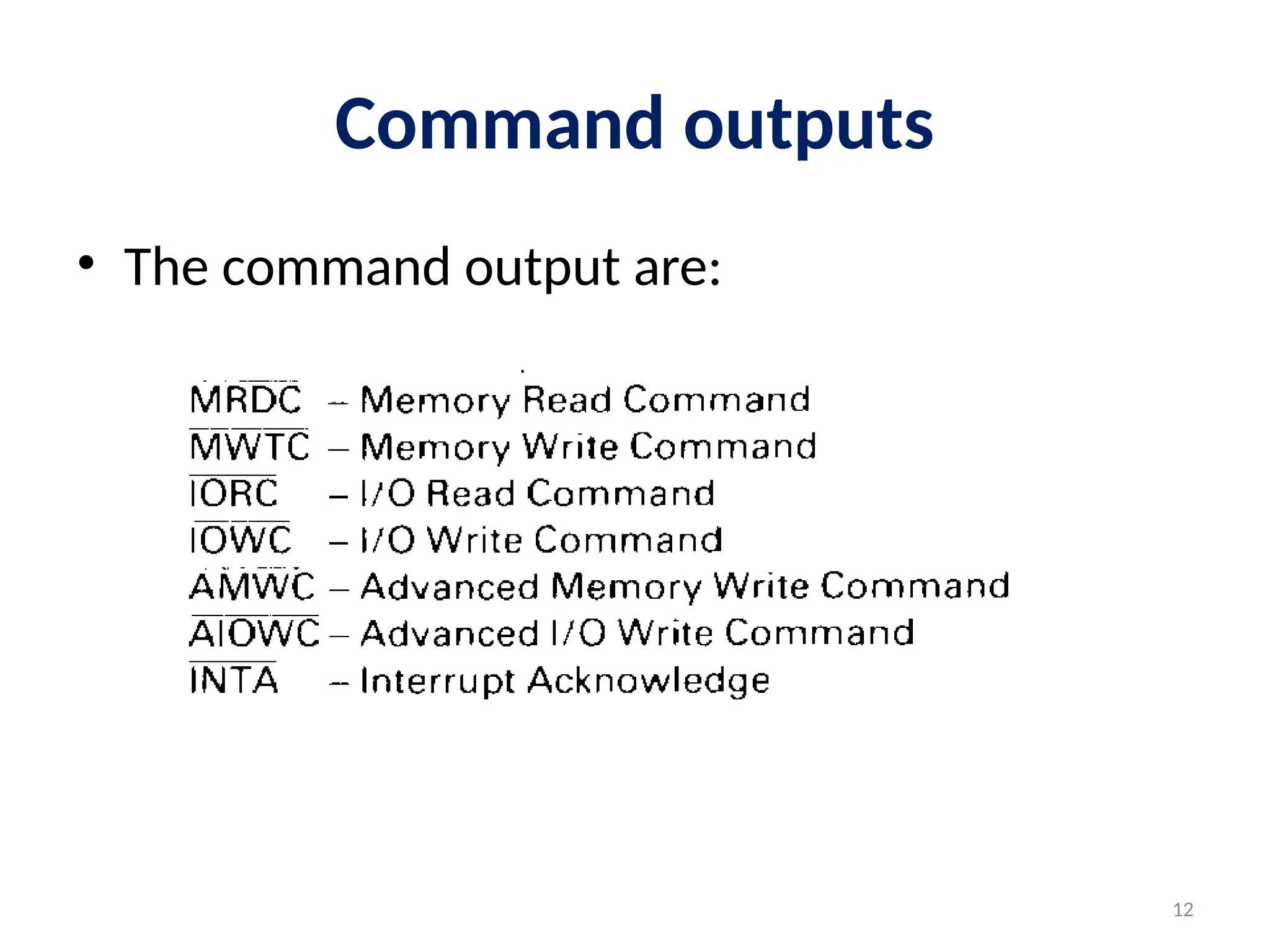

The 8288 bus controller is a 20-pin chip that facilitates control signals for the 8088/86 microprocessors in maximum mode, offering efficiency with 40% less power than standard controllers. It includes various command outputs, supports both I/O and system bus modes, and enables multiple master bus configurations. The document details its operational timing, signal functions, and how it integrates with the IBM PC architecture to manage data transfer between the CPU, memory, and peripheral devices.