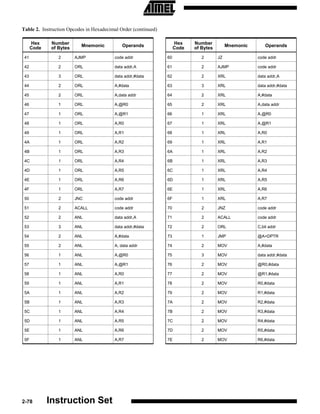

The microcontroller instruction set includes instructions for flow control, logic, arithmetic, and data movement. It supports operations on registers and direct or indirect addressed memory locations. The instruction set is encoded in an 8-bit format and includes operations that affect the processor status flags.

![Instruction Set

Microcontroller Instruction Set

For interrupt response time information, refer to the hardware description chapter.

(1)

Instructions that Affect Flag Settings

Instruction Flag Instruction Flag

C OV AC C OV AC

ADD X X X CLR C O

ADDC X X X CPL C X Instruction Set

SUBB X X X ANL C,bit X

MUL O X ANL C,/bit X

DIV O X ORL C,bit X

DA X ORL C, bit X

RRC X MOV C,bit X

RLC X CJNE X

SETB C 1

Note 1. Operations on SFR byte address 208 or bit addresses

209-215 (that is, the PSW or bits in the PSW) also

affect flag settings.

The Instruction Set and Addressing Modes

Rn Register R7-R0 of the currently selected Register Bank.

direct 8-bit internal data location’s address. This could be an Internal Data RAM location

(0-127) or a SFR [i.e., I/O port, control register, status register, etc. (128-255)].

@Ri 8-bit internal data RAM location (0-255) addressed indirectly through register R1or R0.

#data 8-bit constant included in instruction.

#data 16 16-bit constant included in instruction.

addr 16 16-bit destination address. Used by LCALL and LJMP. A branch can be anywhere within

the 64 Kbyte Program Memory address space.

addr 11 11-bit destination address. Used by ACALL and AJMP. The branch will be within the

same 2 Kbyte page of program memory as the first byte of the following instruction.

rel Signed (two’s complement) 8-bit offset byte. Used by SJMP and all conditional jumps.

Range is -128 to +127 bytes relative to first byte of the following instruction.

bit Direct Addressed bit in Internal Data RAM or Special Function Register.

0509A

2-71](https://image.slidesharecdn.com/setinstrucciones1-111211095113-phpapp02/75/Microcontroller-Instruction-Set-1-2048.jpg)

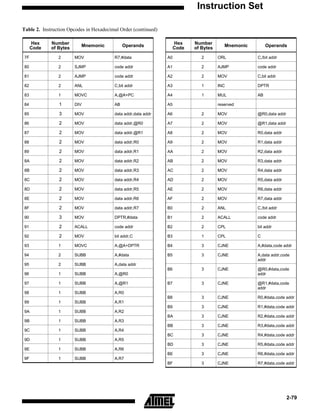

![Instruction Set Summary

0 1 2 3 4 5 6 7

JBC JB JNB JC JNC JZ JNZ

0 NOP bit,rel bit, rel bit, rel rel rel rel rel

[3B, 2C] [3B, 2C] [3B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C]

AJMP ACALL AJMP ACALL AJMP ACALL AJMP ACALL

1 (P0) (P0) (P1) (P1) (P2) (P2) (P3) (P3)

[2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C]

LJMP LCALL ORL ANL XRL ORL

RET RETI

2 addr16 addr16 dir, A dir, A dir, a C, bit

[2C] [2C]

[3B, 2C] [3B, 2C] [2B] [2B] [2B] [2B, 2C]

ORL ANL XRL JMP

RR RRC RL RLC

3 dir, #data dir, #data dir, #data @A + DPTR

A A A A

[3B, 2C] [3B, 2C] [3B, 2C] [2C]

ADD ADDC ORL ANL XRL MOV

INC DEC

4 A, #data A, #data A, #data A, #data A, #data A, #data

A A

[2B] [2B] [2B] [2B] [2B] [2B]

INC DEC ADD ADDC ORL ANL XRL MOV

5 dir dir A, dir A, dir A, dir A, dir A, dir dir, #data

[2B] [2B] [2B] [2B] [2B] [2B] [2B] [3B, 2C]

MOV

INC DEC ADD ADDC ORL ANL XRL

6 @R0, @data

@R0 @R0 A, @R0 A, @R0 A, @R0 A, @R0 A, @R0

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

7 @R1, #data

@R1 @R1 A, @R1 A, @R1 A, @R1 A, @R1 A, @R1

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

8 R0, #data

R0 R0 A, R0 A, R0 A, R0 A, R0 A, R0

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

9 R1, #data

R1 R1 A, R1 A, R1 A, R1 A, R1 A, R1

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

A R2, #data

R2 R2 A, R2 A, R2 A, R2 A, R2 A, R2

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

B R3, #data

R3 R3 A, R3 A, R3 A, R3 A, R3 A, R3

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

C R4, #data

R4 R4 A, R4 A, R4 A, R4 A, R4 A, R4

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

D R5, #data

R5 R5 A, R5 A, R5 A, R5 A, R5 A, R5

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

E R6, #data

R6 R6 A, R6 A, R6 A, R6 A, R6 A, R6

[2B]

MOV

INC DEC ADD ADDC ORL ANL XRL

F R7, #data

R7 R7 A, R7 A, R7 A, R7 A, R7 A, R7

[2B]

Key:

[2B] = 2 Byte, [3B] = 3 Byte, [2C] = 2 Cycle, [4C] = 4 Cycle, Blank = 1 byte/1 cycle

2-72 Instruction Set](https://image.slidesharecdn.com/setinstrucciones1-111211095113-phpapp02/85/Microcontroller-Instruction-Set-2-320.jpg)

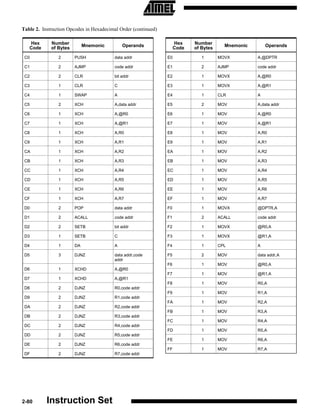

![Instruction Set

Instruction Set Summary (Continued)

8 9 A B C D E F

MOV

SJMP ORL ANL PUSH POP MOVX A, MOVX

DPTR,#

0 REL C, /bit C, /bit dir dir @DPTR @DPTR, A

data 16

[2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2C] [2C]

[3B, 2C]

AJMP ACALL AJMP ACALL AJMP ACALL AJMP ACALL

1 (P4) (P4) (P5) (P5) (P6) (P6) (P7) (P7)

[2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C] [2B, 2C]

ANL MOV MOV CPL CLR SETB MOVX MOVX

2 C, bit bit, C C, bit bit bit bit A, @R0 wR0, A

[2B, 2C] [2B, 2C] [2B] [2B] [2B] [2B] [2C] [2C]

MOVC A, MOVC A, INC MOVX MOVX

CPL CLR SETB

3 @A + PC @A + DPTR DPTR A, @RI @RI, A

C C C

[2C] [2C] [2C] [2C] [2C]

DIV SUBB MUL CJNE A,

SWAP DA CLR CPL

4 AB A, #data AB #data, rel

A A A A

[2B, 4C] [2B] [4C] [3B, 2C]

MOV SUBB CJNE XCH DJNZ MOV MOV

5 dir, dir A, dir A, dir, rel A, dir dir, rel A, dir dir, A

[3B, 2C] [2B] [3B, 2C] [2B] [3B, 2C] [2B] [2B]

CJNE

MOV MOV

SUBB @R0, #data, XCH XCHD MOV MOV

6 dir, @R0 @R0, dir

A, @R0 rel A, @R0 A, @R0 A, @R0 @R0, A

[2B, 2C] [2B, 2C]

[3B, 2C]

CJNE

MOV MOV

SUBB @R1, #data, XCH XCHD MOV MOV

7 dir, @R1 @R1, dir

A, @R1 rel A, @R1 A, @R1 A, @R1 @R1, A

[2B, 2C] [2B, 2C]

[3B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

8 dir, R0 R0, dir R0, #data, rel R0, rel

A, R0 A, R0 A, R0 R0, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

9 dir, R1 R1, dir R1, #data, rel R1, rel

A, R1 A, R1 A, R1 R1, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

A dir, R2 R2, dir R2, #data, rel R2, rel

A, R2 A, R2 A, R2 R2, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

B dir, R3 R3, dir R3, #data, rel R3, rel

A, R3 A, R3 A, R3 R3, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

C dir, R4 R4, dir R4, #data, rel R4, rel

A, R4 A, R4 A, R4 R4, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

D dir, R5 R5, dir R5, #data, rel R5, rel

A, R5 A, R5 A, R5 R5, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

E dir, R6 R6, dir R6, #data, rel R6, rel

A, R6 A, R6 A, R6 R6. A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

MOV MOV CJNE DJNZ

SUBB XCH MOV MOV

F dir, R7 R7, dir R7, #data, rel R7, rel

A, R7 A, R7 A, R7 R7, A

[2B, 2C] [2B, 2C] [3B, 2C] [2B, 2C]

Key:

[2B] = 2 Byte, [3B] = 3 Byte, [2C] = 2 Cycle, [4C] = 4 Cycle, Blank = 1 byte/1 cycle

2-73](https://image.slidesharecdn.com/setinstrucciones1-111211095113-phpapp02/85/Microcontroller-Instruction-Set-3-320.jpg)