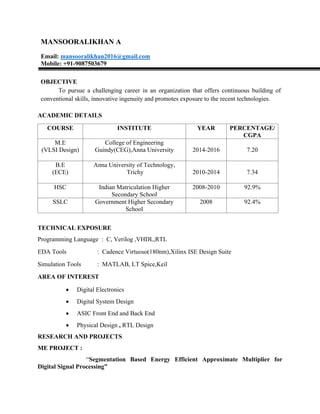

Mansoor Ali Khan is seeking a challenging career in a technology-focused organization and has a solid academic background, holding an M.E. in VLSI Design and a B.E. in Electronics. He has experience in digital electronics, ASCI design, and relevant programming languages, with notable projects that focus on energy-efficient circuits and security enhancements in AES engines. Additionally, his work has been published in a reputable journal, and he is proficient in English and Tamil.