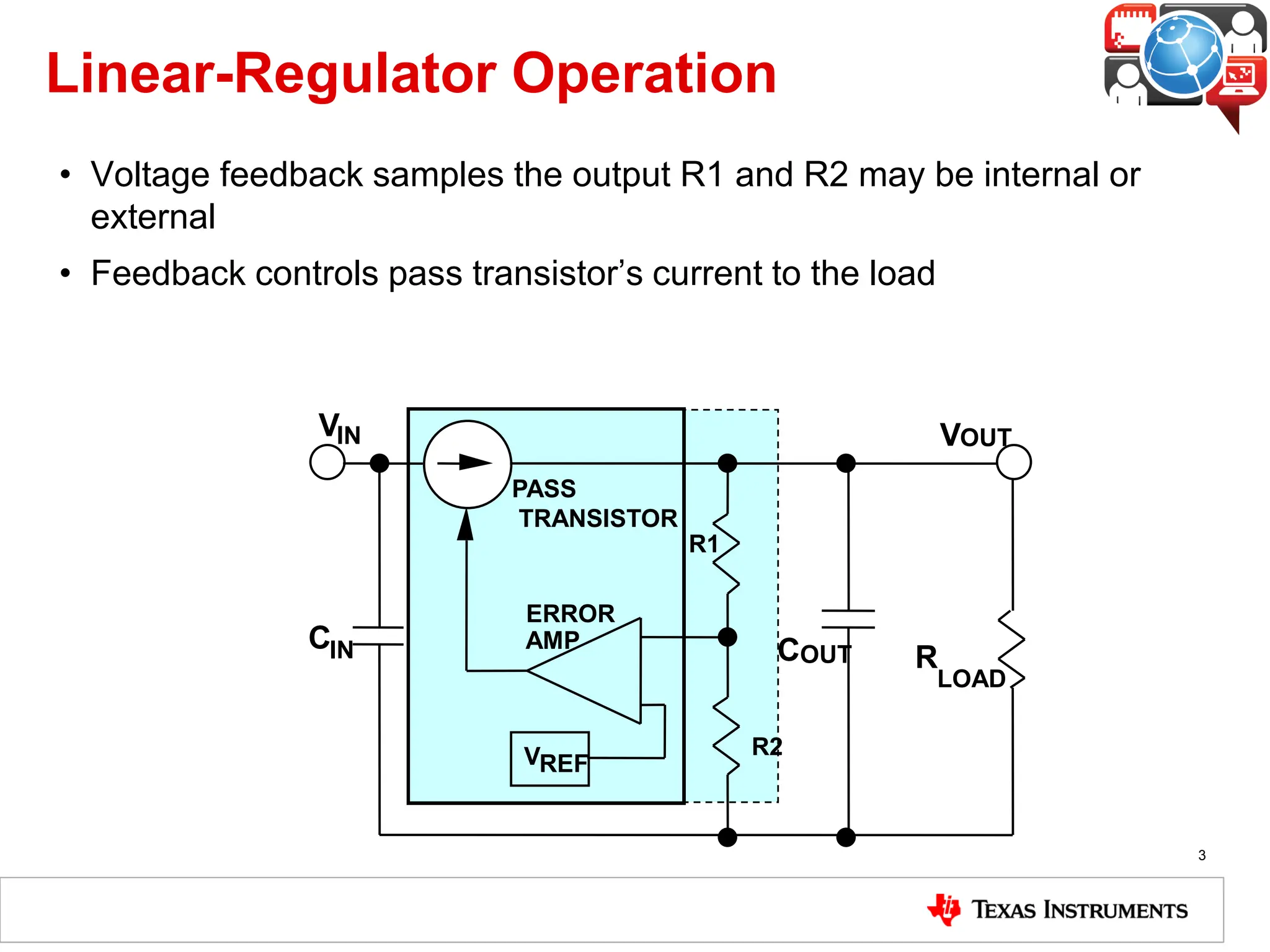

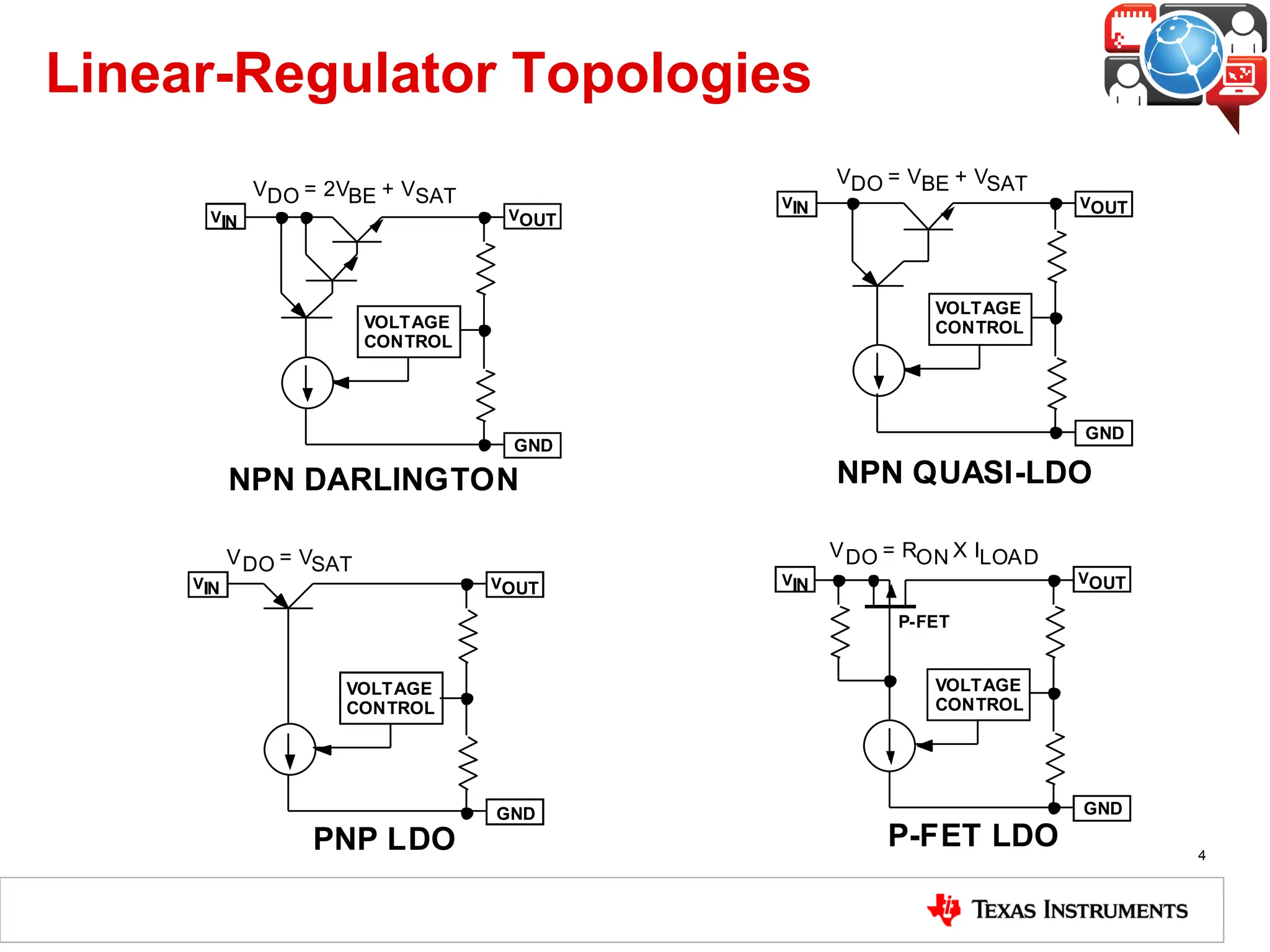

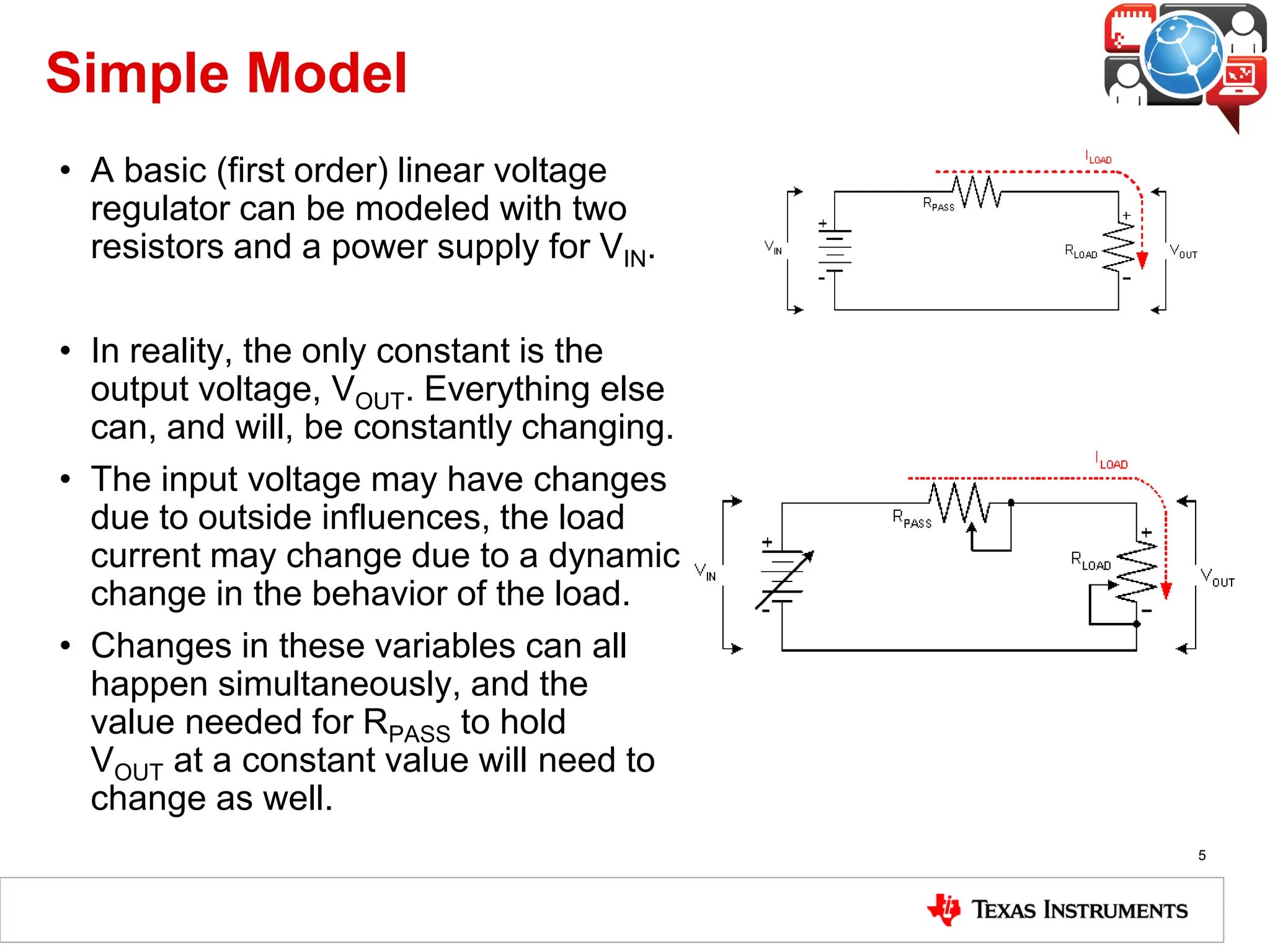

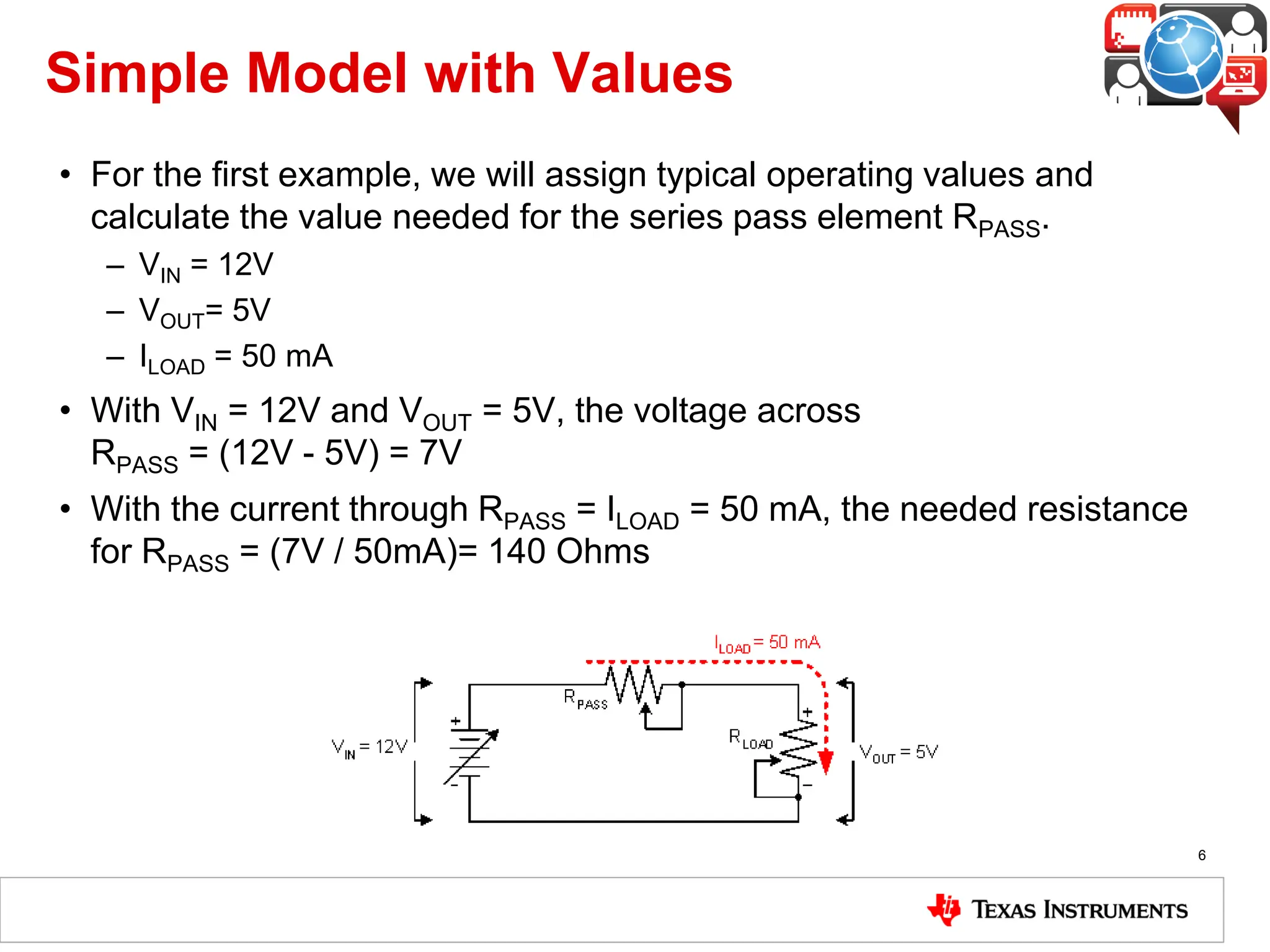

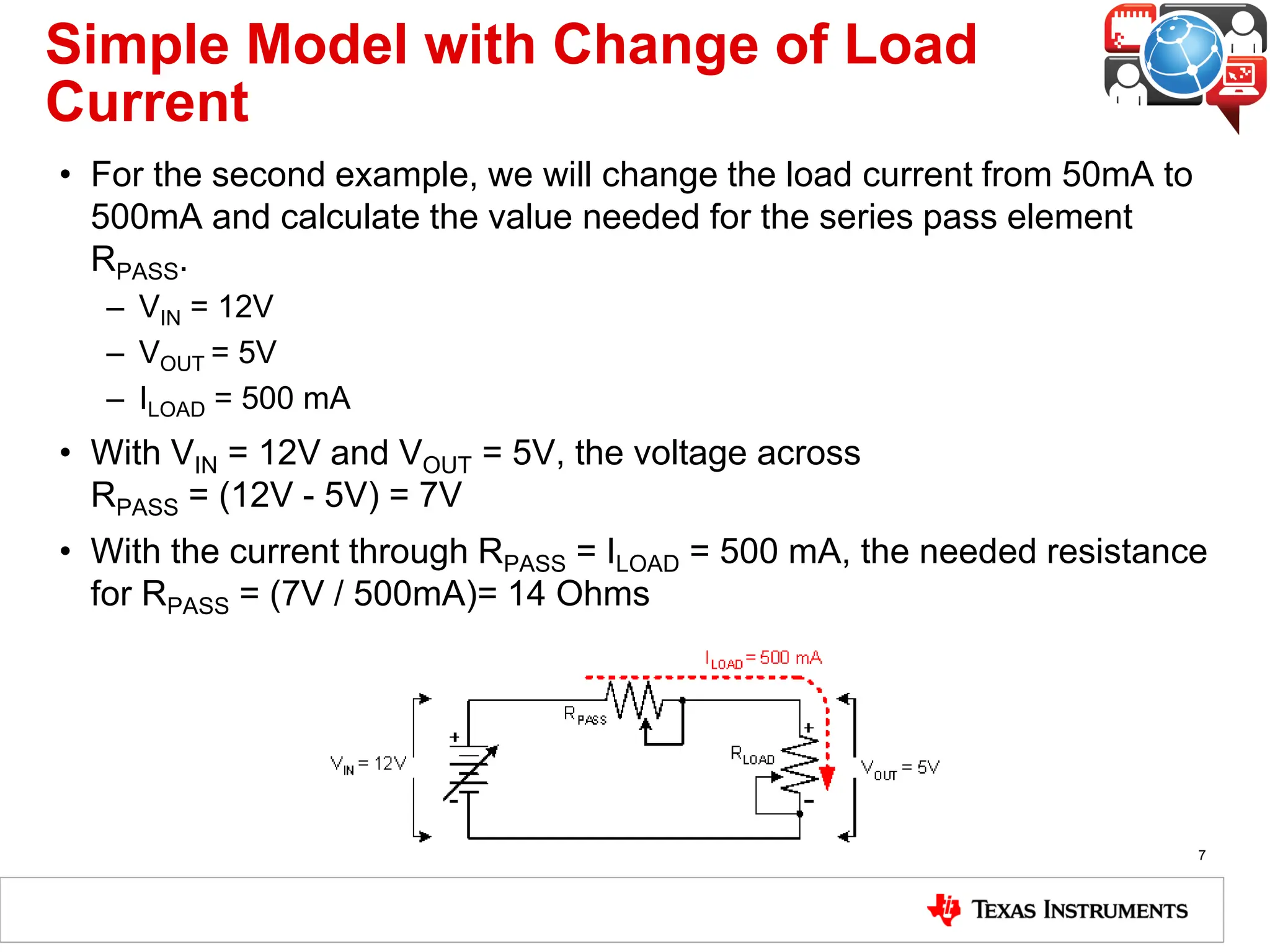

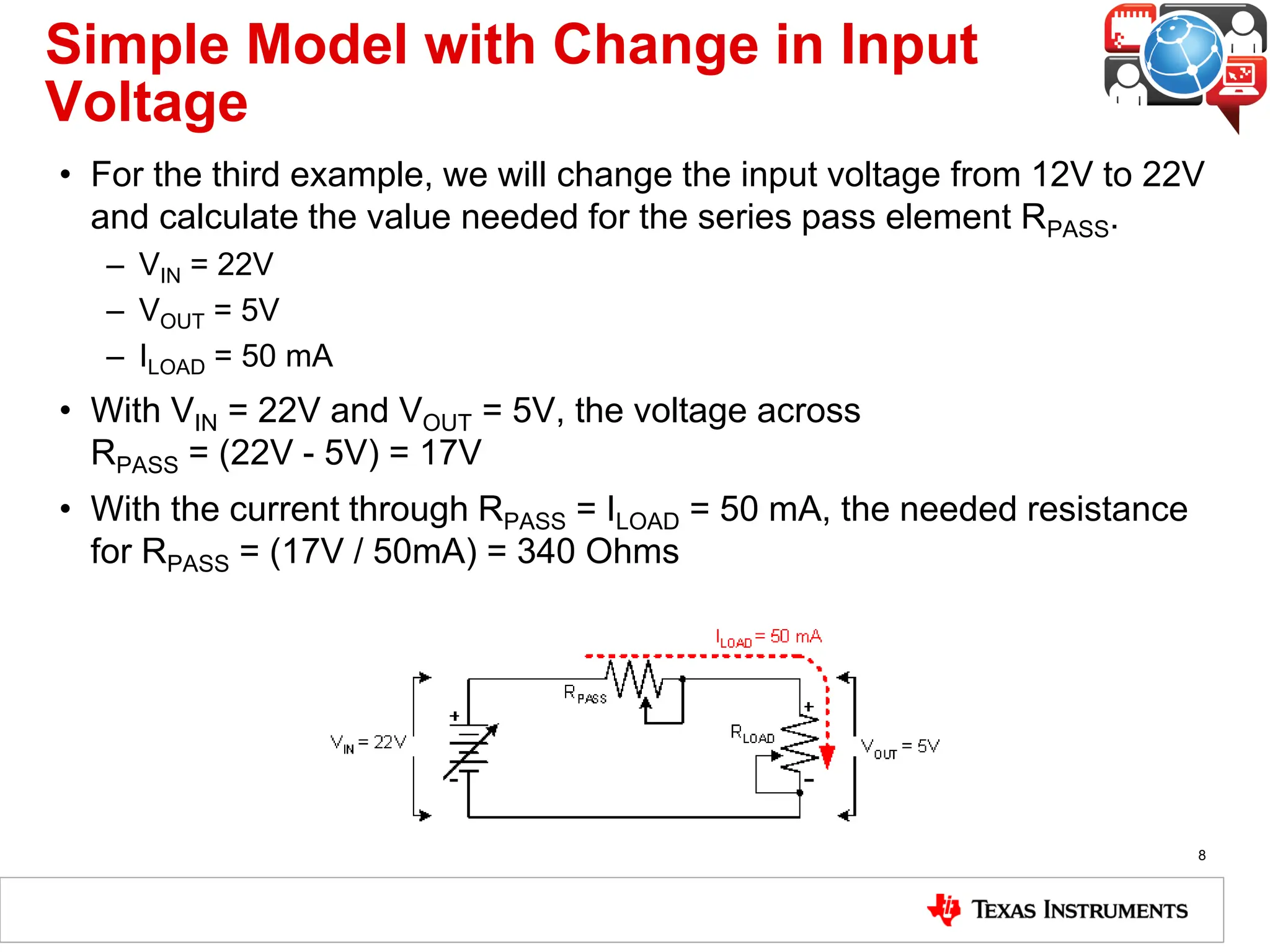

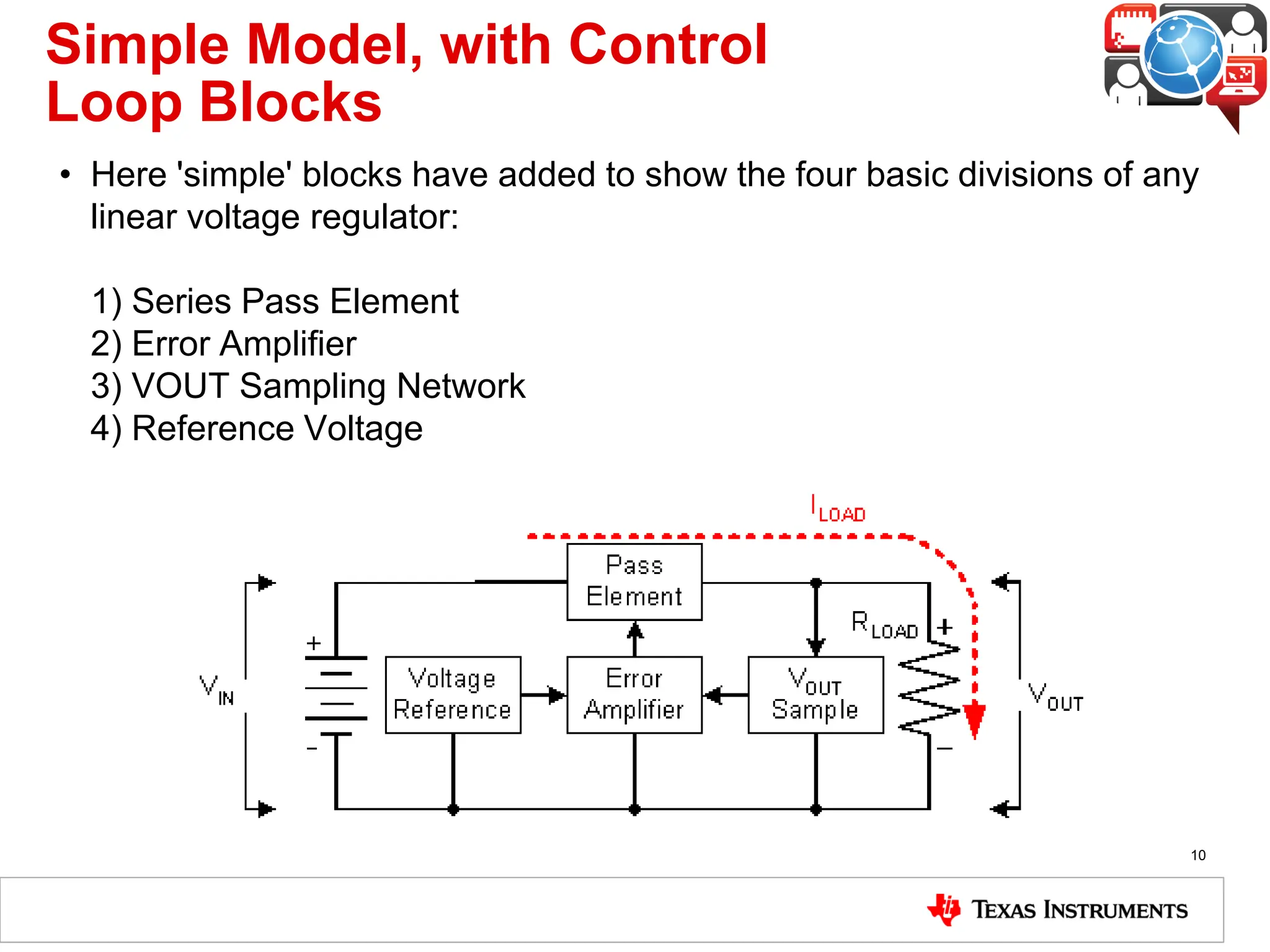

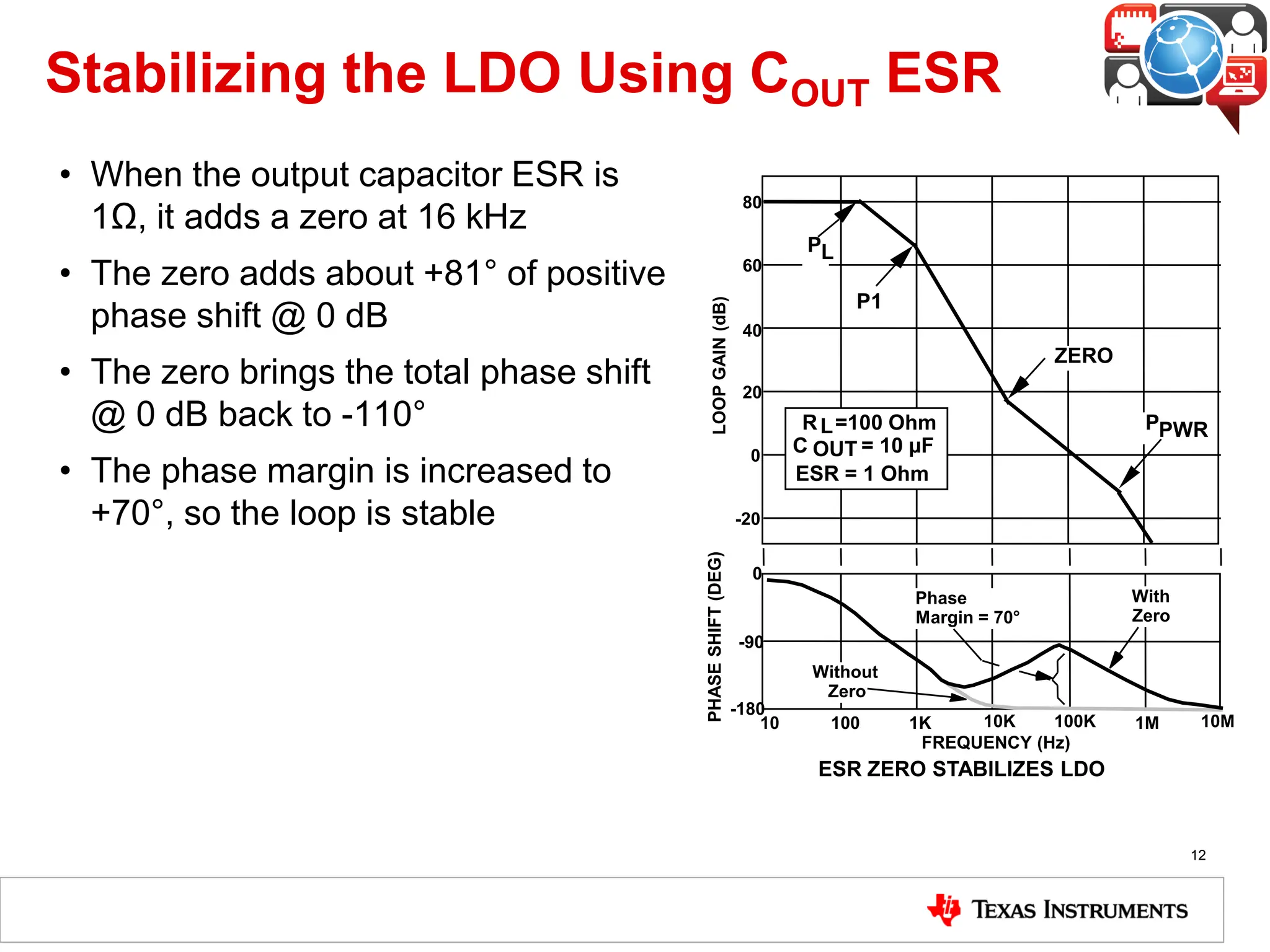

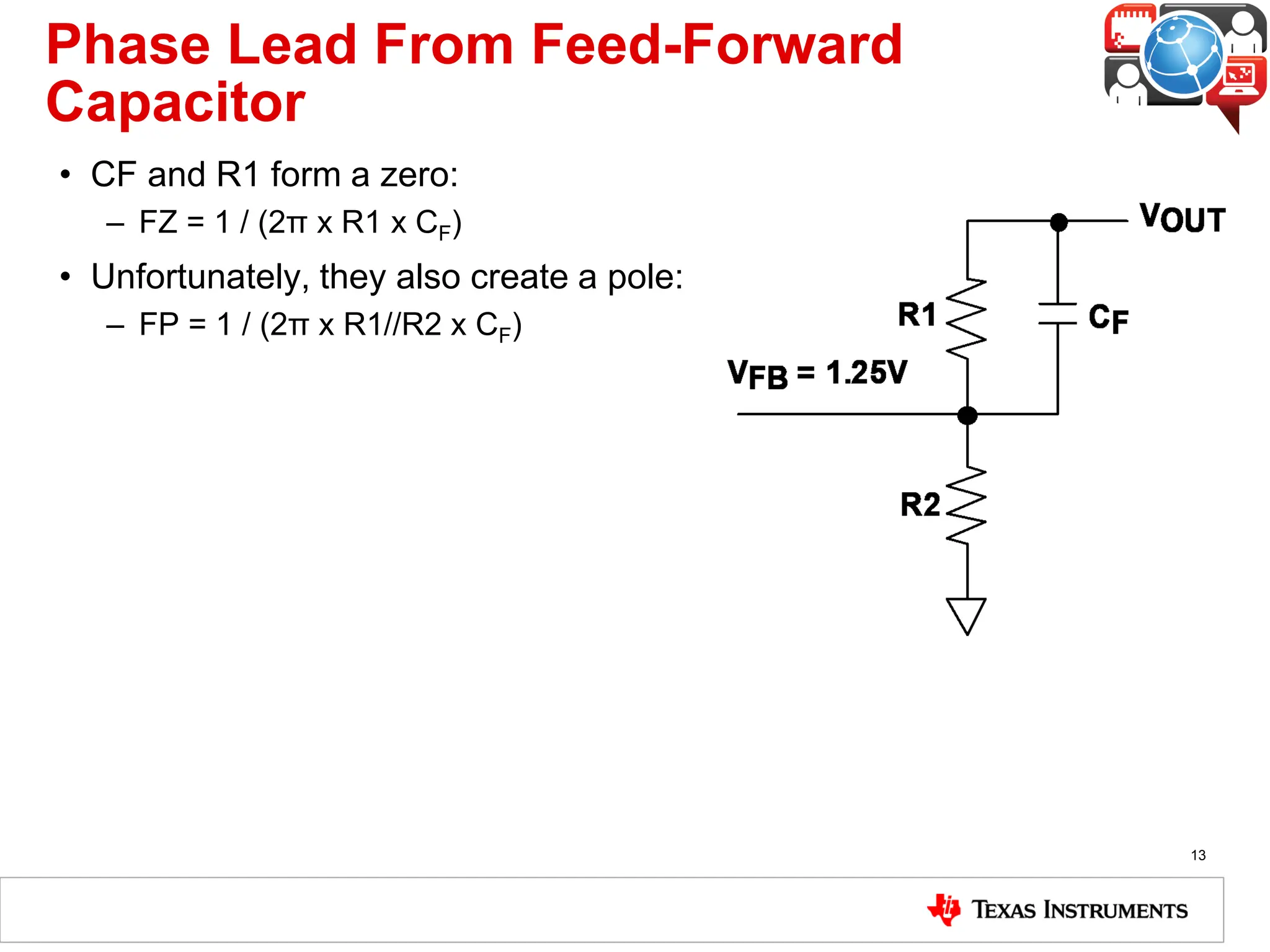

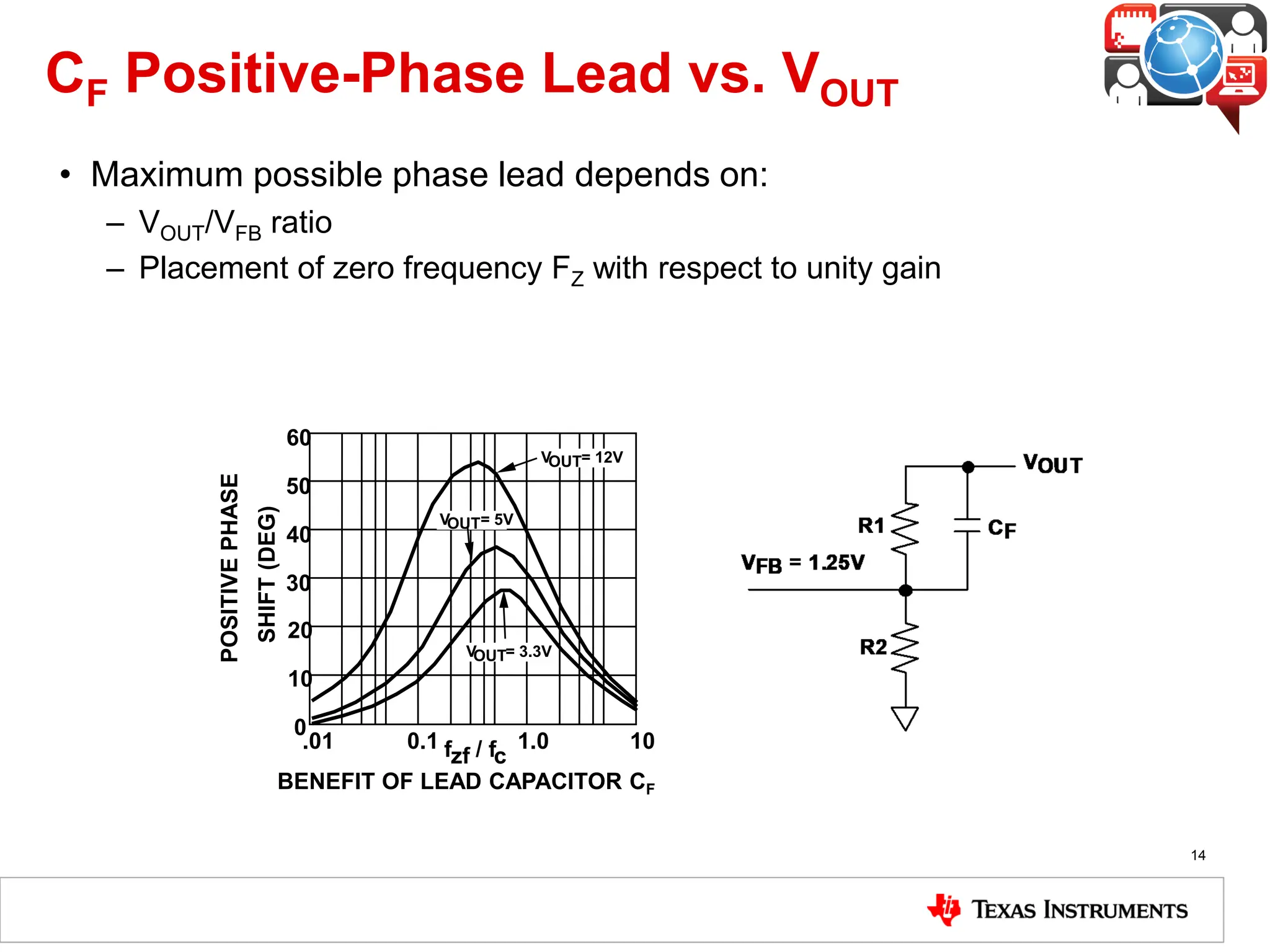

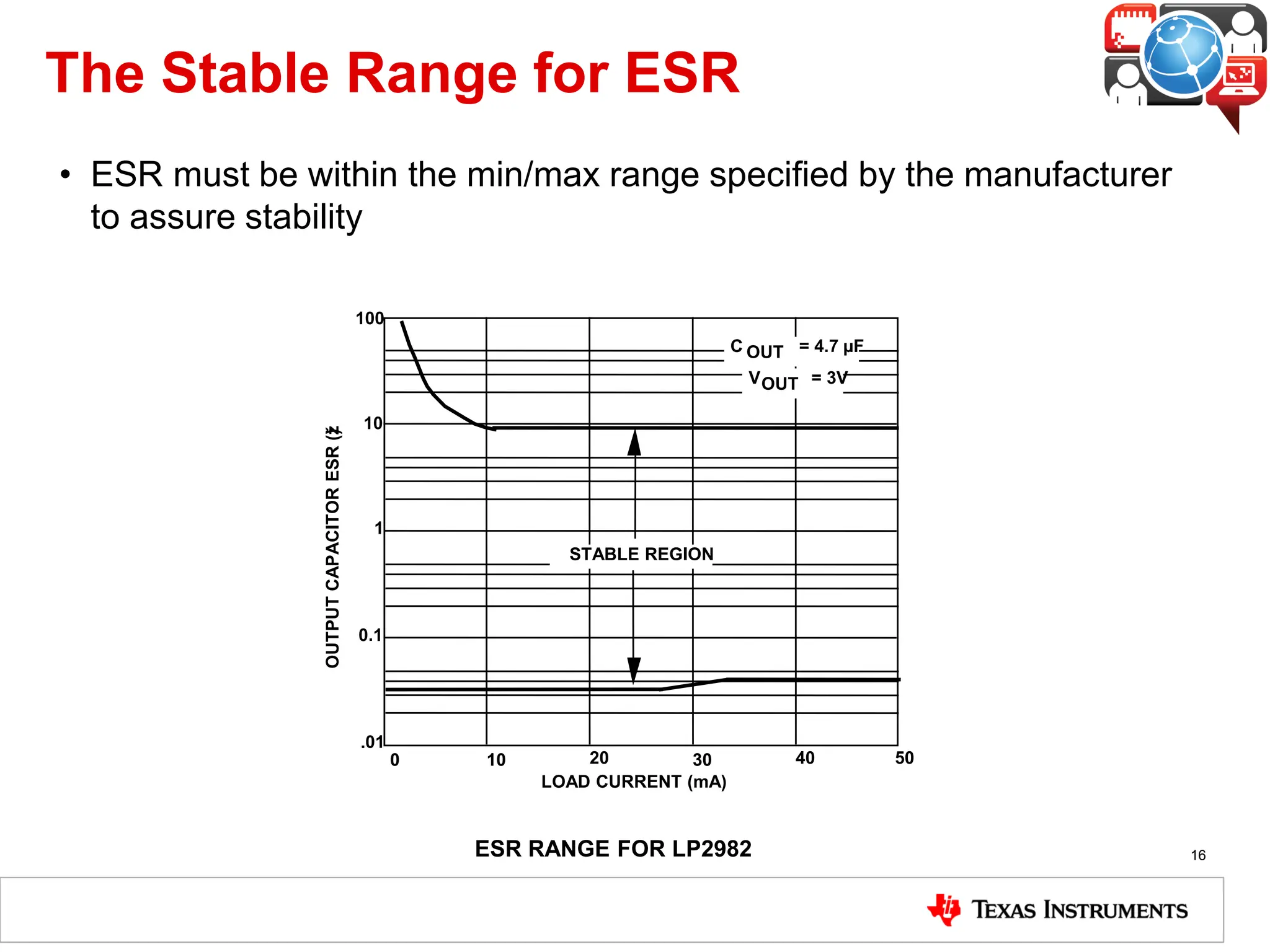

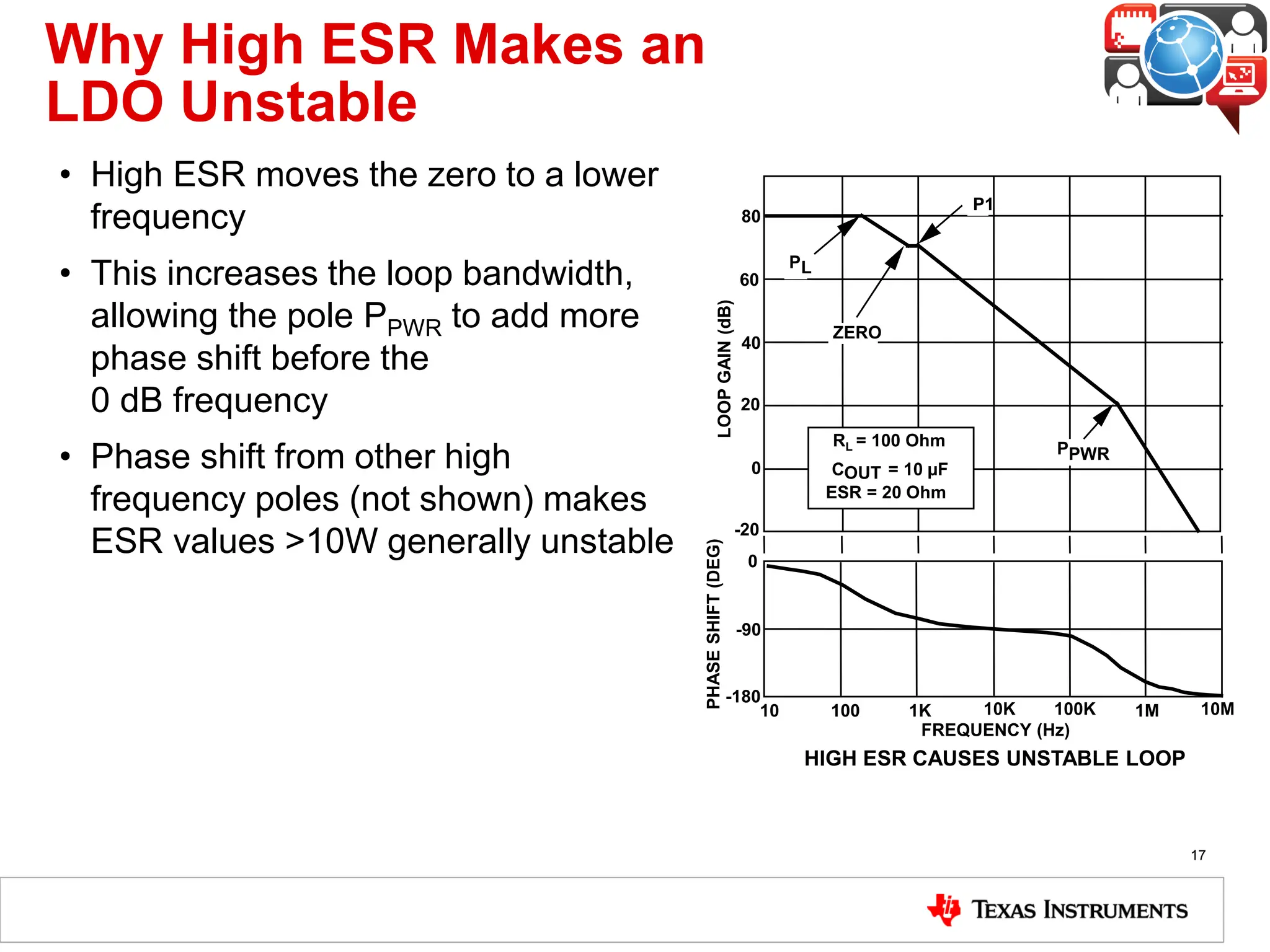

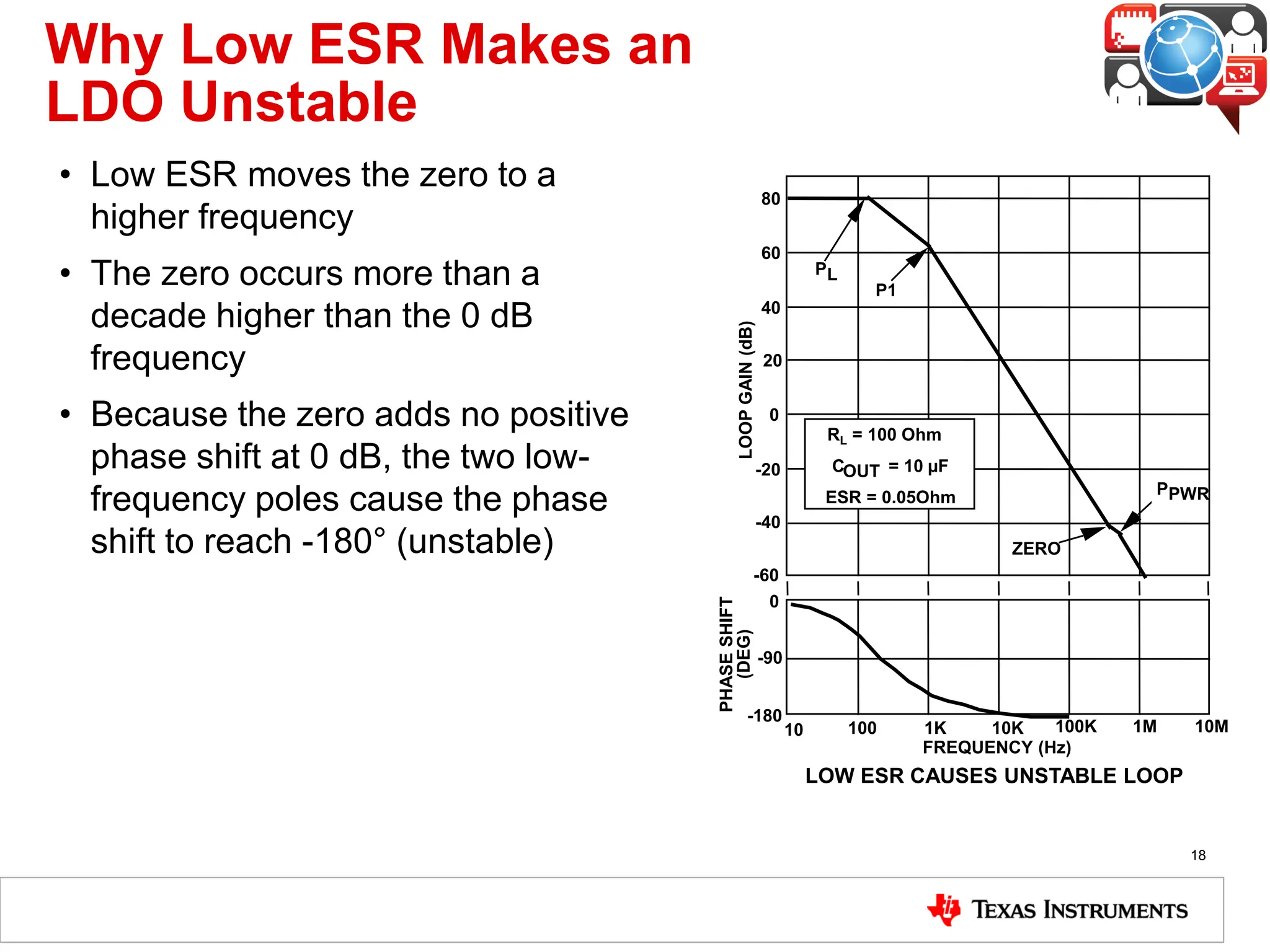

The document covers the fundamentals and operation of linear voltage regulators, detailing their types and the working of components such as control loops, error amplifiers, and pass transistors. It explains how output voltage is maintained through feedback mechanisms and provides examples illustrating calculations related to load current and input voltage variations. Additionally, the importance of output capacitor equivalent series resistance (ESR) for stability and potential causes of oscillation due to ESR values is discussed.