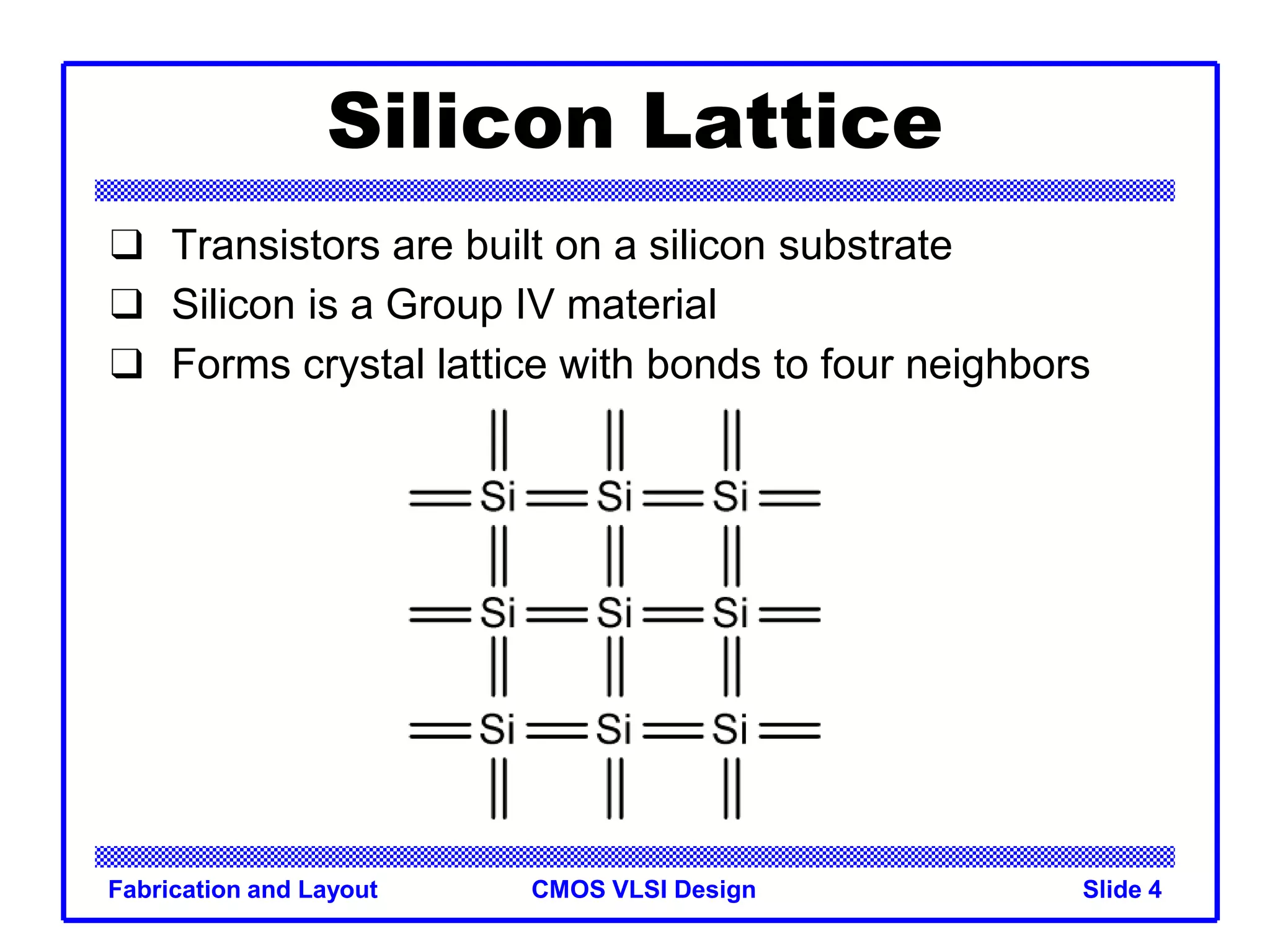

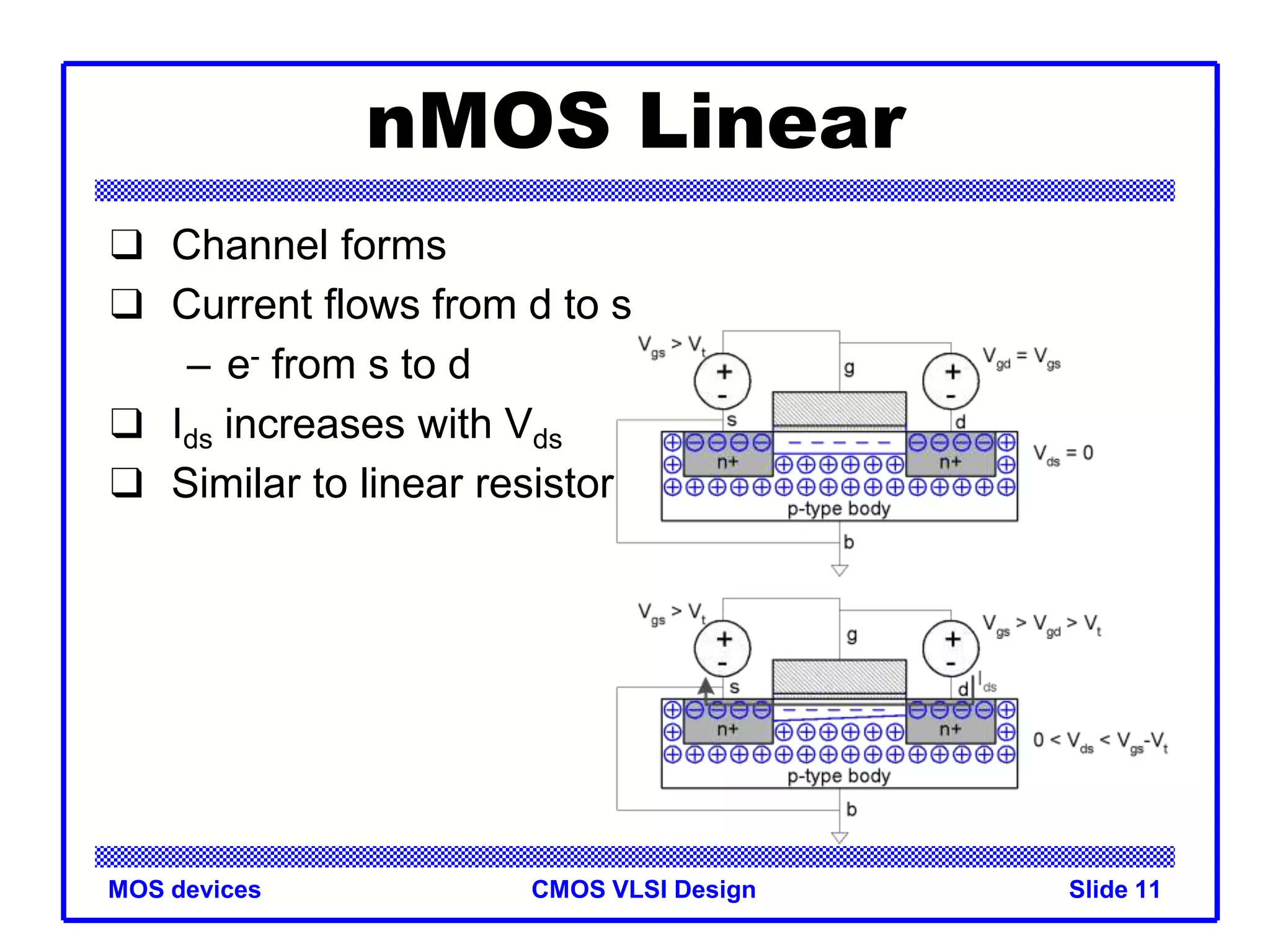

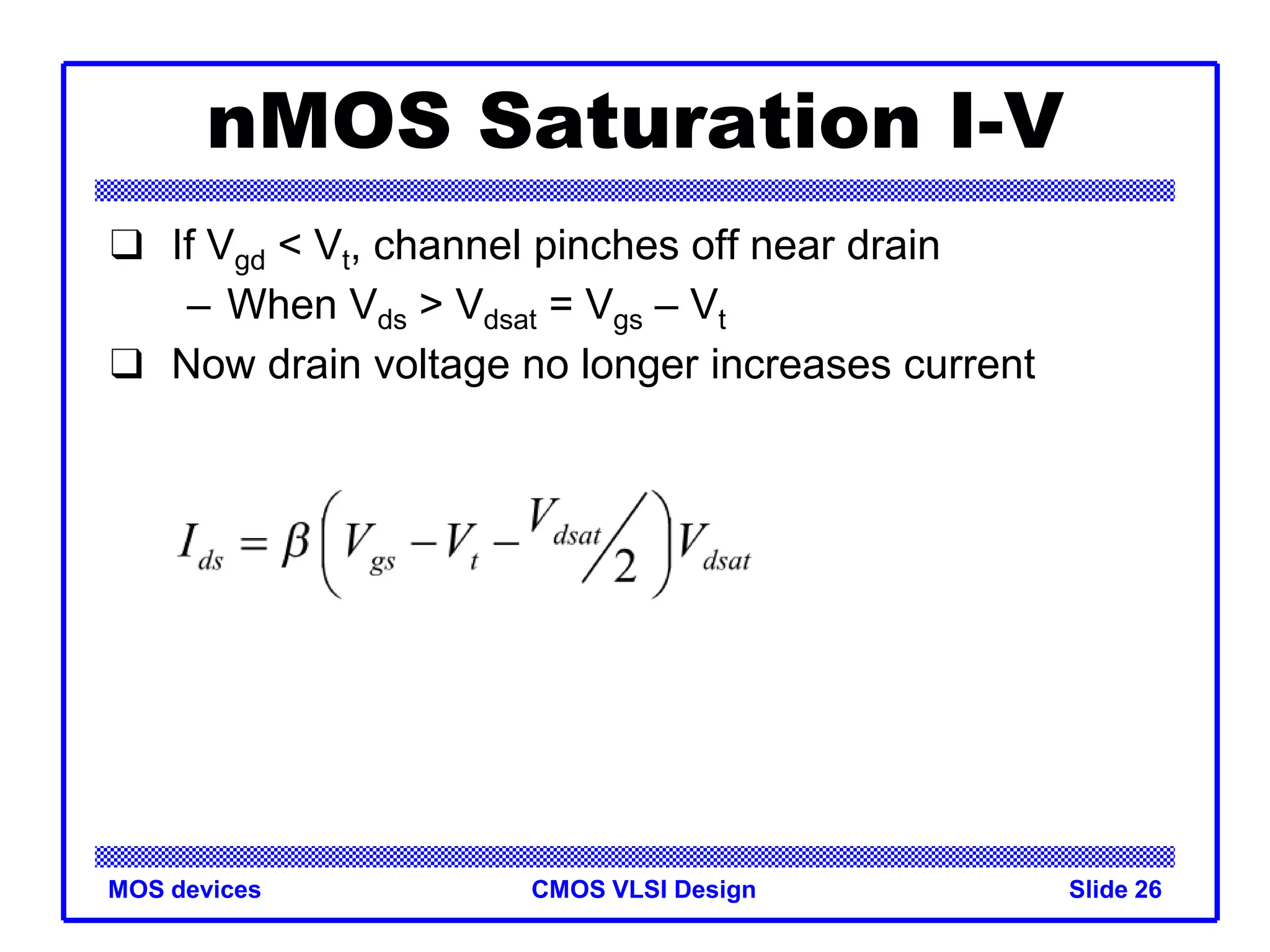

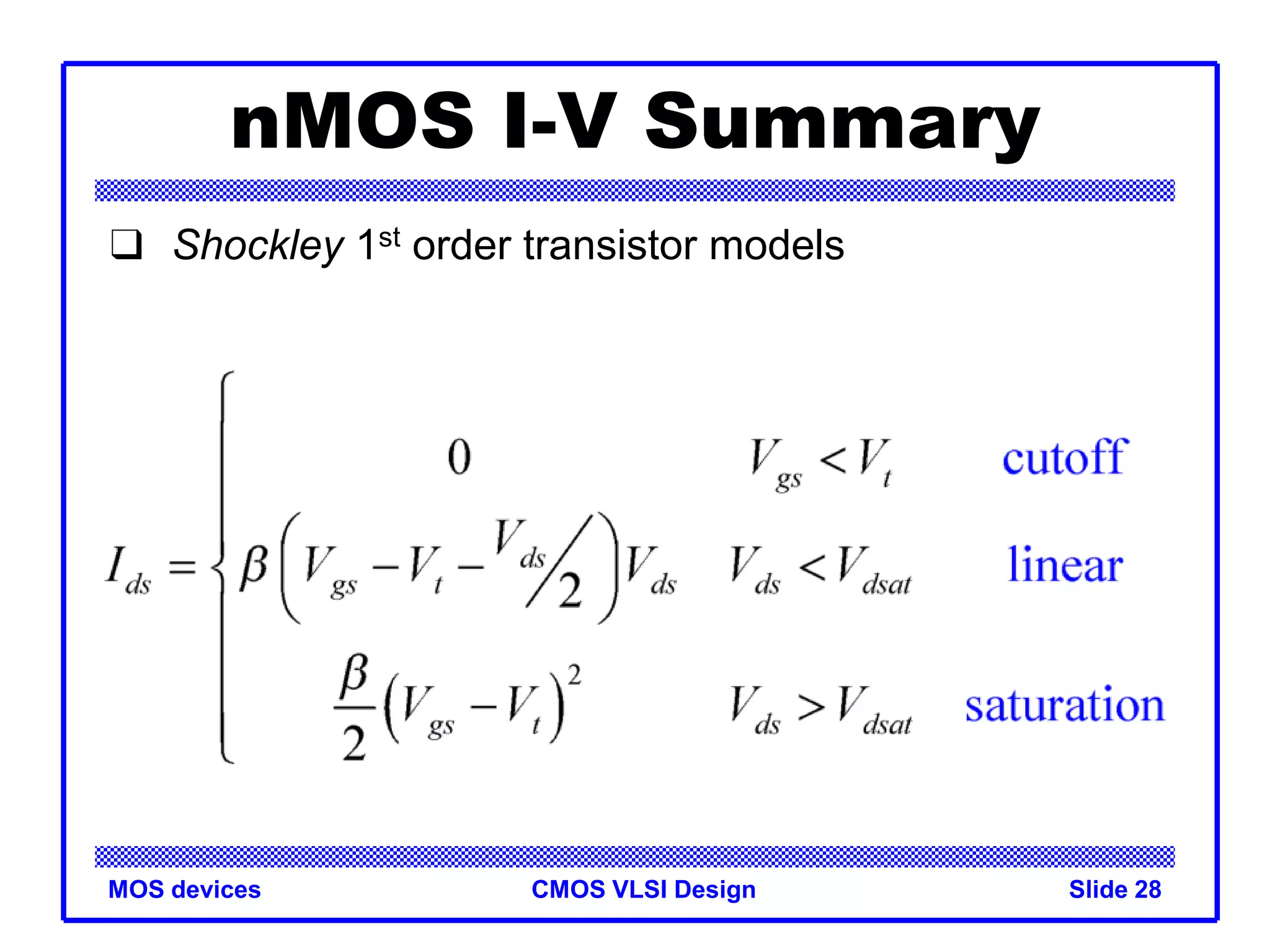

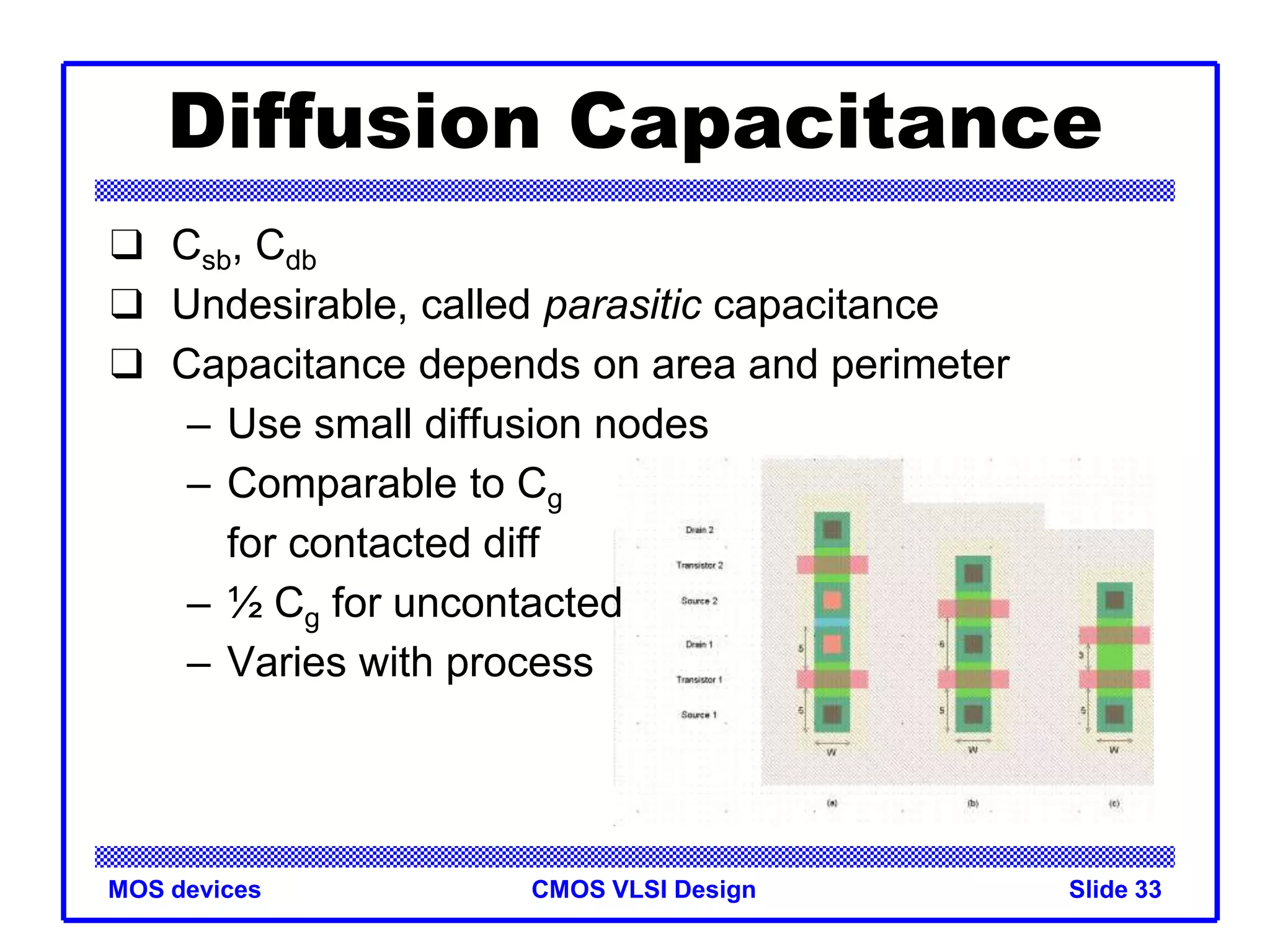

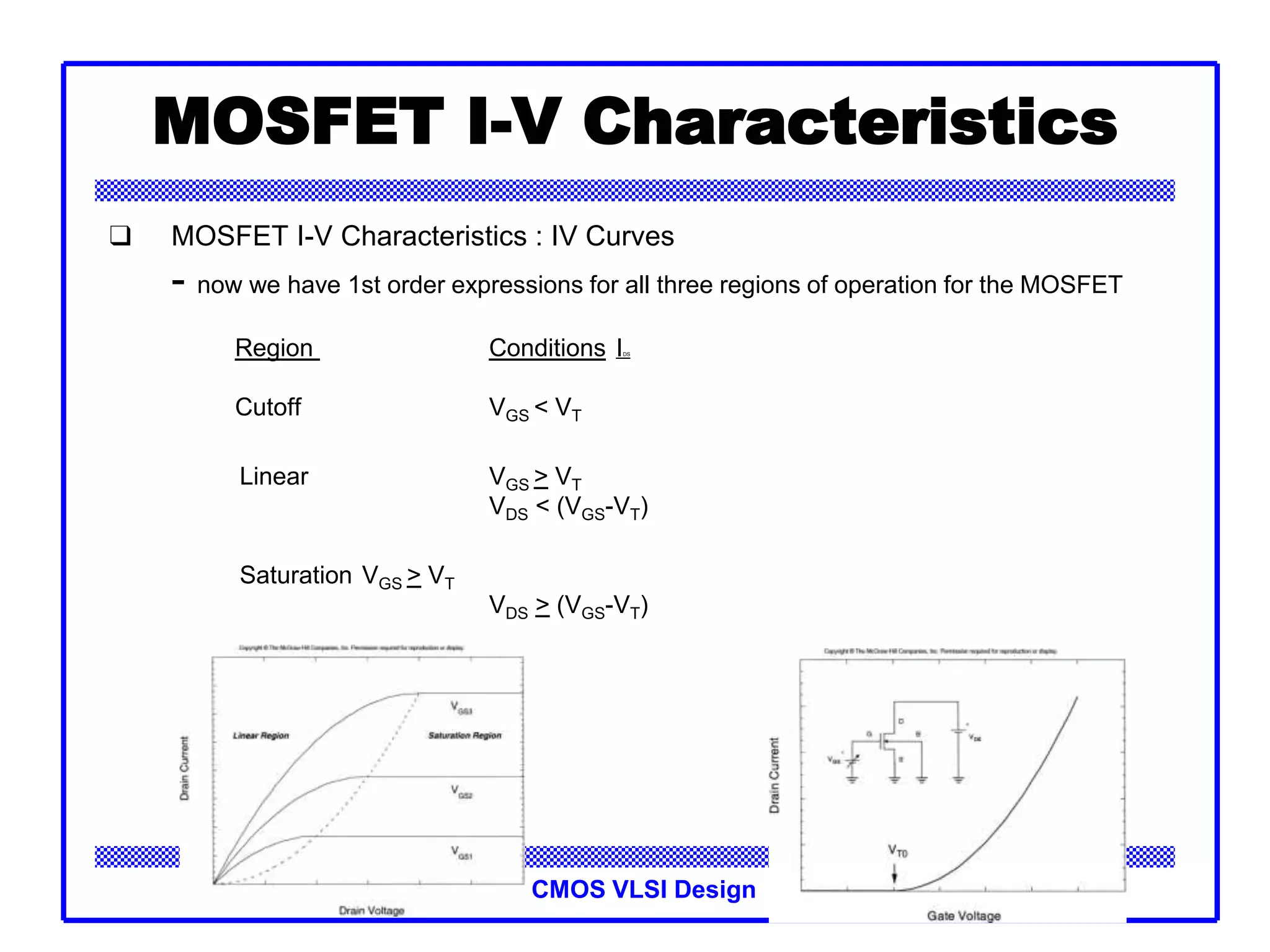

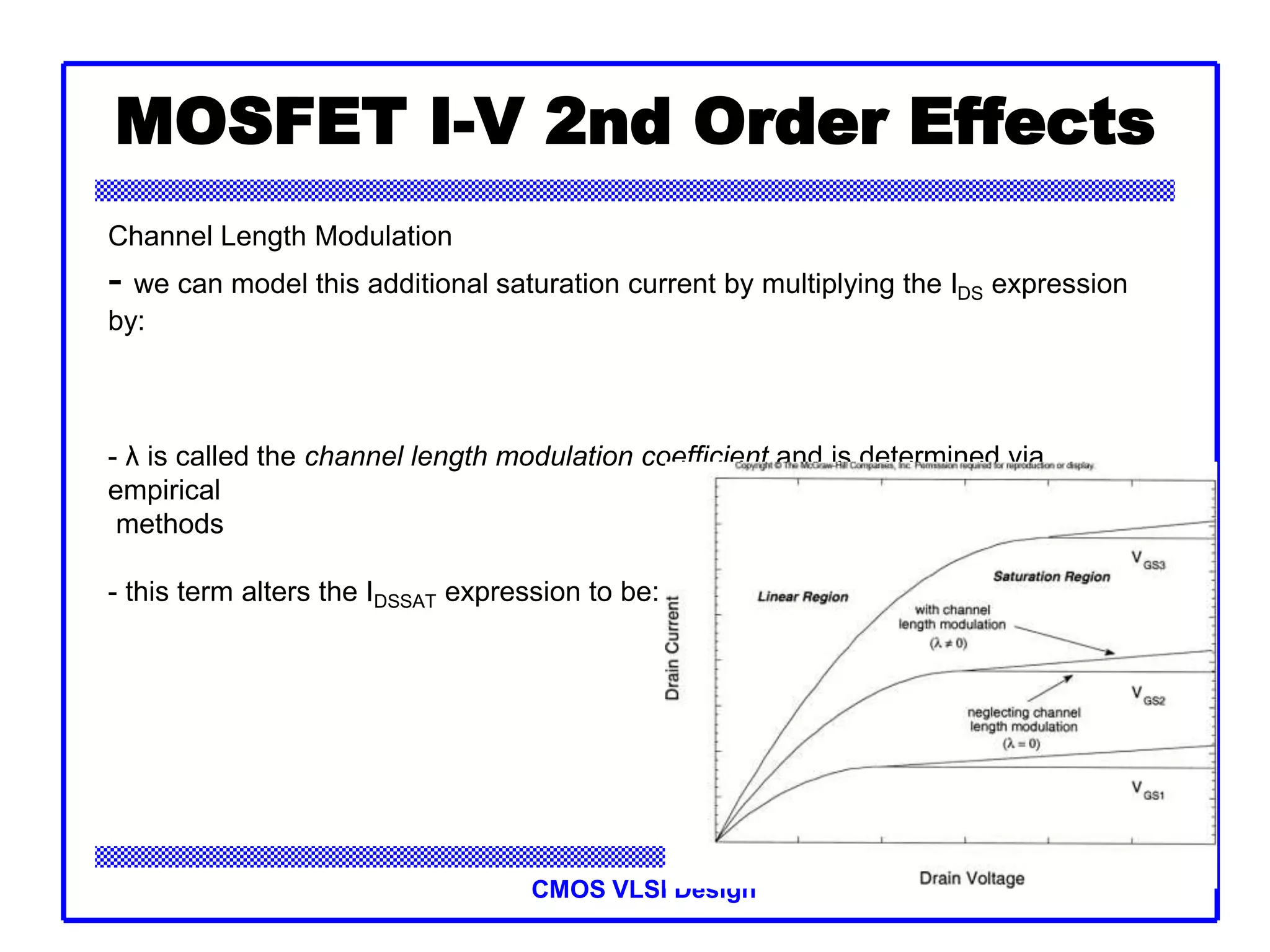

The document provides an introduction to CMOS VLSI design, covering MOS transistor theory and fabrication/layout. It discusses how MOS transistors are built on a silicon substrate using dopants to introduce carriers. The key modes of a MOS capacitor are described. Terminal voltages and regions of operation (cutoff, linear, saturation) for nMOS and pMOS transistors are explained. Equations are derived for channel charge, carrier velocity, and linear/saturation current-voltage characteristics. Second-order effects like channel length modulation and substrate bias are also covered.