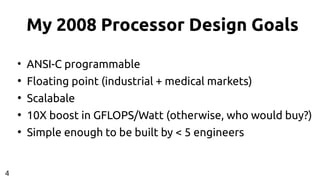

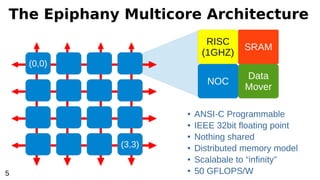

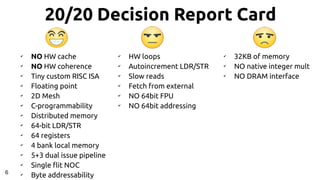

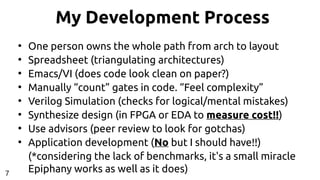

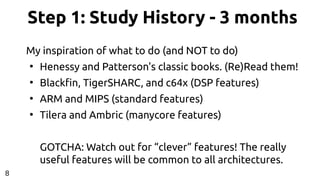

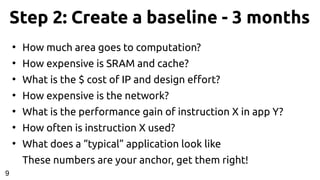

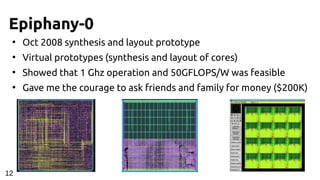

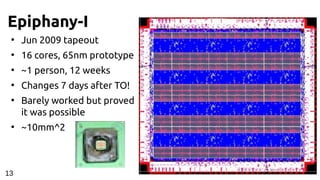

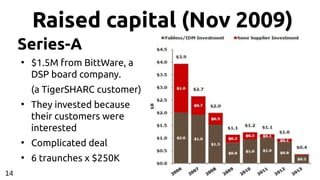

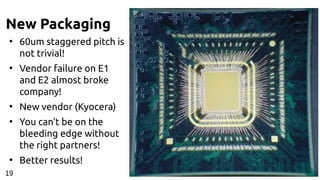

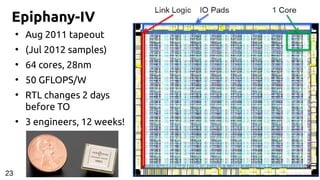

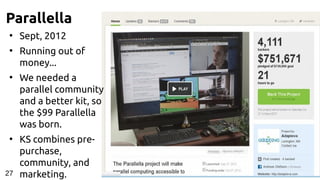

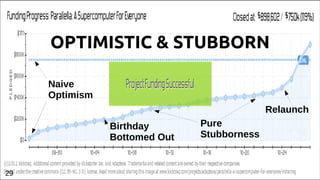

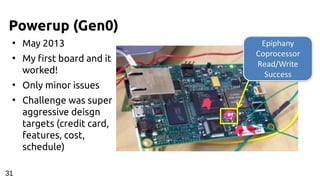

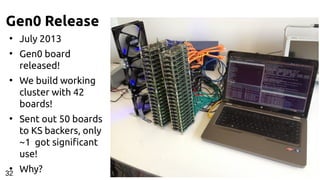

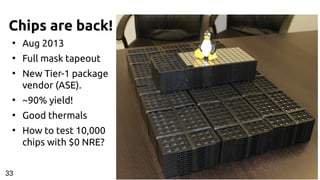

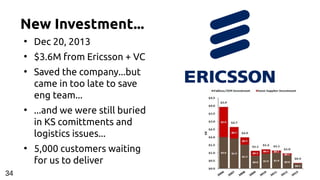

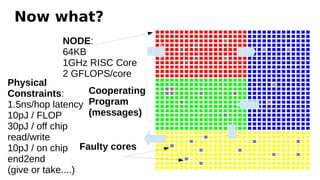

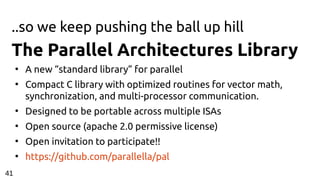

The document details the journey of designing a parallel processor from scratch, highlighting key insights such as the efficiency of specialized processors over general-purpose ones, and the author's experiences with various prototypes and iterations. It emphasizes the importance of a strong team and collaborations with vendors, as well as the lessons learned about development, software needs, and market challenges. Ultimately, it presents a vision for the future of parallel computing and the role of architectures like Epiphany in that landscape.