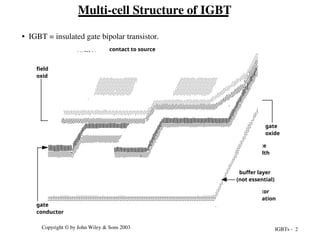

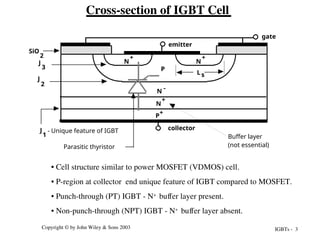

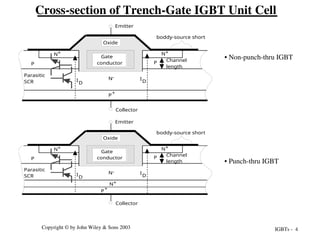

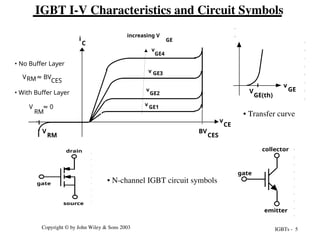

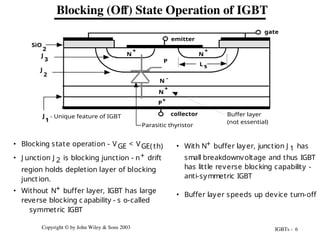

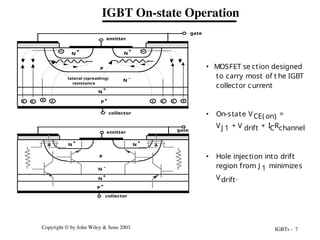

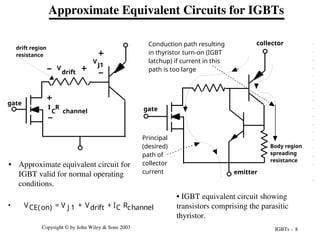

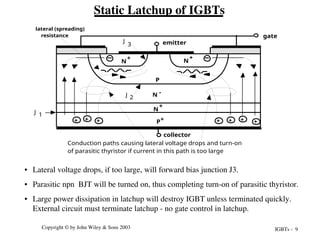

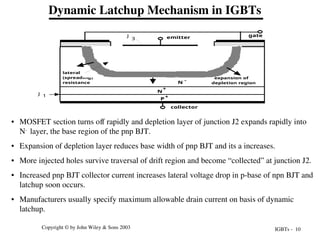

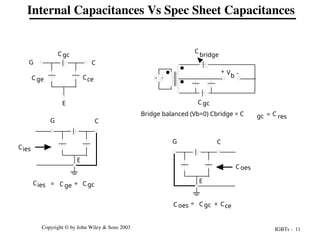

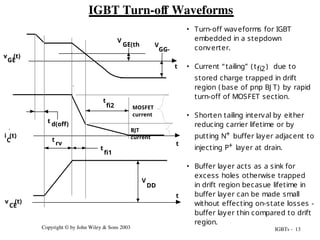

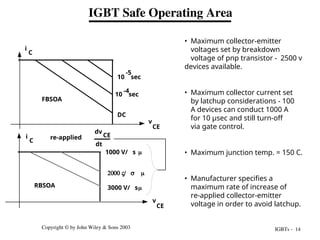

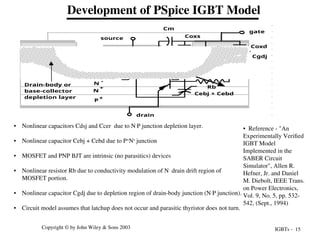

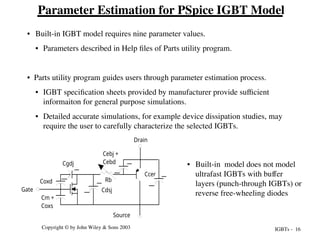

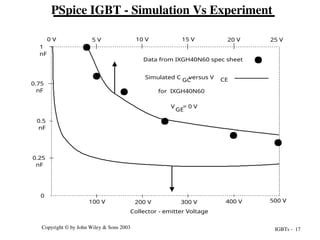

The document provides a comprehensive overview of Insulated Gate Bipolar Transistors (IGBTs), detailing their construction, operating principles, and characteristics, including both switching and blocking states. It discusses the advantages and limitations of various IGBT configurations, including punch-through and non-punch-through types, and presents information on PSPICE simulation models for IGBTs. Key topics also include the dynamics of latchup and safe operating areas for IGBTs under different conditions.