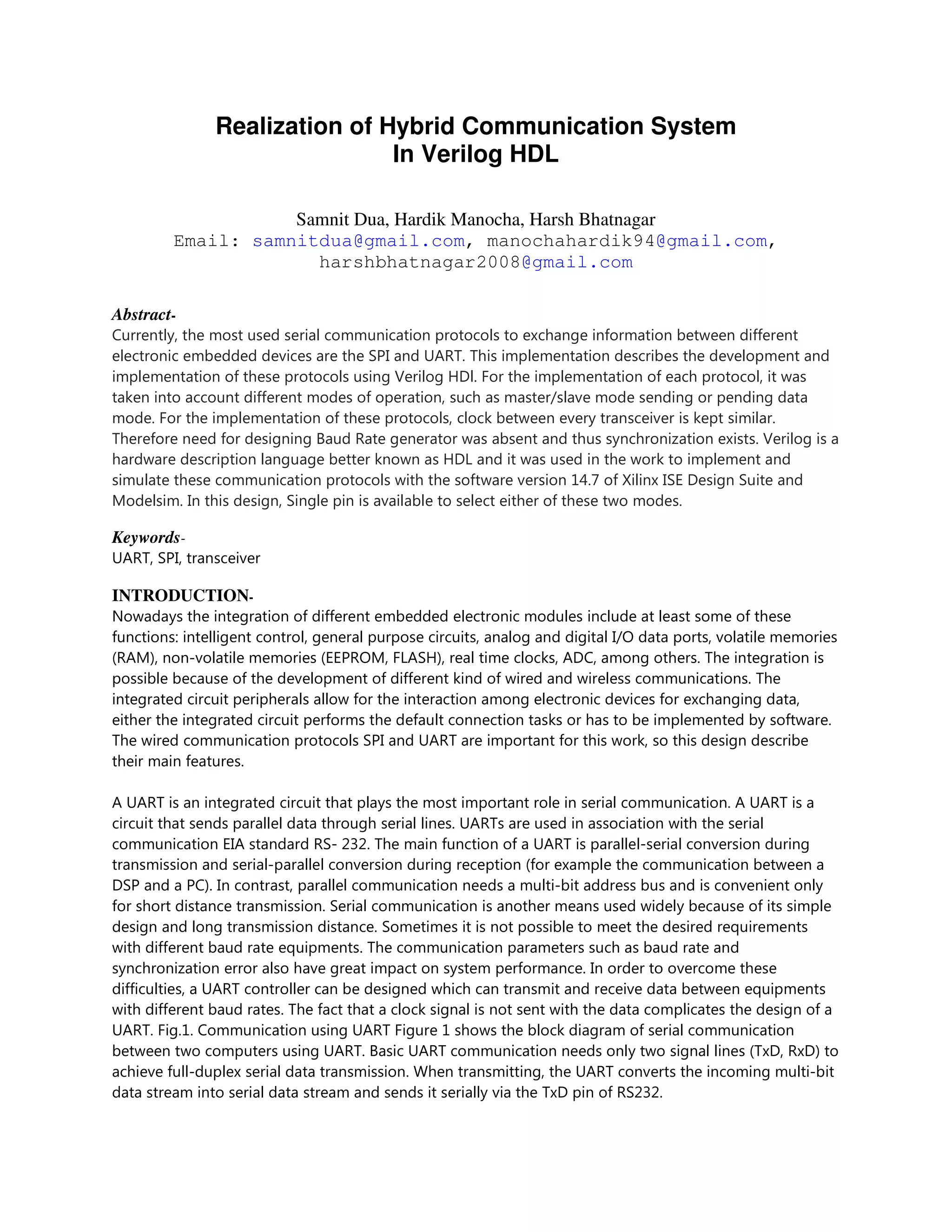

This document describes the development and implementation of the SPI and UART serial communication protocols in Verilog HDL. Both protocols were implemented considering different operating modes like master/slave and transmit/receive modes. Verilog was used to simulate the protocols in Xilinx ISE Design Suite and Modelsim. A single pin allows selecting between the SPI and UART modes.

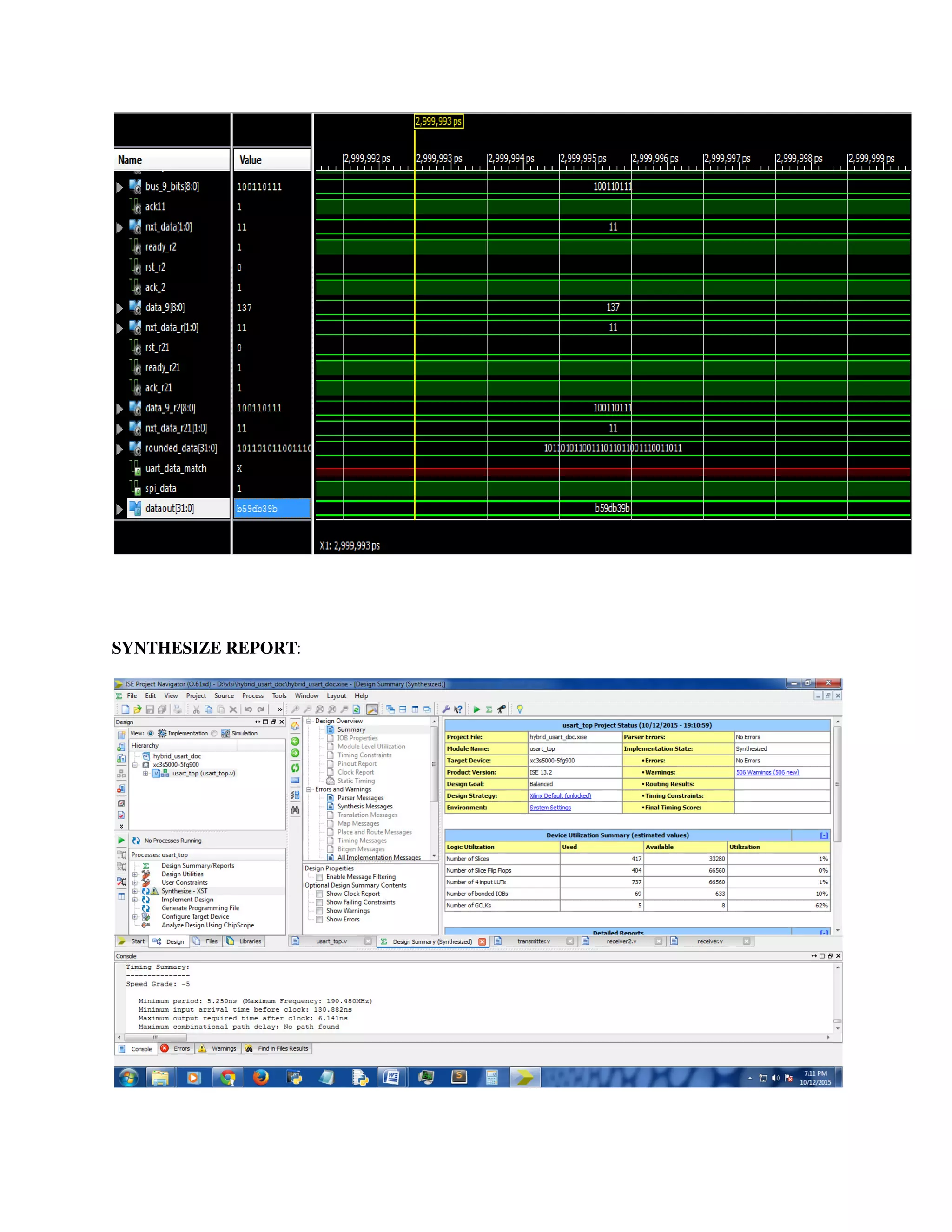

![TIMING ANALYSIS:

Speed Grade: -5

Minimum period: 5.250ns (Maximum Frequency: 190.480MHz)

Minimum input arrival time before clock: 130.882ns

Maximum output required time after clock: 6.141ns

Maximum combinational path delay: No path found

====================================================================

Process "Synthesize - XST" completed successfully

FUTURE SCOPE

Resides in using this communication protocol design for implementing T-DES, where DES would be

replaced by Hybrid AES-DES. Implementation of such design would increase the difficulties in cracking the

algorithm; thereby further increasing security far from simple AES. T-hybrid AES-DES would employ this

design in SPI mode.

CONCLUSION

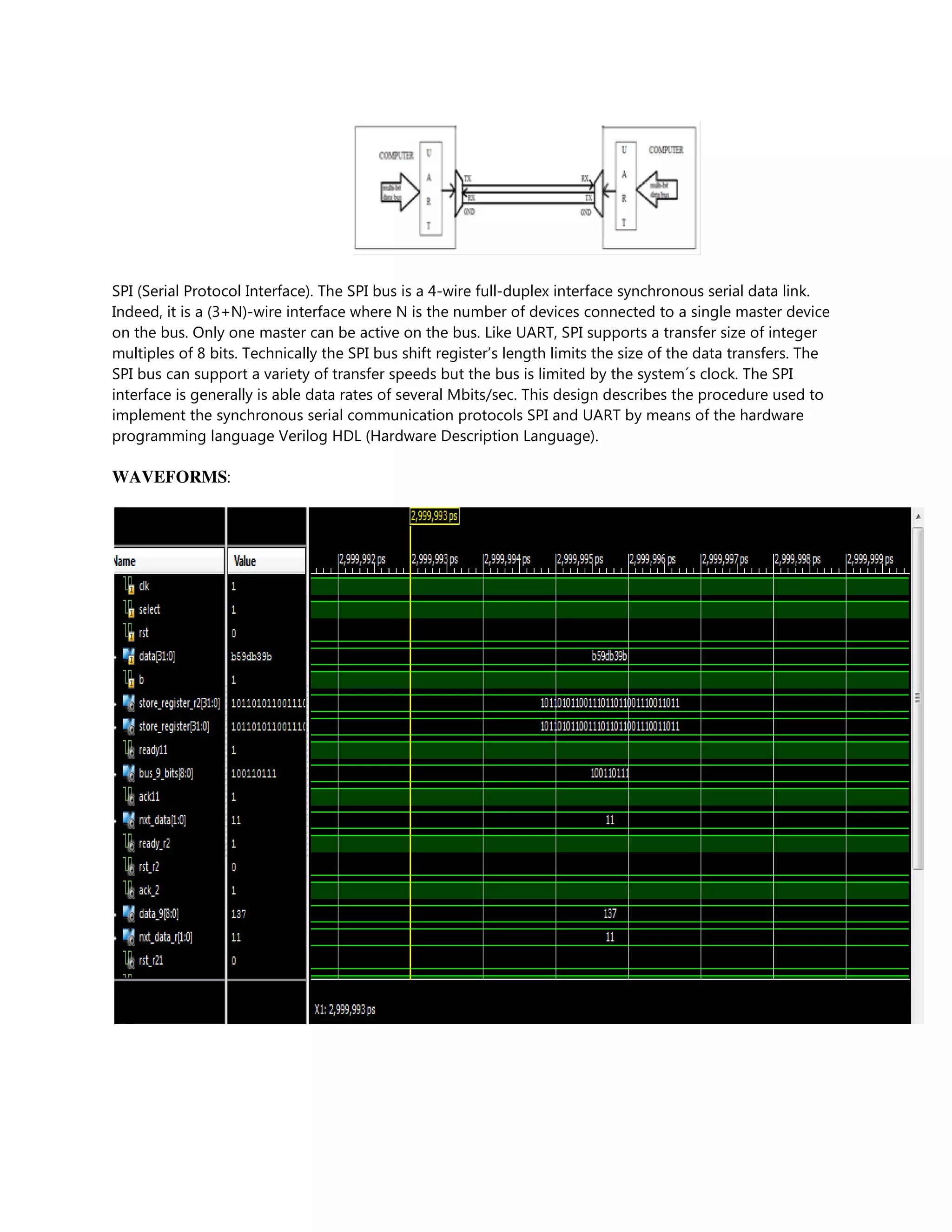

In this project, we have implemented a mix of two different communication protocols under a single chip

design. Protocols developed are UART and SPI. In UART, one transceiver transmits the data to another

transceiver. For UART mode, Select =1. While Select=0, for SPI mode, where second transceiver transmits

data to third and finally third transceiver passes back to first. Validation of design is shown under

Waveforms.

ACKNOWLEDGMENT

We would like to especially thank our project guide Mr. Harsh Bhatnagar whose valuable suggestions

helped shape the basis of our project idea.

REFRENCES

[1] www.opencore.org.Simon Srot. SPI Master Core Specification,Rev.0.6. May 16,2007

[2] Prophet, Graham. Communications IP adds SPI interface to FP-GA. EDN, v 48, n 27, Dec 11, 2003.

[3] Motorola, "MC68HC II manual,".

[4] Smart Computing Dictionary, Serial Peripheral Interface (SPI)

(online)http://www.smartcomputing.com/editorial/dictiona ry/detai l.asp?guid=&searchtype=

1&DicID=12820&RefType=Dictionary (access date 28May 2006)

[5] Frédéric Leens , An Introduction to I2C and SPI Protocols,IEEE Xplore.](https://image.slidesharecdn.com/hybridusartdocumentation-160405140126/75/Hybrid-Communication-Protocol-UART-SPI-4-2048.jpg)

![[6] ZHANG Yan-wei, Verilog HDL detailed design procedure, Posts & Telecom Press

[7] Mohd Yamani Idna Idris, Mashkuri Yaacob, Zaidi Razak, “A VHDL Implementation of UART Design with

BIST capability”

[8] Dr. T.V.S.P. Gupta, Y. Kumari, M.Asok Kumar”UART realization with BIST architecture using VHDL”

International Journal of Engineering Research and Applications(IJERA) ISSN: 2248-9622 www.ijera.com Vol.

3, Issue 1, January -February 2013, pp.636-640

[9] M.S. Harvey,Generic UART Manual,Silicon Valley,December 1999.](https://image.slidesharecdn.com/hybridusartdocumentation-160405140126/75/Hybrid-Communication-Protocol-UART-SPI-5-2048.jpg)