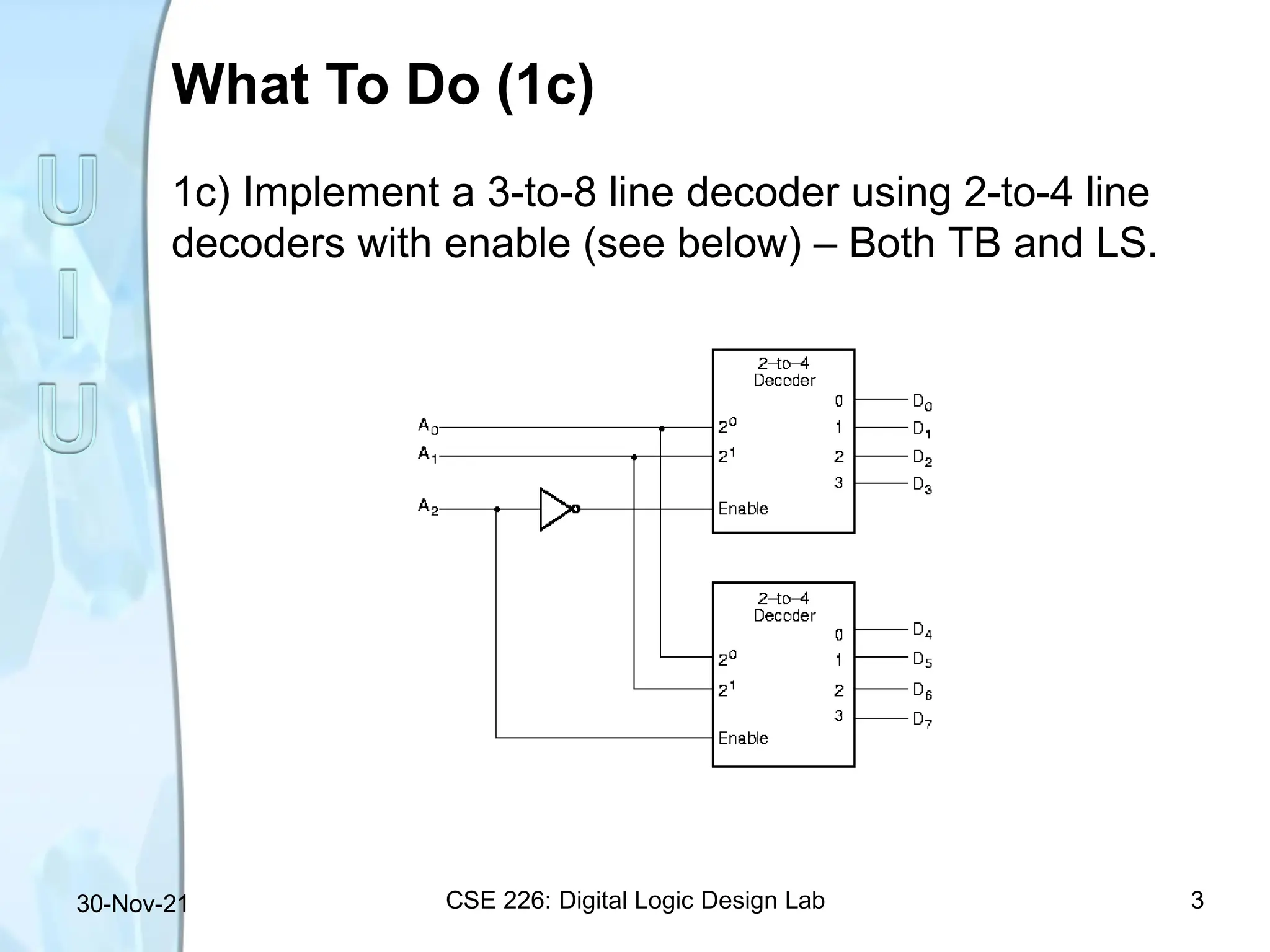

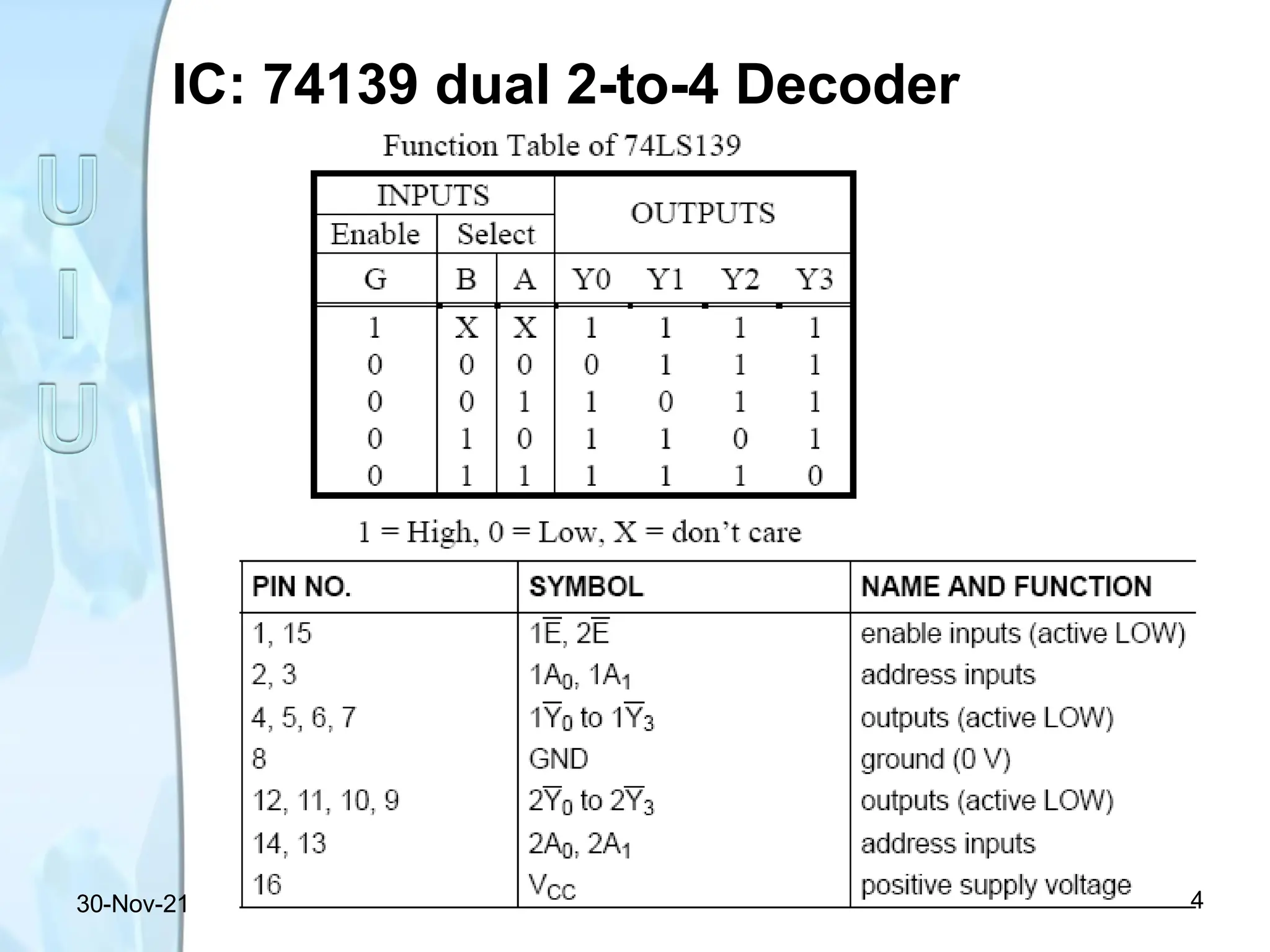

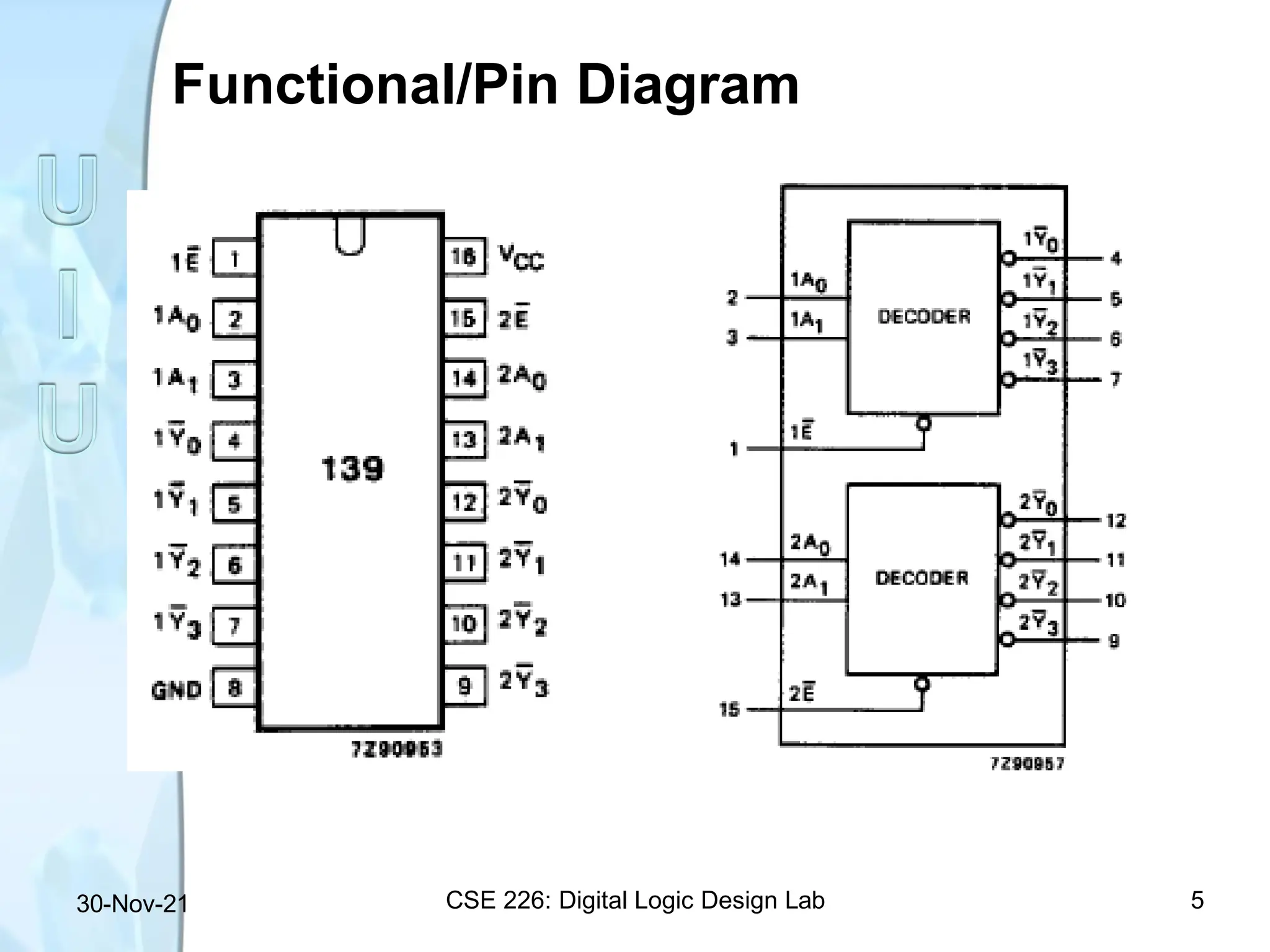

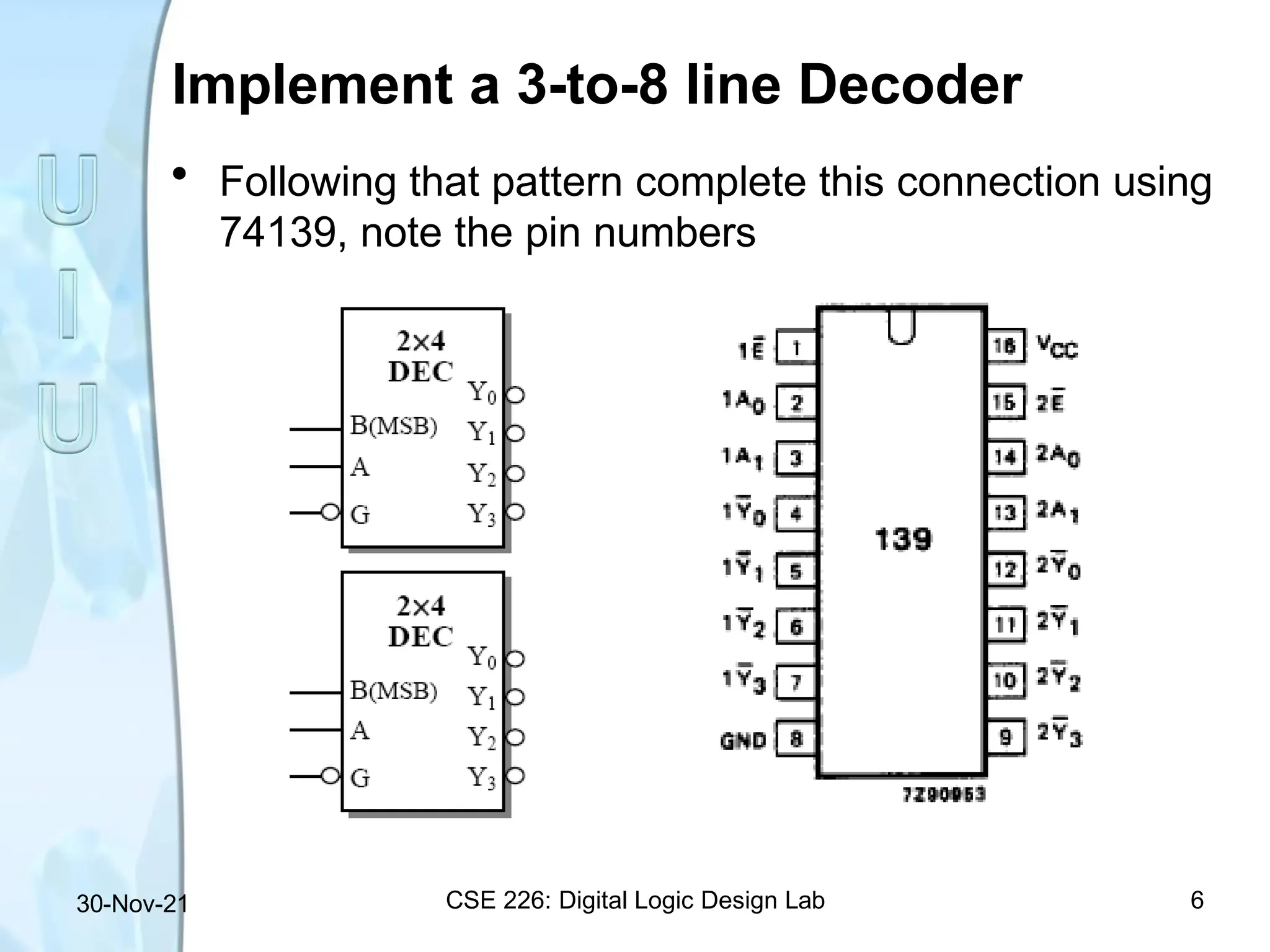

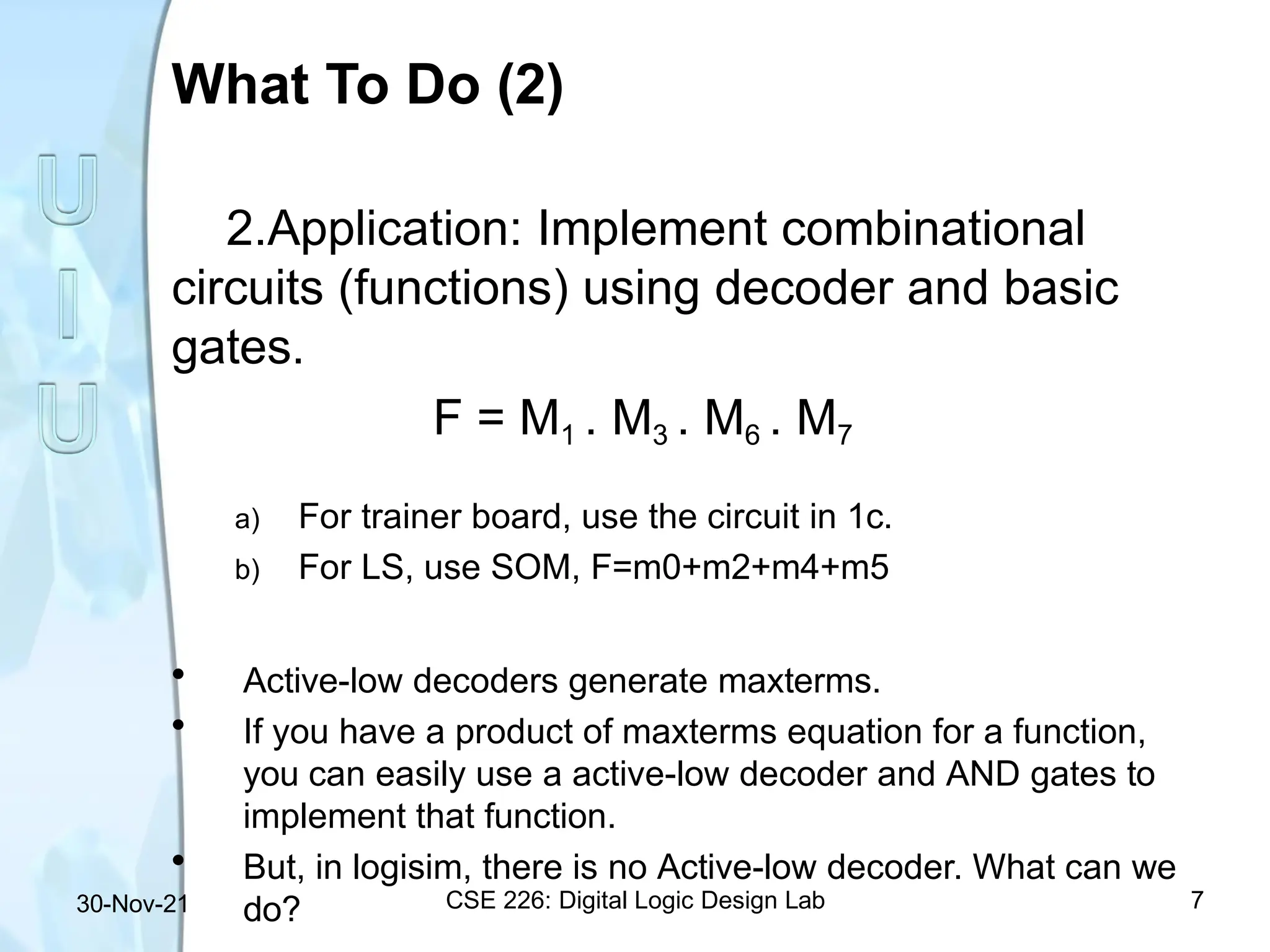

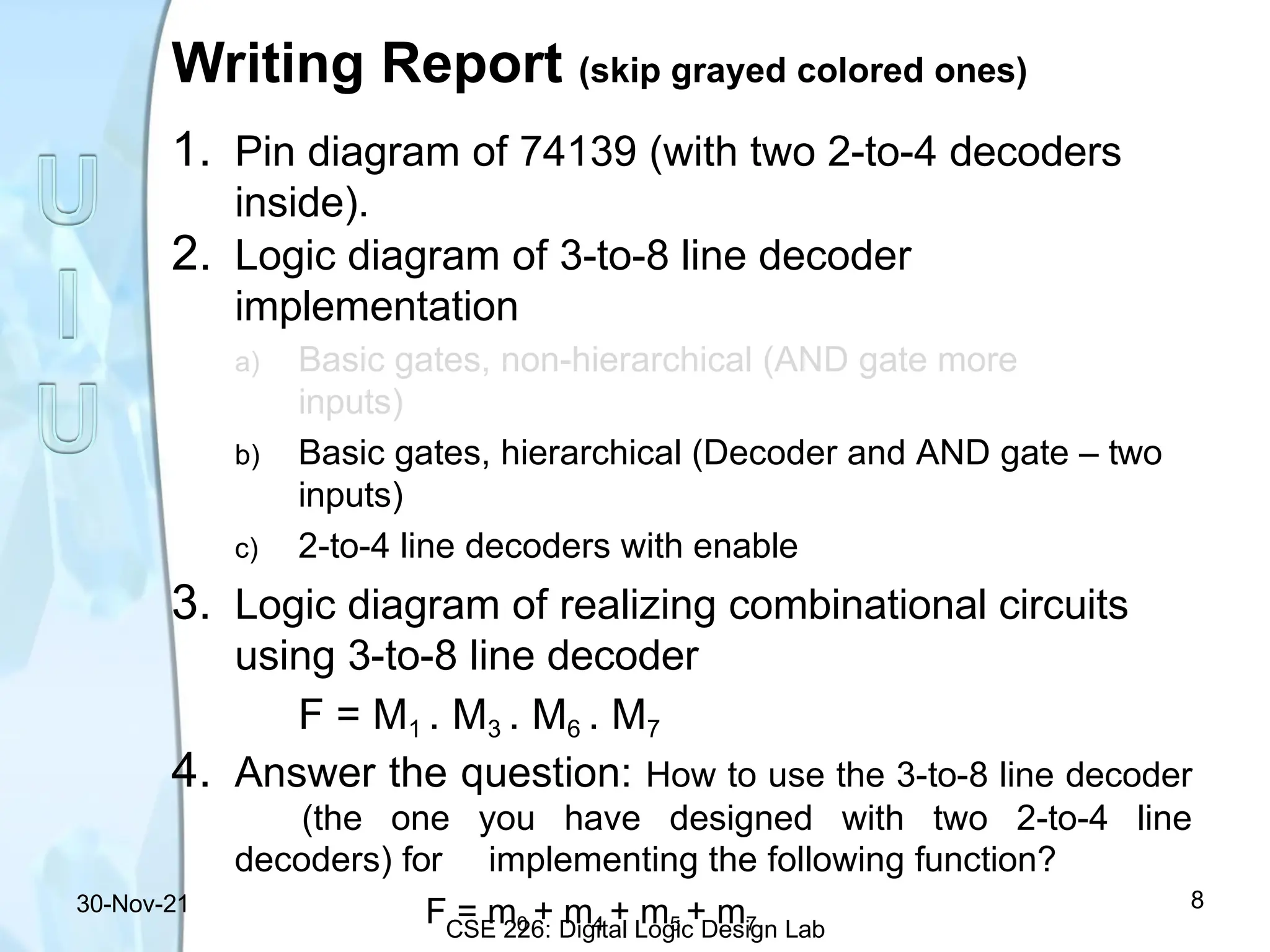

The document outlines the tasks for a digital logic design lab, focusing on implementing a 3-to-8 line decoder using various methods including basic gates and hierarchical designs. It details applications for combinational circuits and highlights the limitations of available decoders in Logisim, particularly regarding active-low decoders. Additionally, it describes report-writing requirements, including diagrams and logic implementation of specific functions.