This document provides an overview of electronic packaging fundamentals related to automotive MEMS and sensor technologies. It discusses key challenges in miniaturizing MEMS devices, high costs of component testing, and integrating MEMS with CMOS. Solutions proposed include standardized MEMS packaging to reduce costs and wafer-level testing to identify faulty devices earlier. Both approaches aim to improve reliability while lowering manufacturing expenses. Overall, the document analyzes ongoing issues in MEMS technology and packaging methods that could help advance automotive and consumer product applications of MEMS sensors.

![Electronic Packaging FundamentalsCourse Project Report

Automotive MEMS and Sensors Technology

INTRODUCTION

Micro-electromechanical systems (MEMS) are developed as a

result of technological advancement in integrated circuits and

micromanufacturing, and its technology has become the

backbone of many sensor technologies in automobiles. Although

faced with many challenges such as device miniaturization,

quality, and reliability testing, and high cost from packaging

and testing, emerging solutions such as MEMS packaging

standardization and wafer level testing can be adopted to

overcome these setbacks.

LITERATURE REVIEW

Device Miniaturization [1]

Device miniaturization has been the ongoing trend in the

electronic industry, and the demand for advancement in MEMS

technology reflects the drive as well. The recent development in

autonomous vehicles and portable devices are calling for higher

integration of MEMS sensors to support its increasing

capabilities. As these devices increase in function and

complexity, the available footprint within the device is

continuously limited by the ever-decreasing device size. The

manufacturing technique that enables the production of MEMS

technology is bulk surface machining, where layers of

mechanical structures and features are created through a

combination of etching and layer deposition. As the demand for

smaller and more intricate features rises, the industry must

provide an answer in terms of improved and more advanced

manufacturing techniques to address the miniaturization trend.

Component Testing [2]

Many MEMS devices serve as accelerometers, gyroscopes, and

sensors for critical data acquisition applications; therefore, the](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-1-2048.jpg)

![reliability and quality of these devices must be ensured.

Extensive reliability testing is performed at the device or

package level to ensure that the product meets requirements and

specifications. When it comes to testing MEMS products, both

electrical and mechanical analysis is required for a thorough

examination of the product performance. The coupling

relationship of the mechanical parts with electrical circuitry

results in a complex system that requires unique testing

equipment. The cost of testing equipment and setups such as

testing stations can easily exceed millions of dollars in capital

investment from the device manufacturer. The Challenge of

high testing cost poses a roadblock in the MEMS market and

innovative solutions are needed for a cost-saving solution.

MEMS and CMOS Integration [3]

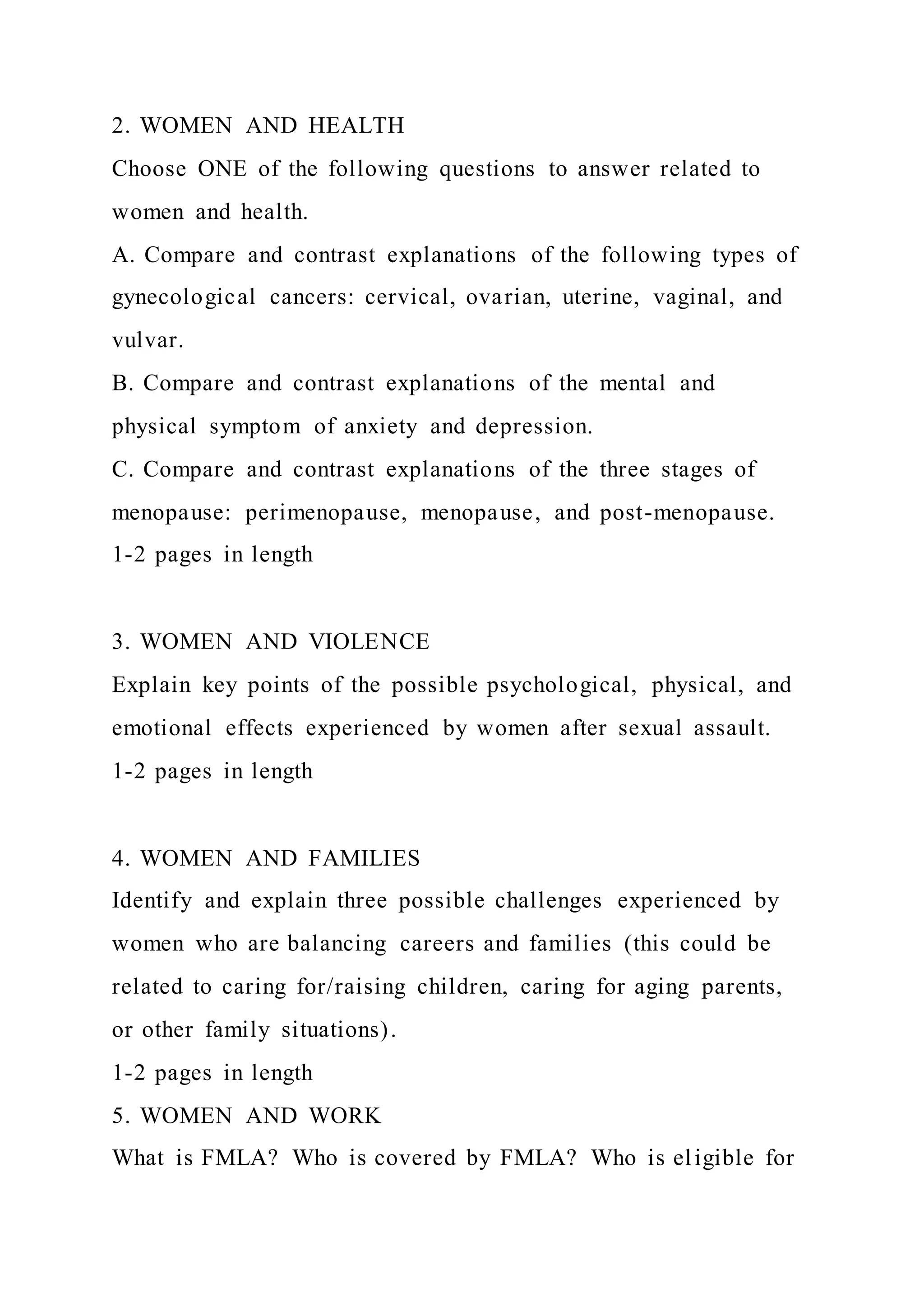

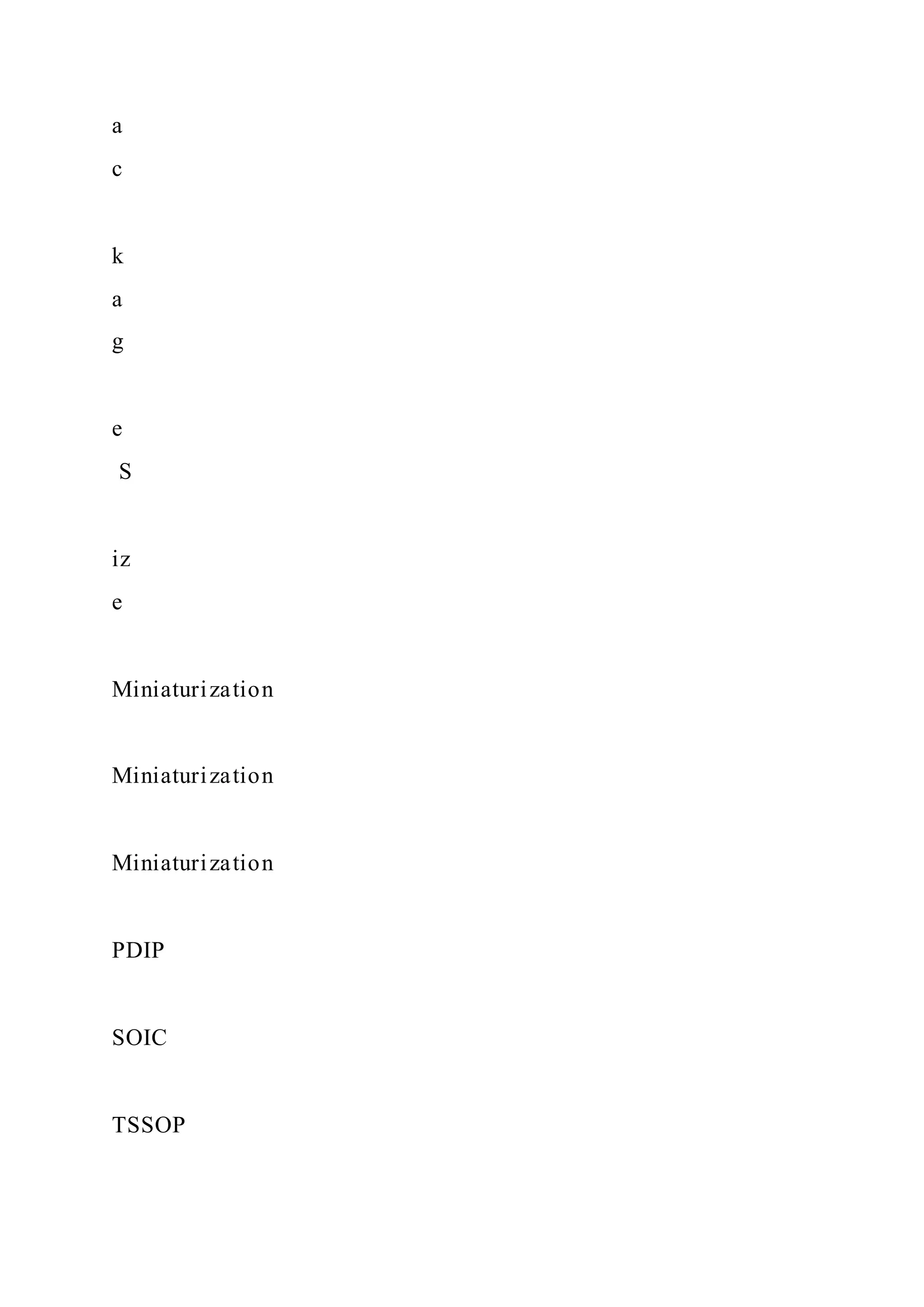

As shown in Fig. 1, MEMS structure is often coupled with

integrated circuitry to perform sensing and analysis of the

acquired data. The industry's drive to lower the production cost

and device size calls for the tackling of the challenge in MEMS

and CMOS process integration. The current method for system

integration involves the manufacturing of the MEMS and

electrical circuitry on different substrates, and interconnects or

direct bonding of the two chips are performed for device

integration. This approached is forced by the high cost

associated with monolithic integration. Challenges foreseen

within the industry would be to lower the cost associated with

the integration of MEMS with IC fabrication.

Figure 1 Acceleration sensor internal layout and MEMS

structure [4]

MEMS Packaging [5]

Packaging serves a crucial function in providing the proper

mechanical protection and environmental control for the MEMS

device. Given the role of packaging and its value in ensuring

the reliability and function of the device, packaging and testing](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-2-2048.jpg)

![can often take up to 90% of the total production cost. The key

challenge in the area of MEMS packaging falls in the design of

the enclosure to provide the proper protection against

temperature, shock, moisture, and stress while allowing data of

interest to be collected through a specified medium. In the case

of pressure sensors used in pressure monitoring and control,

package engineers must ensure that a sufficient and controlled

amount of desired inputs can be registered by the MEMS

device. This process proves to be difficult in that many of the

elements the sensor is designed for monitoring can easily cause

device malfunction if the input is let uncontrolled (ex: pressure,

temperature).

Co-design Requirement [6]

The name "micro-electromechanical system" clearly indicates

the need for the collaboration of mechanical and electrical

engineering disciplines when developing MEMS technologies.

Although the development of MEMS did not revolutionize the

world of engineering and design, it does, however, pose the

challenge and requirement for a higher level of co-design

initiative and execution. In the past, mechanical and electrical

engineers each have simulation and design software dedicated to

their area of interest and expertise. The gap between these

software (ex: FEA and EDA) pose many issues when designing

MEMS devices. The lack of communication between the

software and engineering groups means that critical design

considerations and simulation results were not being shared

efficiently. To successfully develop a product to ensure that

quality and reliability performance are meeting requirements,

there is a growing challenge for software developers and

designers to come up with a solution and initiative for co-

designs.

DESCRIPTION

Standardized Package](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-3-2048.jpg)

![Solution

s

As previously mentioned, packaging and testing can often take

up to 90% of the total production cost of MEMS devices. Unlike

conventional IC packages, where package options have been

standardized and thoroughly tested by many manufacturers,

MEMS packaging still proves to be challenging due to the high

level of customization and variation in the package design [7].

The high cost associated with packaging can be resolved by

introducing a company or industry-wide package standard. To

establish a standardized package model for MEMS devices,

characteristics such as package dimension, I/O count,

connection type, and material sets must be defined. Key ideas to

keep in mind when defining such parameters should be designed

for manufacturability and for reliability, where these two

factors can greatly influence the resulting cost of the device if

left unconsidered. Each characteristic mentioned above warrants

extensive testing and review because the chosen package types

will replace many customized package designs and must be

capable of providing the package solution needed for a wide

range of products.

Wafer Level Testing](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-4-2048.jpg)

![The general approach for MEMS device testing has been at the

component level, where the quality of the product is inspected

at the end of the fabrication process. This approach inherently

increases the cost of MEMS fabrication because faulty devices

are identified at the end of the manufacturing process, leading

to higher waste of resources and time since the products have

been processed and packaged. A recent approach taken by many

device manufacturers is the testing of the MEMS device at the

wafer level – wafer-level testing.

Wafer-level testing involves providing the device with required

electrical stimulation, as well as required testing input such as

sound, light, vibration, temperature, and pressure depending on

the sensor application [8]. Traditional IC testing often requires

input and output both in the form of an electrical signal. Wafer -

level testing of MEMS devices requires not only the electrical

input but also output as a result of the mechanical input to the

system (ex: sensor applications). To conduct tests at the wafer

level, testing devices such as test probes and controllable

testing chambers must be acquired. Depending on the

device/sensor application, the chamber needs to be capable of

creating an inert environment with controlled environmental

specifications targeting different types of MEMS sensors.

INFERENCES/ADVANTAGES-DISADVANTAGES

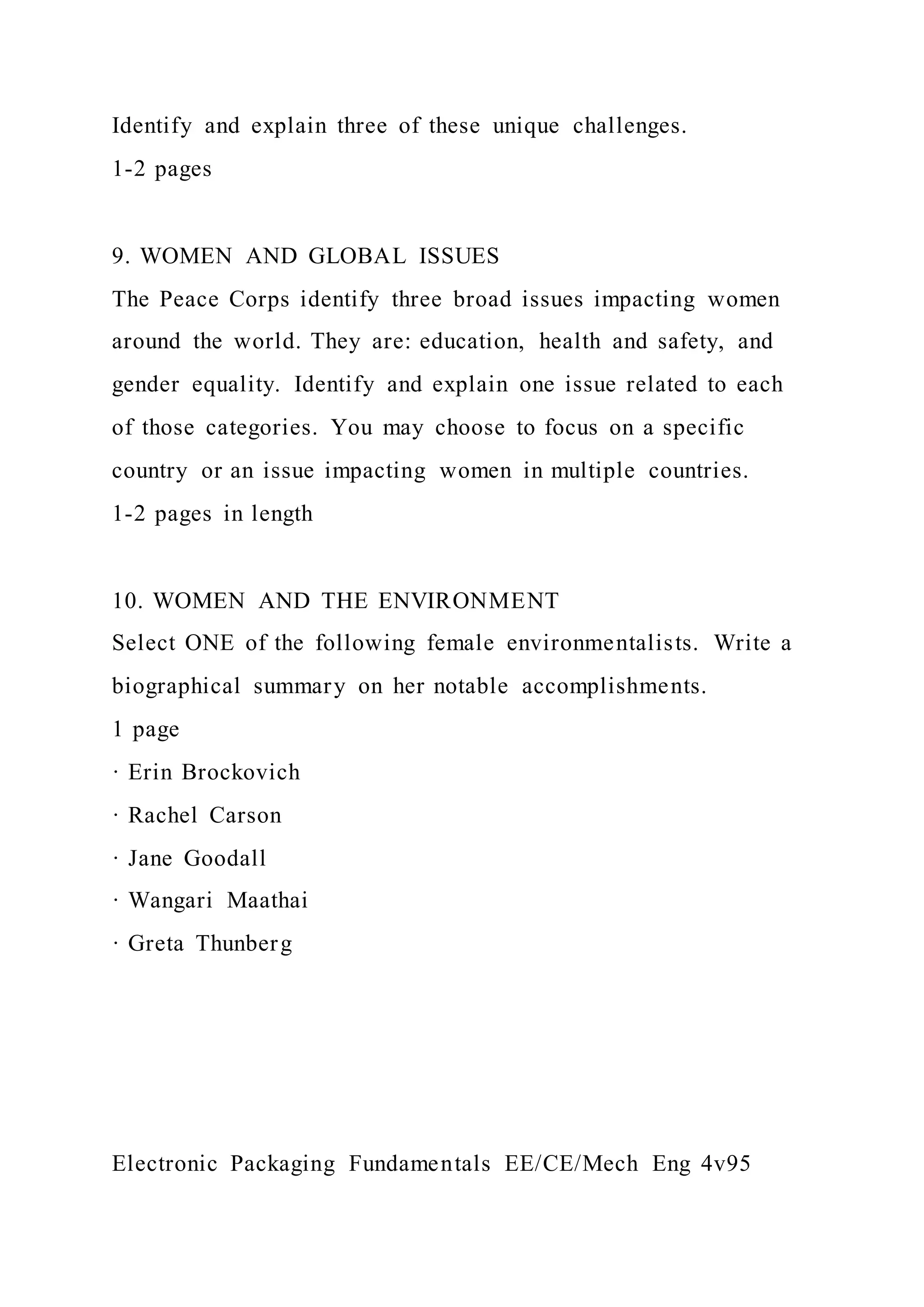

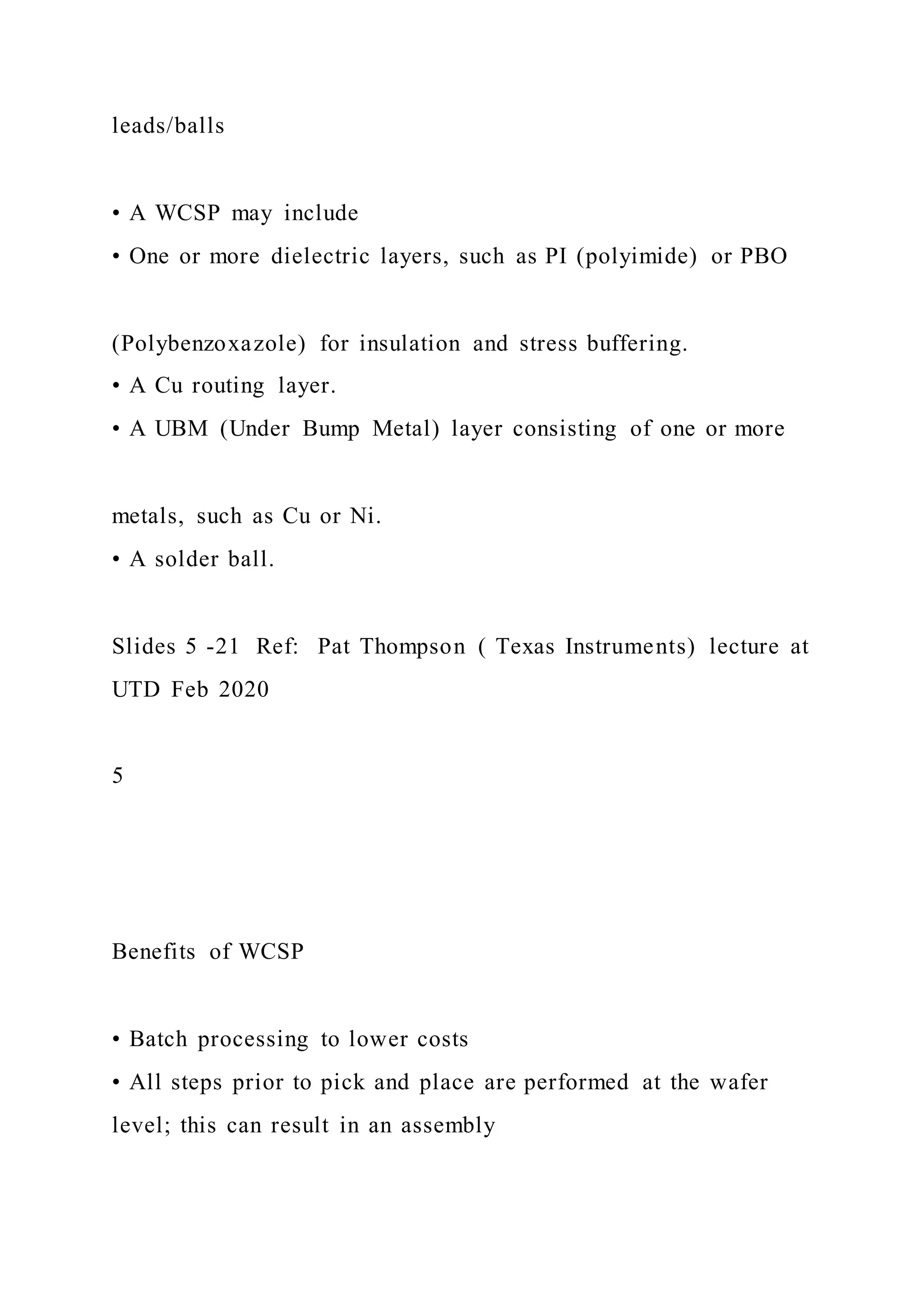

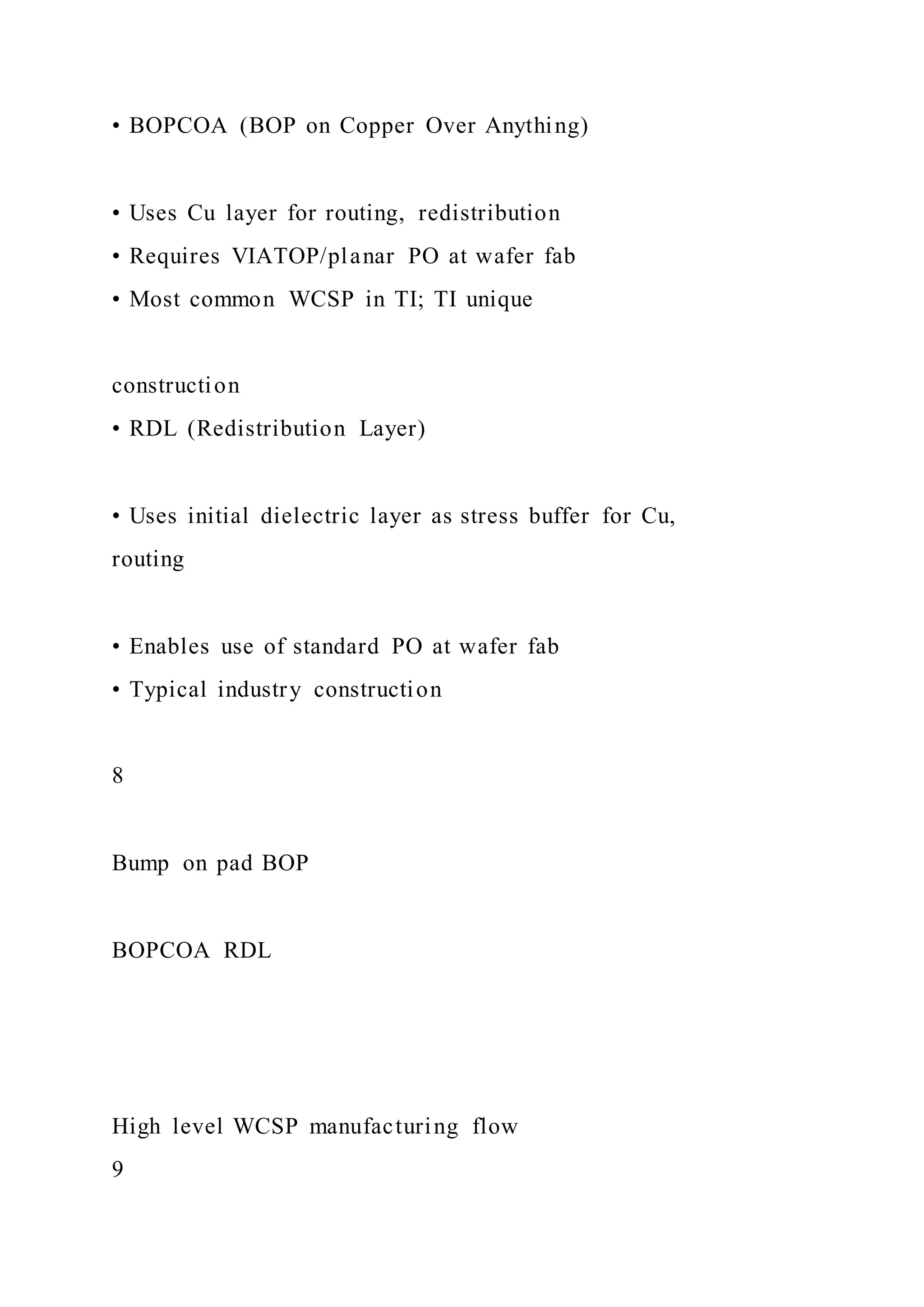

With the application of both package standardization and wafer](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-5-2048.jpg)

![capable of both delivering mechanical input while retrieving the

electrical signal and response; the test environment needs to

provide the ability for fine control of the testing environment to

ensure test accuracy and repeatability.

Figure 2 Cost comparison with and without wafer-level testing

[8]

CONCLUSIONS

As the demand for MEMS technology grows with the increasing

complexity of application areas, many challenges have and will

continue to pose design and application issues for MEMS

devices. It is paramount that the industry position the necessary

resources and effort in tackling those challenges mentioned in

this paper to improve the function and performance of MEMS

products. In the case of this review paper, package

standardization and wafer level testing are discussed and

analyzed to align focuses on the potential benefits capable of

receiving from these two approaches. The number of

automobiles produced and purchased is growing at an upward

trend, meaning MEMS are being incorporated in more and more

of our daily lives. This trend requires the continual

advancement of MEMS products through methods such as those

described in this paper.](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-7-2048.jpg)

![REFERENCES

[1]Marek, J. “MEMS for Automotive and Consumer

Electronics.” 2010 IEEE International Solid-State Circuits

Conference - (ISSCC), vol. 53, IEEE, 2010, pp. 9–17,

doi:10.1109/ISSCC.2010.5434066.

[2]Muhammad, et al. “A Review on Key Issues and Challenges

in Devices Level MEMS Testing.” Journal of Sensors, Hindawi,

21 Feb. 2016, www.hindawi.com/journals/js/2016/1639805/.

[3]Villanueva, et al. “Grand Challenge in N/MEMS.” Frontiers,

Frontiers, 11 Nov. 2015,

www.frontiersin.org/articles/10.3389/fmech.2015.00015/full.

[4]Marek, J. “Automotive MEMS Sensors - Trends and

Applications.” Proceedings of 2011 International Symposium on

VLSI Technology, Systems and Applications, IEEE, 2011, pp.

1–2, doi:10.1109/VTSA.2011.5872208.

[5]Bhat, K N, and M M Nayak. MEMS Pressure Sensors- An

Overview of Challenges in Technology and Packaging.

pdfs.semanticscholar.org/b3ab/9fd4fcae88c557c7d7ccd7e26472

a50c4b60.pdf.

[6]Karam, J. M., et al. “MEMS: The New Challenge for the

Electronic Design Automation Vendors.” SpringerLink,

Springer, Berlin, Heidelberg, 1 Jan. 1998,

link.springer.com/chapter/10.1007/978-3-662-39696-4_11.](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-8-2048.jpg)

![[7]Bauer, Charles E. Packaging MEMS, The Great Challenge of

the 21st Century. TechLead Corporation, 2000,

www.osti.gov/etdeweb/servlets/purl/20136250#page=40.

[8]Werner, Frank-Michael. “Wafer Level Test: Significant Time

and Cost Reduction of MEMS Production.” Electron-Mec, SUSS

MicroTec Test Systems GmbH, www.electron-mec.com/wp-

content/uploads/applications/Publication-

2003_Wafer_Level_Test_Significant_Time_and_Cost_Reductio

n_of_MEMS_Production.pdf.

Page 2 of 2

HSL 3831 Women in Contemporary Society

Final Exam

Provide a response according to the directions for each. For

each response, integrate at least one professional resource to

support your response. You may use your textbook and/or other

professional literature sources (i.e., textbooks,

local/state/national/international professional organization

websites, .gov sites, .edu sites). Cite sources in the body of your

response and provide a full reference citation at the end of the

exam. Refer to syllabus schedule for due date and time. 10

points each/100 points possible.](https://image.slidesharecdn.com/electronicpackagingfundamentalscourseprojectreportautomoti-220921175850-4ac6e28c/75/Electronic-Packaging-FundamentalsCourse-Project-ReportAutomoti-9-2048.jpg)