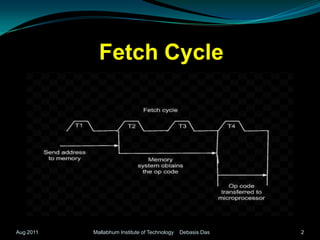

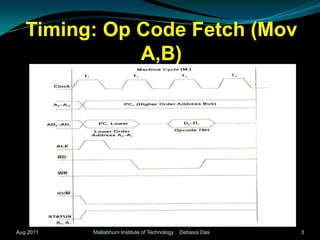

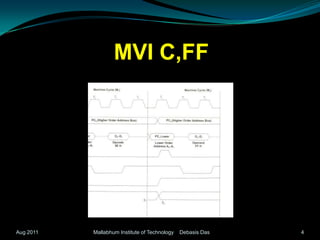

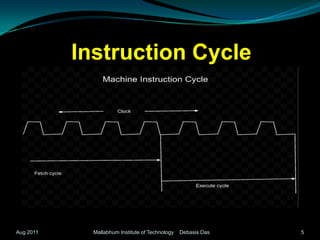

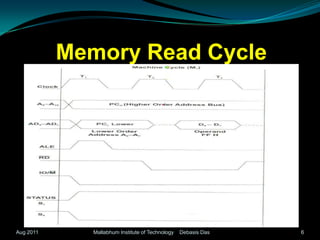

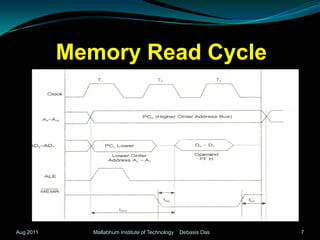

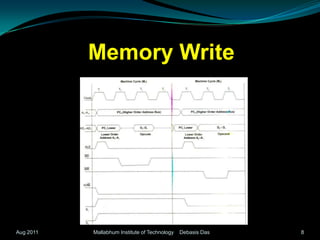

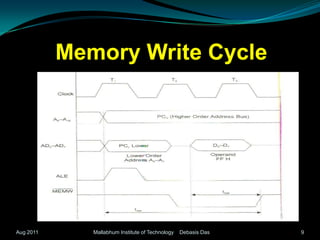

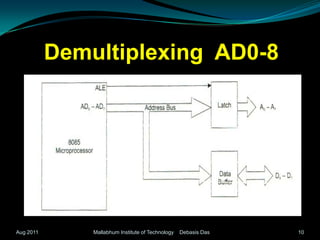

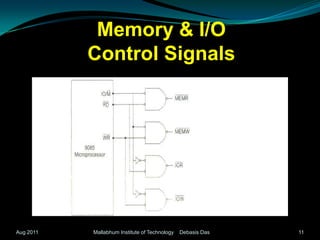

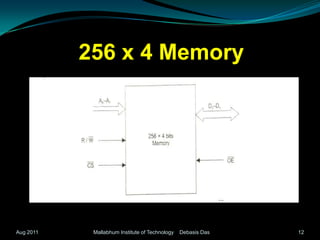

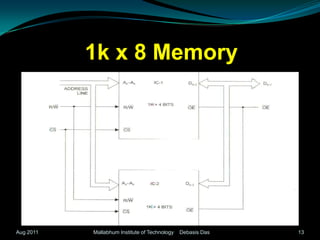

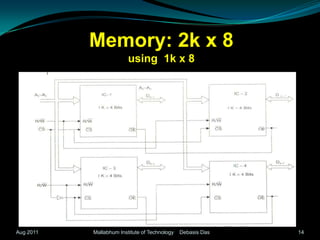

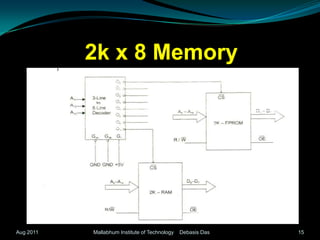

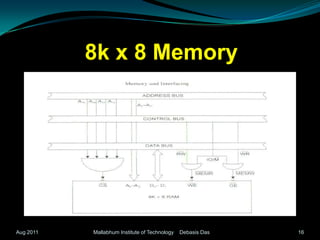

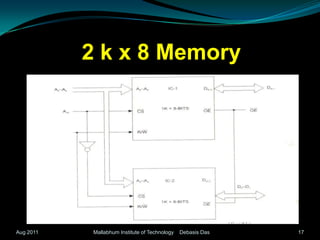

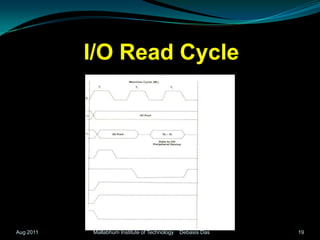

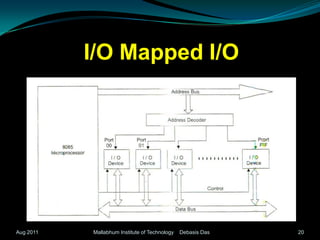

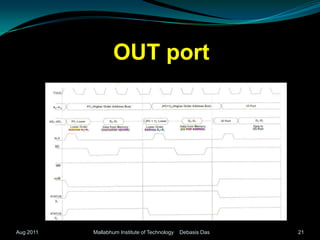

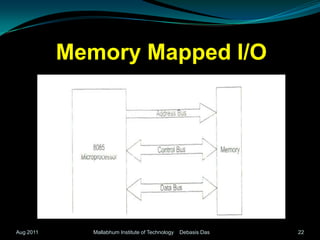

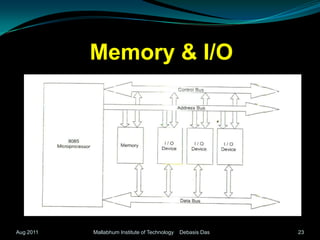

This document discusses the operation of microprocessors and microcontrollers, including fetch cycles, instruction cycles, memory read/write cycles, demultiplexing address lines, different memory configurations from 256x4 to 8kx8, input/output port timing, and memory-mapped versus input/output mapped input/output techniques. It is a lecture on hardware interfacing from Mallabhum Institute of Technology presented by Debasis Das in August 2011.