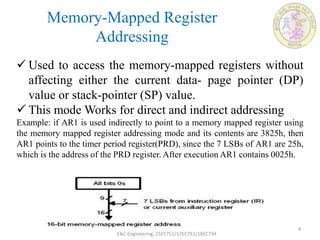

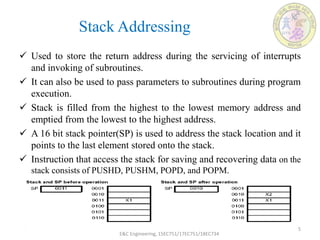

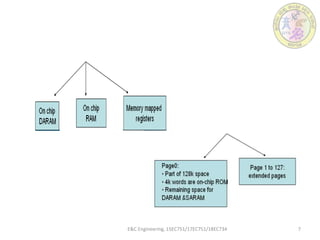

The document discusses the data addressing modes and memory management of the TMS320C54XX processors, focusing on memory-mapped register and stack addressing modes. It outlines the memory space capabilities, including total memory size and organization, and details the program control structure, which includes the program counter and repeat counters. Learning outcomes emphasize a comprehensive understanding of these concepts for effective programming and application of the TMS320C54XX devices.