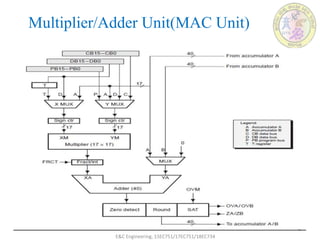

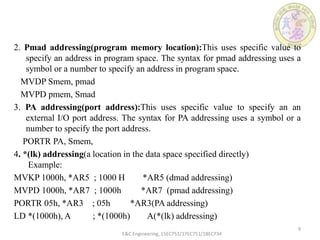

The document discusses the architecture and functional block of the TMS320C54xx digital signal processors, focusing on the multiplier/adder unit and its components, including data addressing modes. It outlines seven basic addressing modes for accessing operands, including immediate, absolute, accumulator, and indirect addressing. Additionally, the learning outcomes emphasize understanding the MAC unit and addressing modes of the TMS320C54xx devices.