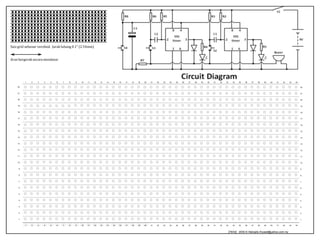

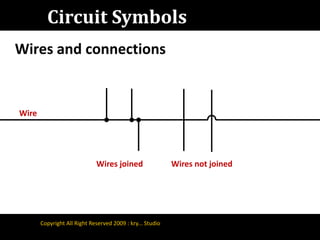

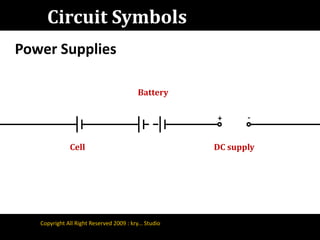

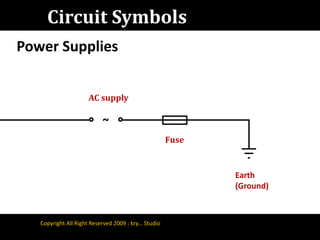

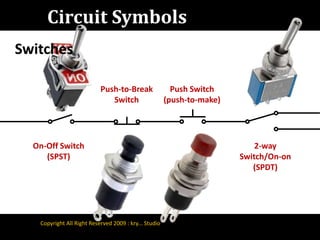

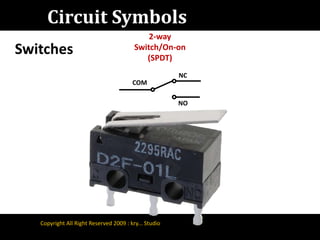

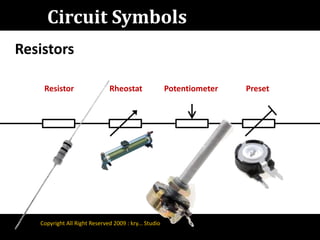

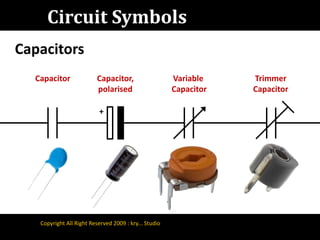

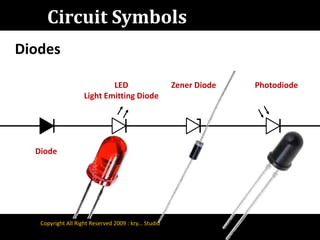

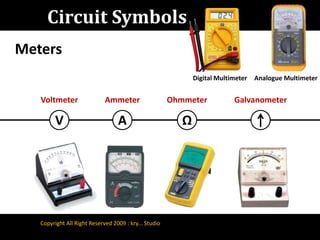

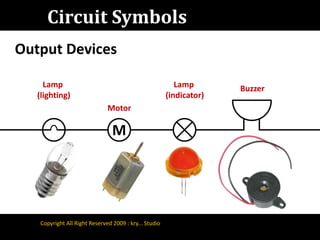

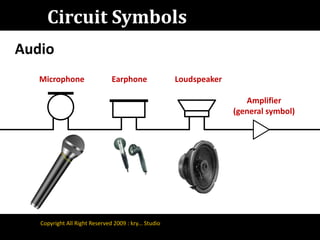

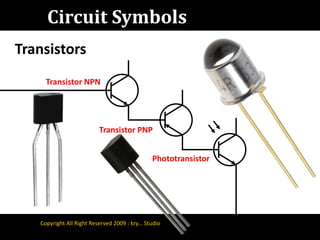

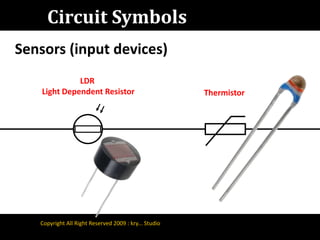

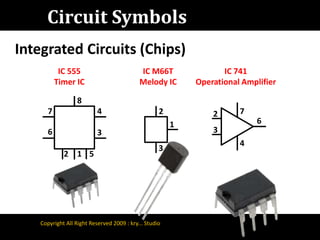

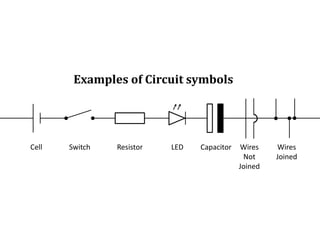

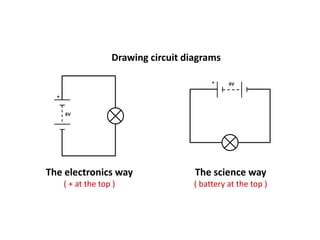

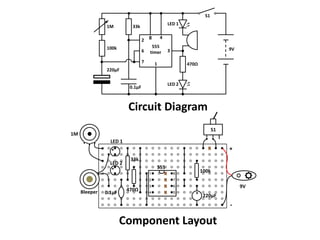

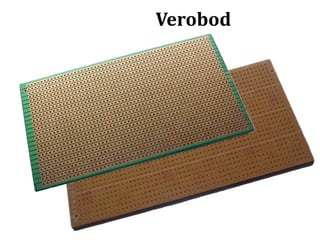

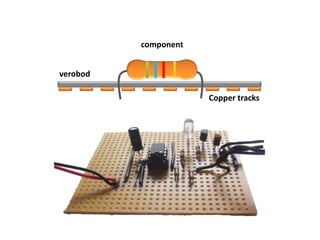

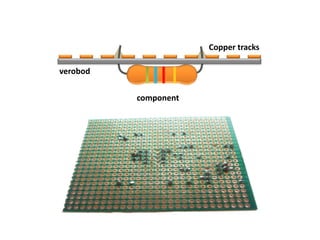

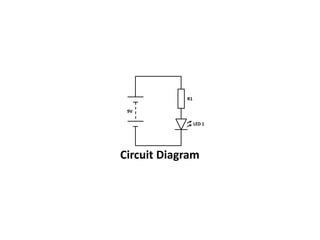

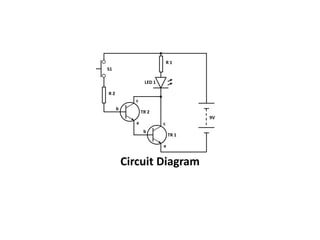

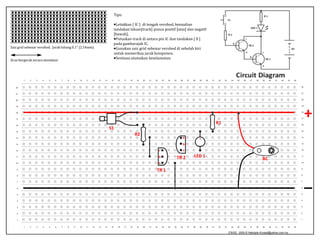

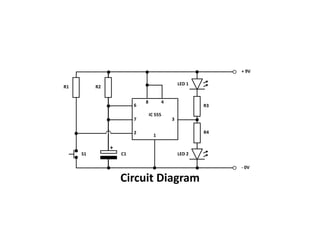

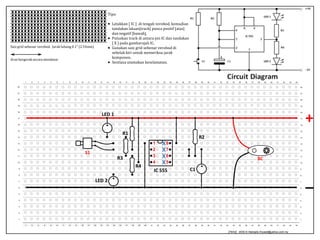

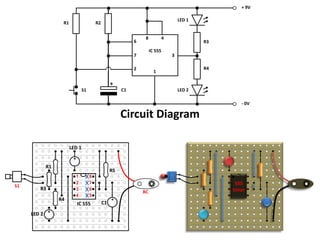

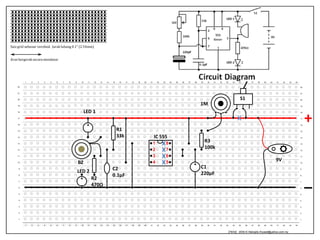

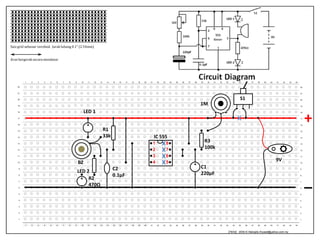

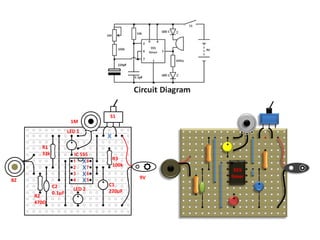

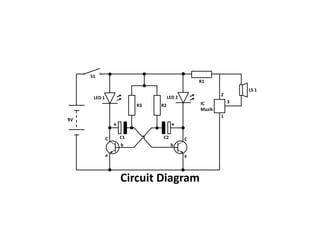

This document provides circuit symbols and their explanations used in circuit diagrams. It includes common electronic components like batteries, resistors, capacitors, transistors, integrated circuits, and other symbols. The document also demonstrates how to plan circuit board layouts by placing components and drawing trace connections between them on a grid-based board template. Examples are given of improving circuit board layout plans and checking the designs. Guidance is provided on positioning integrated circuits in the center and drawing positive and negative power connections.

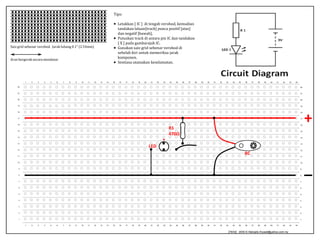

![LUKISAN BERGAMBAR [litarverobod]Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-26-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-27-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jaraklubang 0.1" (2.54mm)Arusbergeraksecaramendatar123456789101112131415161718192021222324252627282930313233343536373839404142434422222121202019191818171716161515141413131212111110109988776655443322111234567891011121314151617181920212223242526272829303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-29-320.jpg)

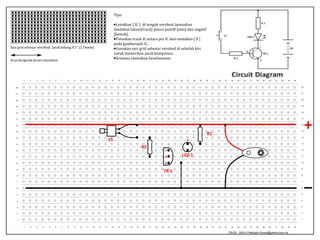

![Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-32-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-33-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jaraklubang 0.1" (2.54mm)Arusbergeraksecaramendatar222120191812345678910111213141516171819202122232425262728293031323334353637383940414243441722162115201419+131812171116R1470Ω1015914+8LED13712BC611_51049382716543211234567891011121314151617181920212223242526272829303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-35-320.jpg)

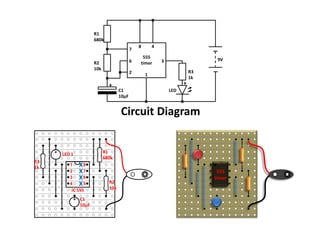

![Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-37-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-38-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jaraklubang 0.1" (2.54mm)Arusbergeraksecaramendatar222120191812345678910111213141516171819202122232425262728293031323334353637383940414243441722162115201419+131812171116R1470Ω1015914+8LED13712BC611_51049382716543211234567891011121314151617181920212223242526272829303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-40-320.jpg)

![+R1S1+R2cLED 1beTR 1_Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-45-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-46-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jarak lubang 0.1" (2.54mm)Arus bergerak secara mendatar123456789101112131415161718192021222324252627282930313233343536373839404142434422222121202019191818171716161515141413131212111110109988776655443322111234567891011121314151617181920212223242526272829303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-48-320.jpg)

![+R1S1+R2cLED 1beTR 1_Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-50-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-51-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jarak lubang 0.1" (2.54mm)Arus bergerak secara mendatar123456789101112131415161718192021222324252627282930313233343536373839404142434422222121202019191818171716161515141413131212111110109988776655443322111234567891011121314151617181920212223242526272829303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-53-320.jpg)

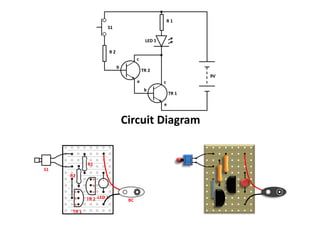

![Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-58-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-59-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jarak lubang 0.1" (2.54mm)Arus bergerak secara mendatar+R1S1R2+ebccLED 1TR 2bBCeTR 1_ [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my 123456789101112131415161718192021222324252627282930313233343536373839404142434422222121202019191818171716161515141413131212111110109988776655443322111234567891011121314151617181920212223242526272829303132333435363738394041424344](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-61-320.jpg)

![Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-63-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-64-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jarak lubang 0.1" (2.54mm)Arus bergerak secara mendatar+R1S1R2+ebccLED 1TR 2bBCeTR 1_ [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my 123456789101112131415161718192021222324252627282930313233343536373839404142434422222121202019191818171716161515141413131212111110109988776655443322111234567891011121314151617181920212223242526272829303132333435363738394041424344](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-66-320.jpg)

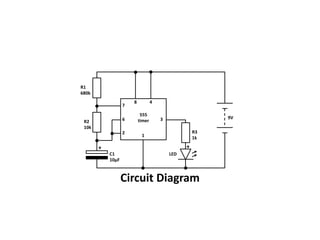

![Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-71-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-72-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jaraklubang 0.1" (2.54mm)Arusbergeraksecaramendatar222120191812345678910111213141516171819202122232425262728293031323334353637383940414243441722162115201419+131812171116R1680k+10LED 115R31k914X18813X27712X36611R210kX45510IC 55549_3C110µF8+27165432112345678910111213141516171819202122232425262728729303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-74-320.jpg)

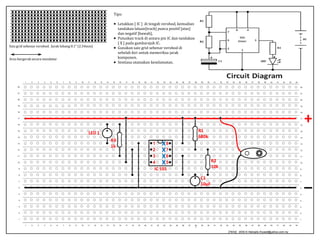

![Tips:Letakkan [ IC ] ditengahverobod, kemudiantandakanlaluan[track] puncapositif [atas] dannegatif [bawah],](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-76-320.jpg)

![Putuskan track diantara pin IC dantandakan [ X ] padagambarajah IC.](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-77-320.jpg)

![Sentiasautamakankeselamatan.Saiz grid sebenarverobod. Jaraklubang 0.1" (2.54mm)Arusbergeraksecaramendatar222120191812345678910111213141516171819202122232425262728293031323334353637383940414243441722162115201419+131812171116R1680k+10LED 115914R31kX18813X27712X36611R210kX45510IC 55549_38C110µF+27165432112345678910111213141516171819202122232425262728729303132333435363738394041424344 [78/02] 2009 © Hakcipta Krysaid@yahoo.com.my](https://image.slidesharecdn.com/circuitdiagramsandcomponentlayouts-090620055807-phpapp01/85/Circuit-Diagrams-And-Component-Layouts-79-320.jpg)