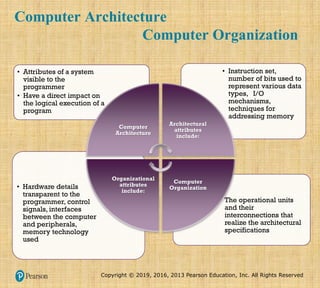

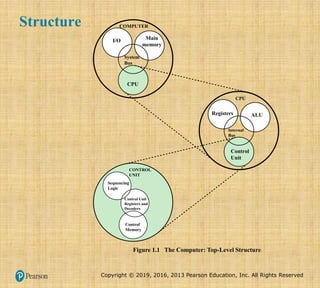

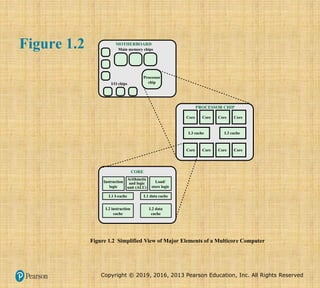

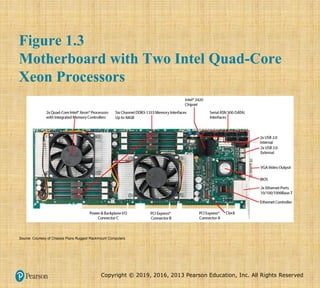

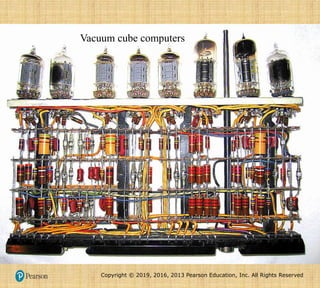

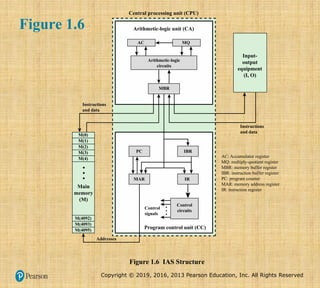

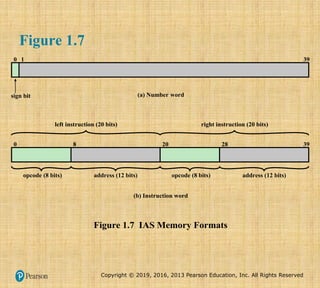

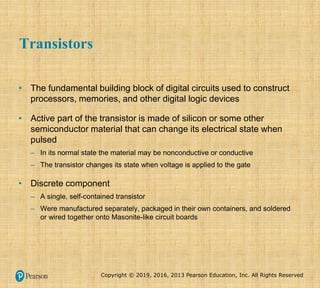

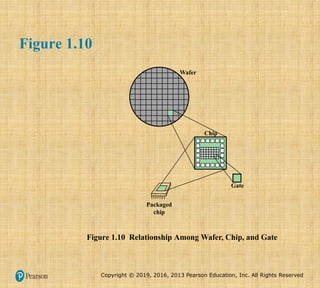

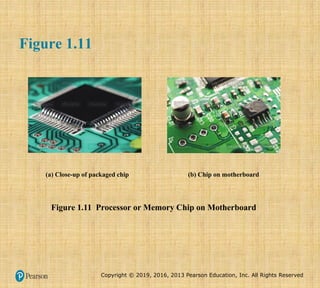

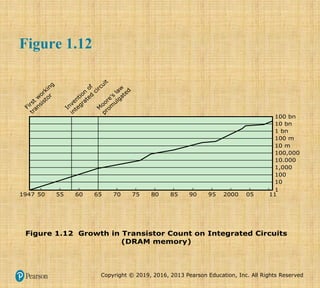

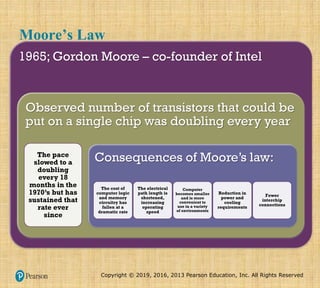

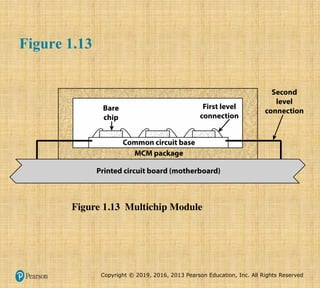

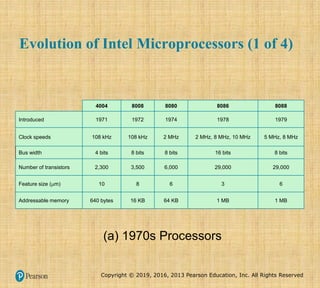

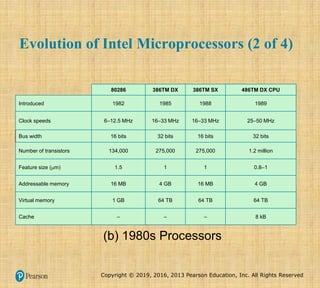

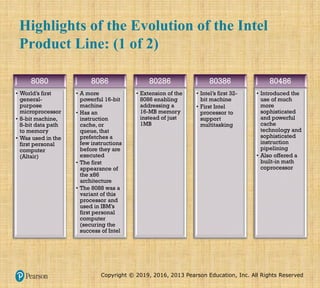

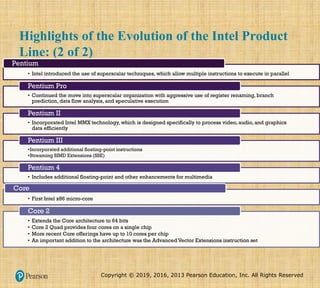

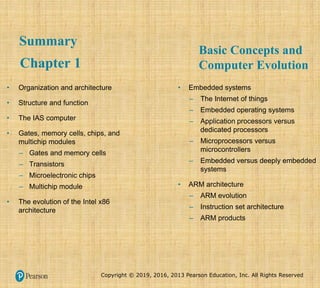

This document provides an overview of computer organization and architecture. It defines computer architecture as the attributes of a system visible to a programmer, such as instruction set and addressing modes, while computer organization refers to the operational units and interconnections that implement the architectural specifications. The document then discusses the hierarchical structure and basic functions of computers. It provides details on the typical components of a computer's structure, including the central processing unit (CPU), main memory, input/output, and interconnects. The document also covers the history of computer development from vacuum tubes to integrated circuits, Moore's Law, and trends in increasing transistor counts.