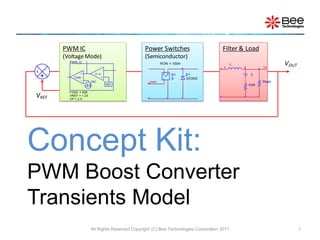

Concept Kit:PWM Boost Converter Transients Model

- 1. PWM IC Power Switches Filter & Load (Voltage Mode) U? (Semiconductor) PWM_IC RON = 100m 1 L 2 Vo VOUT - - + E/A S1 D1 C - + + + Comp S DIODE + - - Rload OSC pwm REF ESR FOSC = 52K VREF VREF = 1.23 VP = 2.5 Concept Kit: PWM Boost Converter Transients Model All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 1

- 2. Contents 1. The PWM Boost Converter Topology 2. Power Switches (Semiconductor) 3. Boost Converter Design Workflow 1 Setting PWM Controller’s Parameters 2 Setting Output Voltage: Rupper, Rlower 3 Inductor Selection: L 4 Capacitor Selection: C, ESR 5 Setting the Compensator Parameters 4. Boost Converter Simulation (Example) 4.1 Switching Waveforms 4.2 Power State Switches Voltage and Current 5. Load Transient Response Simulation (Example) 6. Boost Converter Reliability Testing (Example) 7. Converter Efficiency 7.1 Converter Efficiency vs. MOSFET, Rds(on) 7.2 Converter Efficiency vs. DIODE, VF 8. Simulation Using Real Device Models (Example) 8.1 Switching Waveforms (Real Device Models) 8.2 Converter Efficiency (Real Device Models) 9. SpicePark of MOSFET Model Simulation Index All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 2

- 3. 1.The PWM Boost Converter Topology Power Stage: Boost topology D1 RLs L DIODE v out S1 S Vin + + pwm C - - R RON = 0.01 ESR Error Amplifier C2 0 C1 R1 err R2 Rupper U1 PWM_IC C3 - Type 3 Compensator* + E/A + Rlower Comp - OSC REF FOSC = {f osc} 0 Voltage Mode VREF = {Vref } VP = {Vp} * Please see appendix B for the detail All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 3

- 4. 2.Power Switches (Semiconductor) The parameter RON represents Rds(on) characteristics of MOSFET (usually provide by the manufacturer datasheet). IIN IN I IIN IIN BOOST_SW BOOST_SW D1 DIODE IOUT BOOST_SW • BOOST_SW IOUT IOUT A Near-Ideal IOUT DIODE can be modeled by using SPICE primitive model (D), which ++ ++ DD D ++ D + parameters are : N=0.01 RS=0 CJO=1p. + S1 S + + pwm • A near-ideal MOSFET can be modeled by VIN IN V VIN VIN - - VOUT VOUT VOUT VOUT using PSpice VSWITCH that is voltage D RON = 0.01D D D controlled switch. (the default parameters -- -- (MOSFET) -- -- are Roff=1e7 Ron=0.01 Voff=1.47V Von=1.5V) All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 4

- 5. 3.Boost Convertor Design Workflow The Purpose of the Circuit Simulation • To Evaluate and Verify the Design of the PWM Boost Converter. • To Optimize the Parameters of the PWM Boost Converter. 1 Setting PWM Controller’s Parameters: FOSC , VREF, VP 2 Setting Output Voltage: Rupper, Rlower 3 Inductor Selection: L 4 Capacitor Selection: C, ESR 5 Setting the Compensator Parameters: R2, C1, C2 Continue next slide All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 5

- 6. Boost Convertor Design Workflow Evaluations: • Switching Waveforms, • Power State Switches Voltage and Current, • Load Step Transient Response, • and so on Reliability: L sweep (example) Evaluations: • Converter Efficiency vs. MOSFET, Rds(on) • Converter Efficiency vs. Diode, VF Evaluations Using Real Device Models (as an Option) All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 6

- 7. Boost Convertor Design Workflow 3 D1 RLs L DIODE v out S1 S Vin + + pwm C - - R RON = 0.01 ESR 4 Type 3 Compensator* 0 C2 5 5 C1 R1 R2 err Rupper U1 PWM_IC C3 - + E/A + Rlower Comp - OSC 2 REF FOSC = {f osc} 0 1 Voltage Mode VREF = {Vref } VP = {Vp} All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 7

- 8. Design Specification (Example) A boost converter is designed to deliver 12V, 1.5A from a 3.3 V battery Step-Up (Boost) Converter : • Vin,max = 3.63 (V) Vin = 3.310% • Vin,min = 2.97 (V) • Vout = 12 (V) • Vout, ripple = 180mVP-P (1.2%) • Io,max = 1.5 (A) • Io,min = 0.2 (A) Control IC : • Part # TPS43000 (PWM Controller IC) • Switching Frequency – fosc = 300 (kHz) All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 8

- 9. 1 Setting PWM Controller’s Parameters U1 PWM_IC comp • FOSC, Oscillation frequency (frequency of the sawtooth signal). - FB PWM Comp + E/A + • VREF, feedback reference voltage, value is - OSC given by the datasheet REF FOSC = 300K • VP = the sawtooth peak voltage. VREF = 0.8 VP = 2.2 • If VP does not provided, it could be calculated from: The Comparator compares the error voltage VP = VFB /d (eq.1) (between FB and REF) with a sawtooth signal (frequency = FOSC, peak saw voltage = VFB = VFBH – vFBL VP) to generate PWM signal, as shown in the figure below. d = dMAX – dMIN where f = FOSC 3.0V vFBH is maximum FB voltage where d = 0 2.0V vFBL is minimum FB voltage where d =1(100%) SEL>> VP 0V dMAX is maximum duty cycle, e.g. d = 0(0%) V(osc) V(comp) dMIN is minimum duty cycle, e.g. d =1(100%) If vFBH and vFBL are not provided, the default value, VP=2 could be used. V(PWM) Duty cycle (d) is a value from 0 to 1 Time All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 9

- 10. 1 Setting PWM Controller’s Parameters (Example) The switching frequency 300kHz constant is chosen Input FOSC = 300k The VREF value is given by the datasheet TPS43000 electrical characteristics So we’ve got VREF = 0.8 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 10

- 11. 1 Setting PWM Controller’s Parameters (Example) The VP ( sawtooth signal amplitude ) can be calculated from the characteristics below. TPS43000 electrical characteristics from the (eq.1) VP = VFB /d • from the datasheet , VFB = (2-0) = 2V, and d = (0.9-0) = 0.9 VP = 2 / 0.9 = 2.2 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 11

- 12. 2 Setting Output Voltage: Rupper, Rlower • Use the following formula to select the resistor values. Rupper VOUT VREF 1 (eq.2) Rlower Example Given: Vout = 12V Vref = 0.8 Rlower = 10k then: (VOUT VREF ) Rlower Rupper VREF Rupper = 140k All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 12

- 13. 3 Inductor Selection: L, RLS Inductor Value • The output inductor value is selected to set the D1 RLs L DIODE converter to work in CCM (Continuous Current Mode) for all load current conditions. S1 S + + pwm C • Calculated by - - D min (1 D min) 2 VOUT R RON = 0.01 ESR LCCM (eq.3) 2 fosc IO , min Vin, min D max • with IL (eq.4) L fosc Where • LCCM is the inductor that make the converter to work in CCM. • Dmin is the minimum duty cycle; Dmin =1- Vin,max /VOUT • Dmax is the maximum duty cycle; Dmax =1- Vin,min /VOUT • RLs is load resistance at the minimum output current ( Io,min ) • fosc is switching frequency • IL is inductor ripple current All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 13

- 14. 3 Inductor Selection: L, RLS (Example) D1 Inductor Value RLs L DIODE S1 S + + pwm C from (eq.3) - - D min (1 D min) 2 VOUT R RON = 0.01 ESR LCCM 2 fosc IO , min Given: • Vin,max = 3.63V (3.3V+10%), Vout = 12V, Io,min = 0.2A • Dmin = 1- Vin,max /Vout = 0.7 • fosc = 300kHz Then: • LCCM 6.4 (uH), • L = 6.8 (uH) is selected All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 14

- 15. 4 Capacitor Selection: C, ESR D1 RLs L DIODE Capacitor Value S1 S • The minimum allowable output capacitor + + pwm C value should be determined by - - D max Io, max R RON = 0.01 ESR C (eq.5) Vout, ripple fOSC • In addition, the capacitor must be able to handle the current more than IL IC , Rated (eq.6) 2 • Where IL is calculated by the (eq.4) • The ESR of the output capacitor adds some more ripple, so it should be limited by following equation: Vout , ripple ESR (eq.7) IC All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 15

- 16. 4 Capacitor Selection: C, ESR (Example) D1 DIODE Capacitor Value 1 S From the (eq.5) D max Io, max pwm C C Vout, Ripple fOSC + - R ON = 0.01 ESR and the (eq.6) and (eq.7) IL Vout , ripple IC ESR 2 IC Given: • Dmax = 0.75 V • Io, max = 1.5 A • Vout,ripple = 0.18 V Then: • C 20.9 (F) In addition: • IC,Rated ≈ 550mA ESR 27m All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 16

- 17. 5 Stabilizing the Converter • Loop gain for this configuration is RLs L D1 DIODE Power stage: H(s) S1 S Vin + + pwm C - - R T ( s) H ( s) G ( s) GPWM RON = 0.01 ESR Compensator: G(s) Type 3 Compensator v out C2 0 C1 R1 err R2 Rupper • The purpose of the compensator G(s) U1 PWM_IC C3 is to tailor the converter loop gain - + (frequency response) to make it stable Comp E/A + Rlower - OSC when operated in closed-loop GPWM REF conditions. FOSC = {f osc} VREF = {Vref } 0 VP = {Vp} • The element of the Type 3 compensator (C1, C2 , C3 , R1, and R2 ) can be extracted by using Boost_Calculator.xls (Excel sheet) and open-loop simulation with the Average Models (ac models). Remark: The Average Models are not included with this package. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 17

- 18. 4.Boost Converter Simulation (Example) RLs L D1 10m 6.8u DIODE Specification: v out VIN = 3.3V 10% S1 S ESR + pwm 27m VOUT = 12V Vin 3.3 - + - R 12 IOUT = 0.2 ~ 1.5A RON = 0.01 C 1410u PWM Controller: C2 2 0 795p fOSC = 300kHz R2 VREF = 0.8V Characteristics from err C1 R1 Rupper 4.9k VP1 = 2.2V Texas Instruments IC: U1 8.259n 47.9k 140k C3 TPS43000. PWM_IC 2.826nF - Rlower = 10k, Comp + E/A + - Rlower Rupper = 140k, OSC REF 10k L = 6.8uH (RLS=10m ), FOSC = 300k VREF = 0.8 0 C = 1410uF (ESR = 27m), VP = 2.2 *Analysis directives: .TRAN 0 10ms 0ms 100n .OPTIONS ABSTOL= 1.0n .OPTIONS CHGTOL= 0.01u Task: .OPTIONS ITL1= 200 .OPTIONS ITL2= 100 •Voltage and Current Waveforms Evaluation. .OPTIONS ITL4= 50 .OPTIONS RELTOL= 0.01 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 18

- 19. 4.1 Switching Waveforms 5.0V Control Voltage V(PWM) 0V v(pwm) 5.0A Switch Current ID(S1) 2.5A 0A I(S1:3) 5.0A Inductor Current I(L) 2.5A 0A I(L) 12.2V (9.982m,12.086) 12.1V VOUT, RIPPLE 12.0V SEL>> (9.986m,11.970) 11.8V 9.980ms 9.984ms 9.988ms 9.992ms 9.996ms 10.000ms v(vout) Time • The simulation results shows waveforms of the boost converter. • Output ripple voltage (caused by ESR) = 116mVP-P. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 19

- 20. 4.2 Power State Switches Voltage and Current 16V 6.0A 1 2 (9.992m,12.095) (9.996m,4.3125) SW (MOSFET) Voltage VDS 12V 4.5A 8V 3.0A SW (MOSFET) Current ID 4V 1.5A SEL>> 0V 0A 1 V(S1:3,S1:4) 2 I(S1:3) 16V 5.0A 1 2 Diode Forward Current IF 8V 2.5A (9.996m,4.3554) 0V 0A (9.993m,-11.940) -8V -2.5A Diode Voltage VAK >> -16V -5.0A 9.990ms 9.992ms 9.994ms 9.996ms 9.998ms 10.000ms 1 V(D1:A,D1:C) 2 I(D1) Time • Switch (MOSFET) has the steady state voltage: VDS, PEAK = 12.095V and current: ID, PEAK = 4.312A • Diode has the steady state voltage: VAK, PEAK = -11.940V and current: IF, PEAK = 4.355A All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 20

- 21. 5.Load Transient Response Simulation (Example) The converter are connected with step-load to perform load transient response simulation. RLs L D1 10m 6.8u DIODE v out S1 S ESR + pwm 27m I1 = 0.2 I1 Vin + I2 = 1.5 3.3 - - TD = 19m RON = 0.01 TR = 10u C TF = 10u 1410u PW = 2m PER = 1 Iload = 0.2A C2 step to 1.5A 0 795p R2 C1 R1 4.9k err Rupper 140k U1 8.259n 47.9k C3 PWM_IC 2.826nF *Analysis directives: - + E/A .TRAN 0 26ms 18ms 100n Comp + Rlower - .OPTIONS ABSTOL= 1.0n OSC REF 10k .OPTIONS CHGTOL= 0.01u FOSC = 300k .OPTIONS ITL1= 200 VREF = 0.8 0 VP = 2.2 .OPTIONS ITL2= 100 .OPTIONS ITL4= 50 .OPTIONS RELTOL= 0.01 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 21

- 22. 5.Load Transient Response Simulation (Example) 2.0A 1.6A 0.2-1.5A Step load current 1.2A 0.8A 0.4A 0A I(I1) 12.2V Output Voltage Change 12.1V (21.022m,12.162) 12.0V 11.9V SEL>> (19.099m,11.912) 11.8V 18ms 20ms 22ms 24ms 26ms v(vout) Time • The simulation results shows output voltage change waveforms caused by step load current. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 22

- 23. 6.Boost Converter Reliability Testing (Example) RLs L D1 Specification: 10m {L} DIODE v out VIN = 3.3V 10% PARAMETERS: L = 6.8u S1 S ESR VOUT = 12V Vin + + pwm 27m R 3.3 - - IOUT = 0.2 ~ 1.5A RON = 0.01 60 C 1410u Iload, min PWM Controller: 2 = 0.2A C2 fOSC = 300kHz 0 795p R2 VREF = 0.8V C1 R1 4.9k err Rupper VP1 = 2.2V 140k U1 8.259n 47.9k C3 PWM_IC 2.826nF Rlower = 10k, - + E/A + Comp Rupper = 140k, - OSC Rlower 10k REF L = Swept parameter (RLS=10m ), FOSC = 300k 0 C = 1410uF (ESR = 27m), VREF = 0.8 VP = 2.2 *Analysis directives: .TRAN 0 20ms 0 100n .STEP PARAM L LIST 6.8u, 5.78u .OPTIONS ABSTOL= 1.0n Task: .OPTIONS CHGTOL= 0.01u • To check that the converter still work in CCM .OPTIONS ITL1= 200 .OPTIONS ITL2= 100 after 15% reduction of the inductor value. .OPTIONS ITL4= 50 .OPTIONS RELTOL= 0.01 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 23

- 24. 6.Boost Converter Reliability Testing (Example) 5.0V L=6.8uH A: V(PWM), L=5.78uH 0V v(pwm) 2.0A B: ID(S1) 1.0A 0A I(S1:3) 1.6A C: I(L) 0.8A 0A I(L) the converter works in CCM (no zero current) at L=5.78uH. 12.04V D: VOUT, RIPPLE SEL>> 11.98V 19.990ms 19.992ms 19.994ms 19.996ms 19.998ms 20.000ms v(vout) Time • The simulation results shows waveforms of the converter at L=6.8uH and 5.78uH • At L = 5.78uH(-15%), the converter still work in CCM All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 24

- 25. 7.1 Converter Efficiency vs. MOSFET Rds(on) Perform transient simulation to measure the converter efficiency at Rds(on)= 0.01 and 0.1 . RLs L D1 10m 6.8u DIODE v out S1 S ESR Vin PARAMETERS: + + pwm 27m Rdson = 0.1 R 3.3 - - 12 RON = {Rdson} C 1410u C2 0 795p R2 C1 R1 4.9k err Rupper 140k *Analysis directives: U1 8.259n 47.9k C3 .TRAN 0 20ms 18.8m 100n PWM_IC 2.826nF .STEP PARAM Rdson LIST 0.01, 0.1 - .OPTIONS ABSTOL= 1.0n + E/A .OPTIONS CHGTOL= 0.01u Comp + Rlower .OPTIONS ITL1= 200 - OSC 10k REF .OPTIONS ITL2= 100 .OPTIONS ITL4= 50 FOSC = 300k .OPTIONS RELTOL= 0.01 VREF = 0.8 0 VP = 2.2 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 25

- 26. 7.1 Converter Efficiency vs. MOSFET Rds(on) Efficiency (%) 100 Rds(on) = 0.01, Efficiency = 97.3 % (19.750m,97.343) 90 Rds(on) = 0.1, Efficiency = 88.6 % (19.750m,88.600) 80 70 60 Rds(on) = 0.01 Rds(on) = 0.1 50 19.50ms 19.55ms 19.60ms 19.65ms 19.70ms 19.75ms 19.80ms 19.85ms 19.90ms 19.95ms 100*AVG(W(R))/AVG(-W(Vin)) Time • The converter efficiency is decreased from 97.3% to 88.6% when Rds(on) increase from 0.01 to 0.1. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 26

- 27. 7.2 Converter Efficiency vs. Diode, VF Perform transient simulation to measure the converter efficiency at DIODE (N) = 0.01 and 0.4 PARAMETERS: N = 0.01 RLs L D1 Diode Forward Voltage vs. 10m 6.8u DIODE v out Diode model parameter: N S1 S ESR + pwm 27m Vin + R 3.3 - - Diode Forward I – V Characteristics RON = 0.01 12 1.0A C VF increases when DIODE (N) increases. 1410u 0.9A 0.8A C2 0.7A 0 795p 0.6A R2 C1 R1 4.9k 0.5A err Rupper 0.4A 140k U1 8.259n 47.9k C3 0.3A PWM_IC 2.826nF 0.2A - *Analysis directives: + E/A 0.1A VF .TRAN 0 20ms 18.8m 100n + Comp - Rlower OSC 10k 0A 0V 0.12V 0.24V 0.36V 0.48V 0.60V 0.72V 0.84V 0.96V 1.08V .STEP PARAM N LIST 0.01, 0.4 REF I(D1) V_V1 .OPTIONS ABSTOL= 1.0n FOSC = 300k .OPTIONS CHGTOL= 0.01u VREF = 0.8 0 .OPTIONS ITL1= 200 VP = 2.2 .OPTIONS ITL2= 100 .OPTIONS ITL4= 50 .OPTIONS RELTOL= 0.01 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 27

- 28. 7.2 Converter Efficiency vs. Diode, VF Efficiency (%) 100 DIODE (N) = 0.01, Efficiency = 97.3 % (19.750m,97.343) (19.750m,94.663) DIODE (N) = 0.4, Efficiency = 94.6 % 90 80 70 60 50 19.50ms 19.55ms 19.60ms 19.65ms 19.70ms 19.75ms 19.80ms 19.85ms 19.90ms 19.95ms 100*AVG(W(R))/AVG(-W(Vin)) Time • The converter efficiency is decreased from 97.3% to 94.7% when DIODE’s parameter N increase from 0.01 to 0.4 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 28

- 29. 8.Simulation Using Real Device Models (Example) As we can see in the efficiency simulation (topic #7) that’s how the switching devices effect the simulation result. For the accurate simulation result, the accurate models, that relate to the real devices characteristics, are needed. The Real Device Models of Schottky Diode (Shindengen RLs 10m L 6.8u SBD Part# M2FM3) D1 v out M2FM3 ESR Vin 27m pwm R 3.3 12 U2 C TPC6005S 1410u C2 0 795p The Real Device Models of C1 R1 R2 4.9k MOSFET (Toshiba N Channel err Rupper 140k MOS Part# TPCP6005) U1 8.259n 47.9k C3 PWM_IC 2.826nF - + E/A + Comp - Rlower OSC 10k REF FOSC = 300k VREF = 0.8 0 VP = 2.2 All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 29

- 30. 8.Simulation Using Real Device Models (Example) 5.0V 0V V(PWM) Spike current 6.0A 4.0A 2.0A 0A -2.0A I(U2:1) 6.0A 4.0A 2.0A 0A I(L) 12.1V 12.0V SEL>> 11.9V 9.980ms 9.985ms 9.990ms 9.995ms 10.000ms V(VOUT) Time • The real device model enable designers to include the spike signal (caused by the devices’ parasitic capacitance) in the switching waveforms simulation. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 30

- 31. 8.2 Converter Efficiency (Real Device Models) Efficiency (%) 100 Efficiency = 89.97 % (9.500m,89.973) 90 80 70 60 50 9.0ms 9.1ms 9.2ms 9.3ms 9.4ms 9.5ms 9.6ms 9.7ms 9.8ms 9.9ms 10.0ms 100* AVG(W(R))/ AVG(-W(Vin)) Time • The converter efficiency is decreased from 97.3% to 89.97% when the device models are changed from the near-Ideal to the real model. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 31

- 32. 9.SpicePark of MOSFET Model Maximum Value Device Models • After the device voltage and current condition is simulated (e.g. VDS, PEAK=12.095V and ID, PEAK=4.312A), The real device models could be picked up from the SpicePark, that is the resource of device models, provided by Bee Technologies. All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 32

- 33. Simulation Index Simulations Folder name 1. Switching Waveforms...................................................... waveforms 2. Power Stage Switches Voltage and Current.................... powersw 3. Load Transient Response................................................ stepload 4. Boost Converter Reliability Testing................................... optimize 5. Converter Efficiency vs. MOSFET Rds(on) .................... efficiency-rdson 6. Converter Efficiency vs. MOSFET Diode, VF.................. efficiency-diode Libraries : 1. ..pwmic.lib 2. ..diode.lib All Rights Reserved Copyright (C) Bee Technologies Corporation 2011 33