1. The document provides an overview of the ARM architecture, including details on registers, exceptions, interrupts, memory management and instructions.

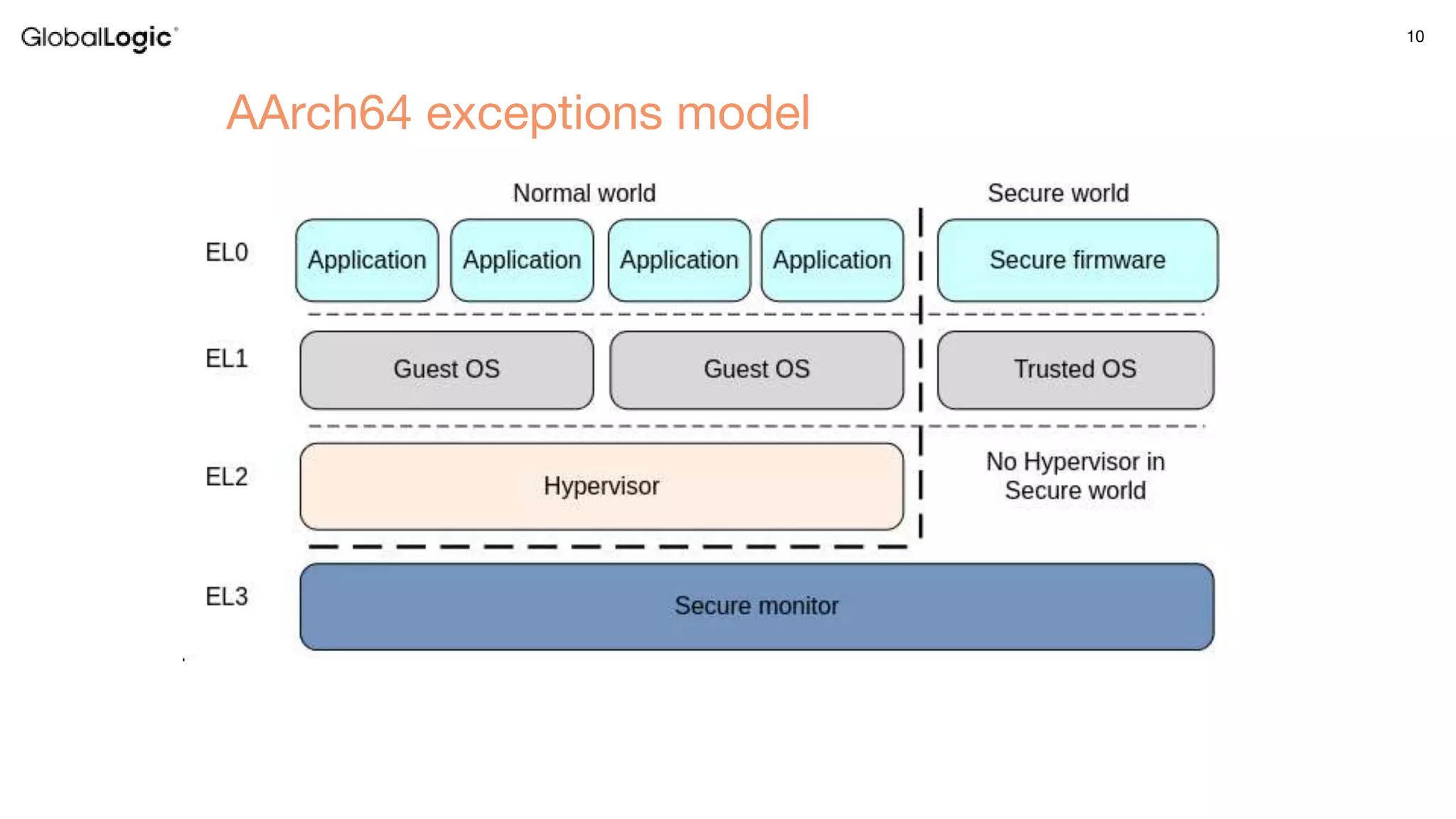

2. It describes the evolution of the ARM architecture from ARMv7 to AArch64 (ARMv8), noting changes in registers and exception handling between the versions.

3. The document also covers memory management features like MMU support, different memory types (normal vs device memory), and caching behavior in the ARM architecture.