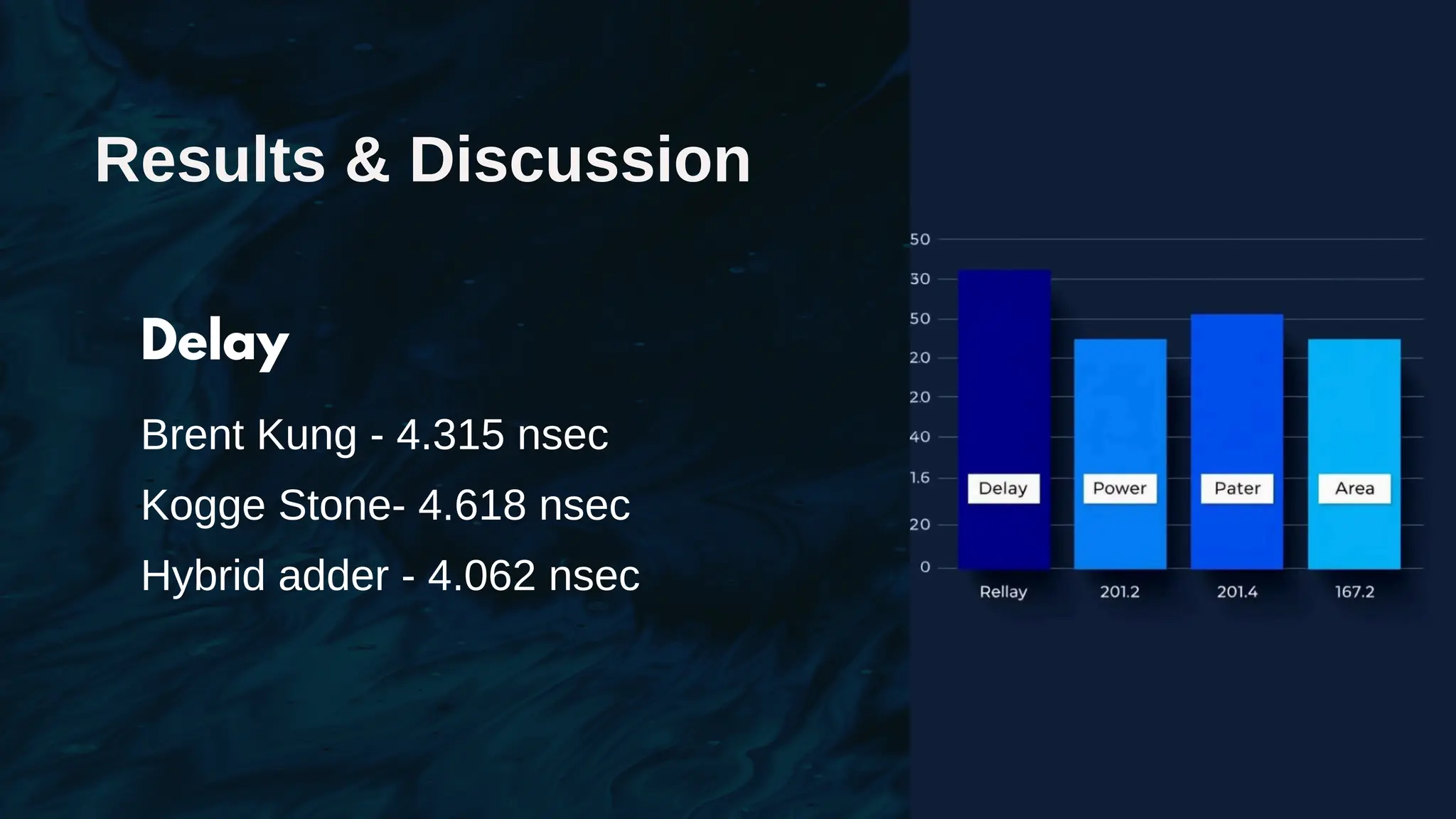

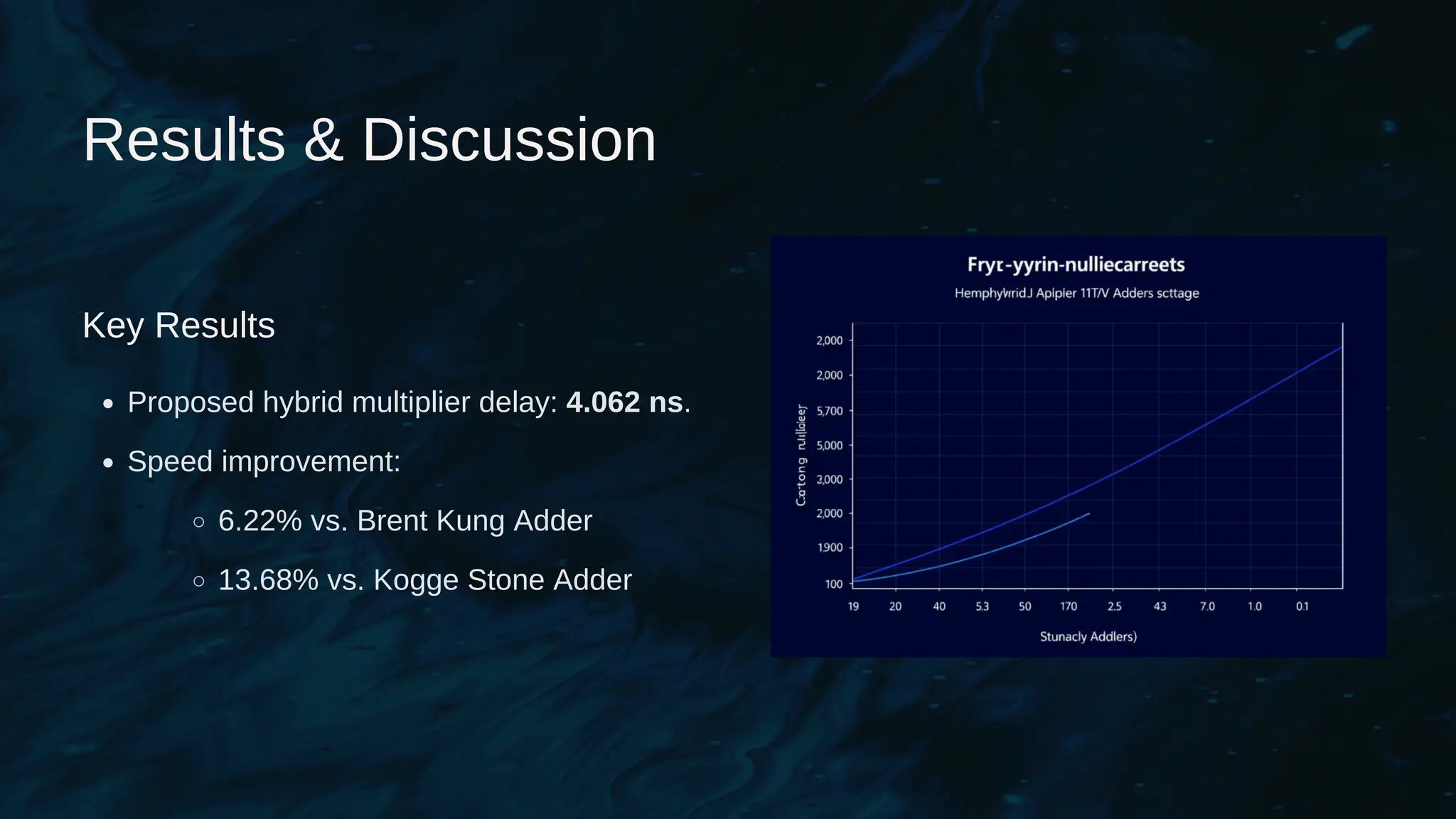

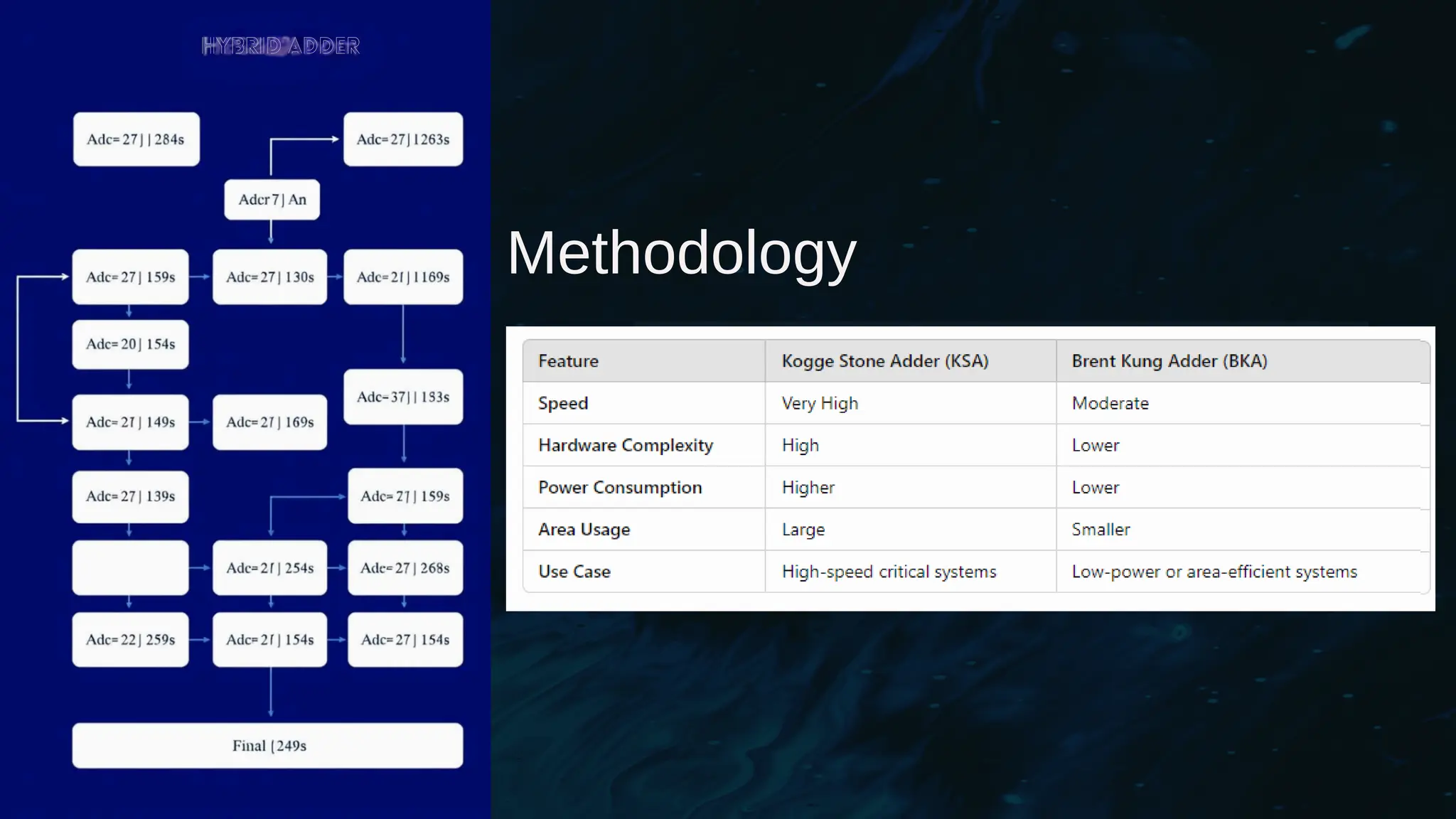

The document presents a seminar on a novel high-speed multiplier design using a hybrid adder technique, addressing challenges associated with multiplier designs. It includes details on methodology, FPGA implementation, and performance analysis, showing that the hybrid multiplier outperforms traditional adders like Brent Kung and Kogge Stone in terms of speed and delay. Future work aims to reduce logic complexity while maintaining efficiency.

![8-bit Hybrid Adder [1]

Designed for smaller data sizes.

Cout](https://image.slidesharecdn.com/presentataion-241025133209-0b9090e4/75/A-Novel-Design-of-High-Speed-Multiplier-Using-Hybrid-Adder-Technique-A-Seminar-Presentation-on-7-2048.jpg)

![12-bit Hybrid Adder [1]

Mid-range data size.](https://image.slidesharecdn.com/presentataion-241025133209-0b9090e4/75/A-Novel-Design-of-High-Speed-Multiplier-Using-Hybrid-Adder-Technique-A-Seminar-Presentation-on-8-2048.jpg)

![16-bit Hybrid Adder [1]

Designed for larger data sizes.](https://image.slidesharecdn.com/presentataion-241025133209-0b9090e4/75/A-Novel-Design-of-High-Speed-Multiplier-Using-Hybrid-Adder-Technique-A-Seminar-Presentation-on-9-2048.jpg)

![Step 1

AND operation of input bits.

Step 2

Generation of partial products.

Step 3

Addition of partial products using a

hybrid adder.

Fig -Partial Product Generation [1]](https://image.slidesharecdn.com/presentataion-241025133209-0b9090e4/75/A-Novel-Design-of-High-Speed-Multiplier-Using-Hybrid-Adder-Technique-A-Seminar-Presentation-on-10-2048.jpg)