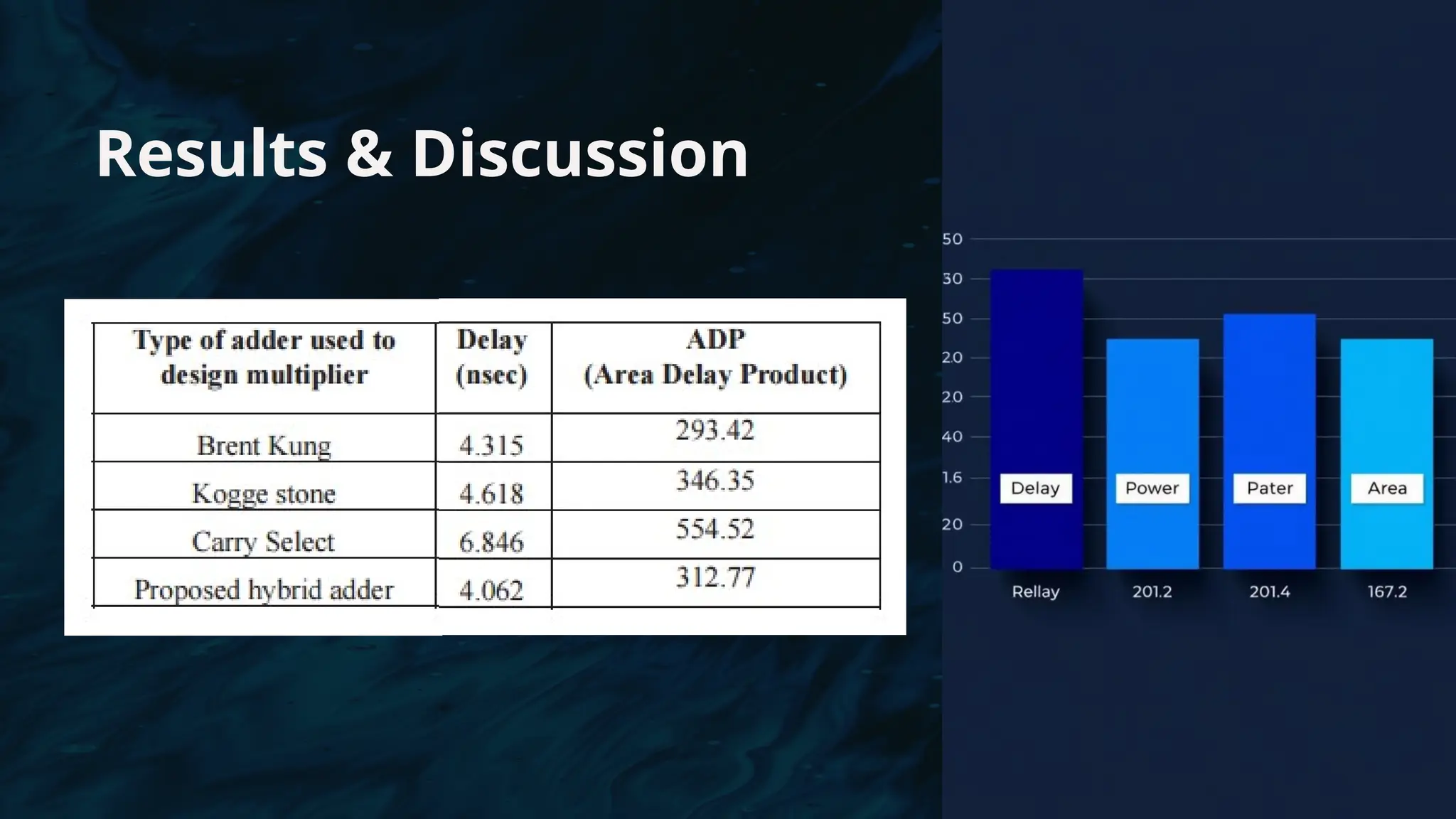

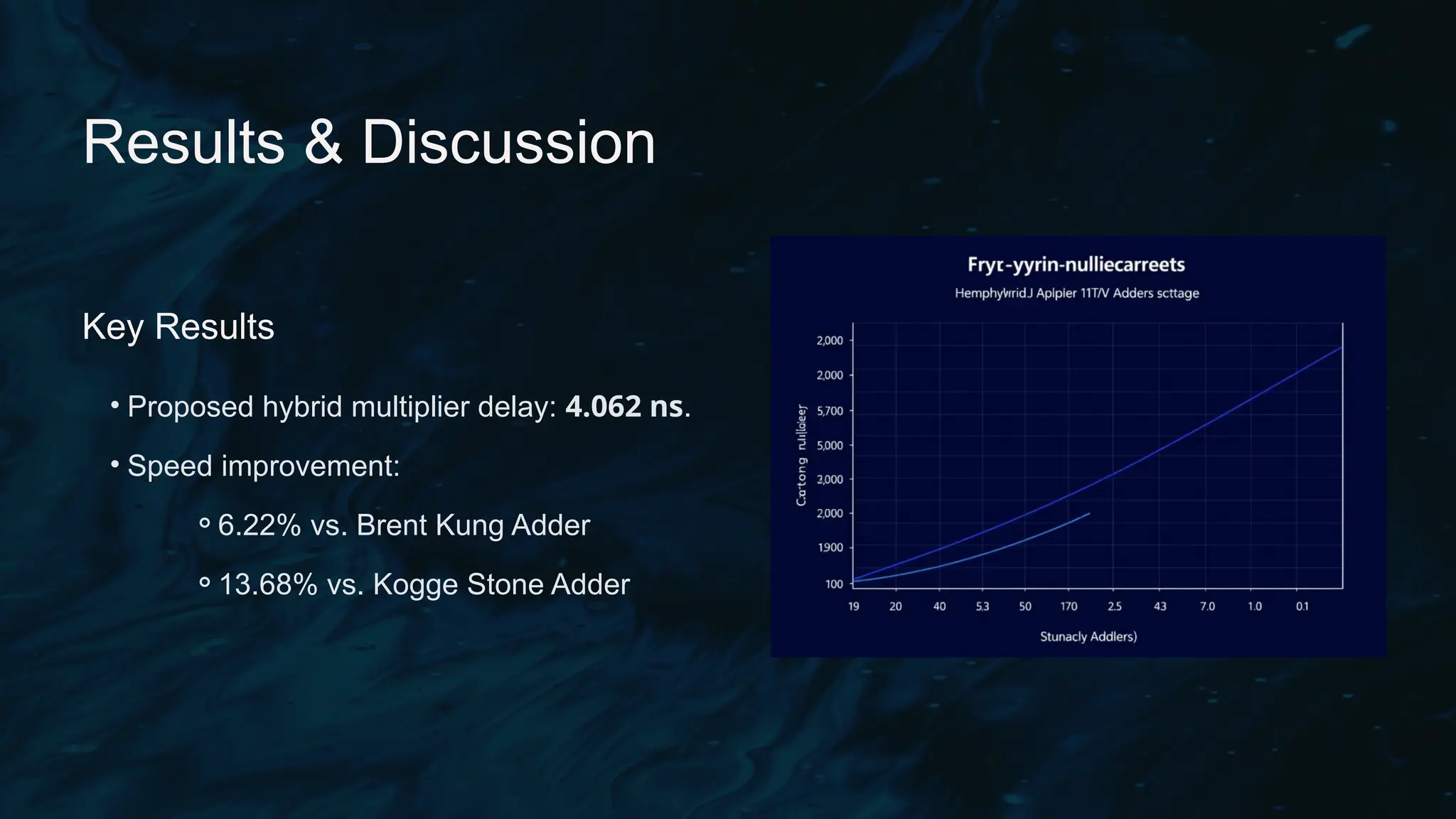

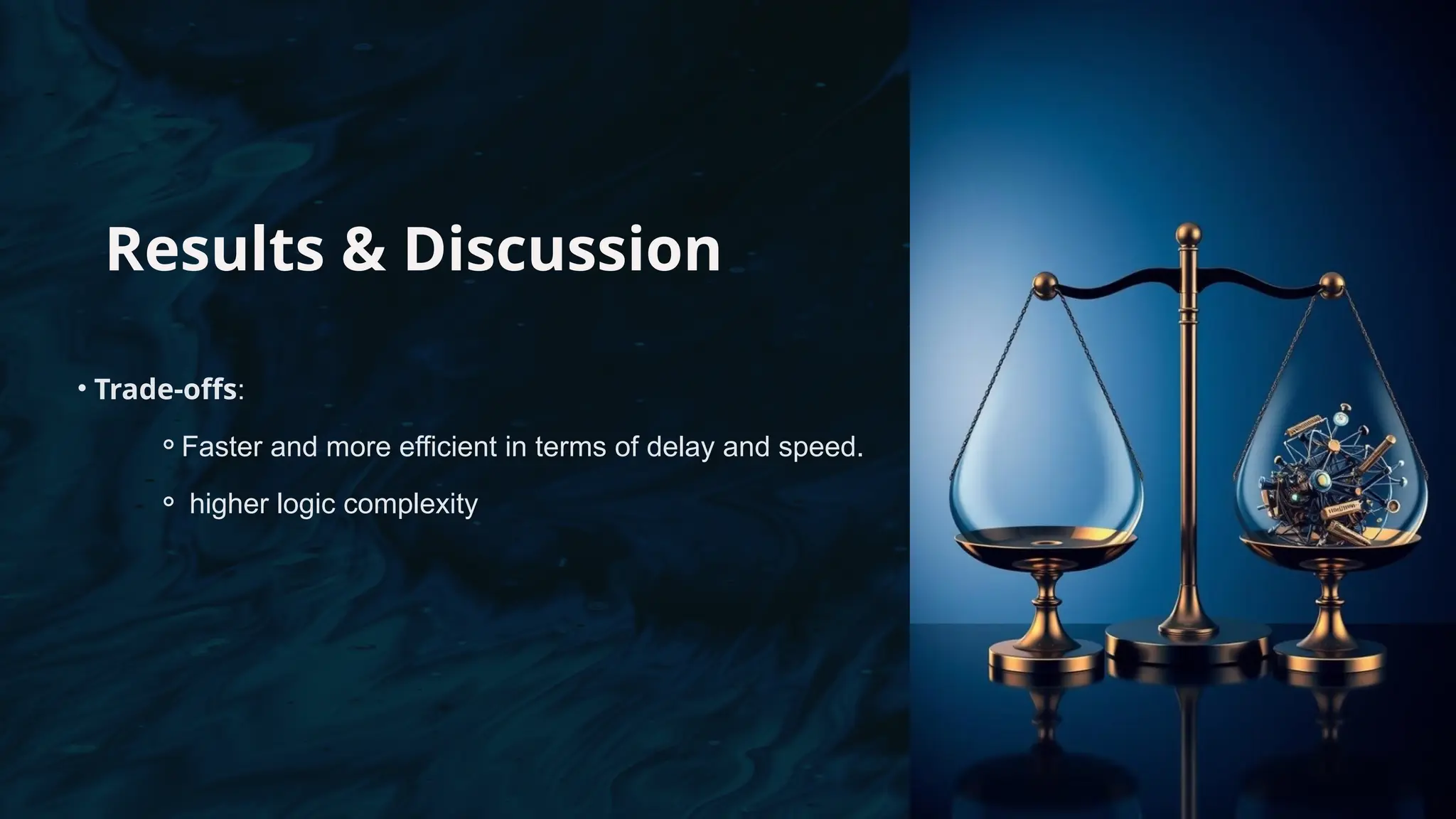

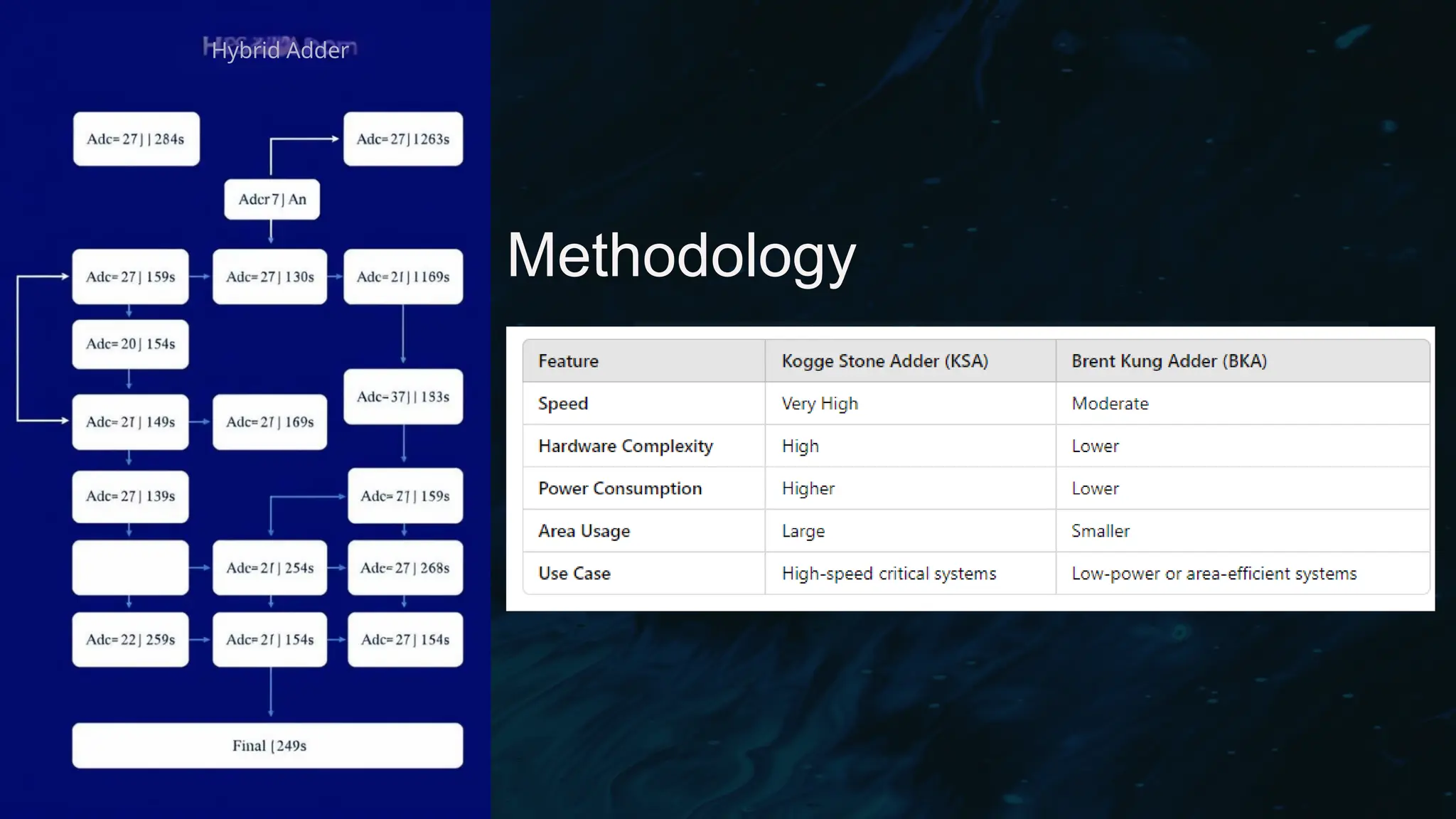

The document presents a seminar on designing a high-speed multiplier using a hybrid adder framework, highlighting the importance of multipliers and their applications. It discusses the methodology involving a hybrid adder and FPGA implementation, along with performance analysis showing speed improvements and trade-offs in complexity. The conclusion indicates that the hybrid adder design achieves lower delay and higher speed efficiency, with future work aimed at reducing logic complexity.

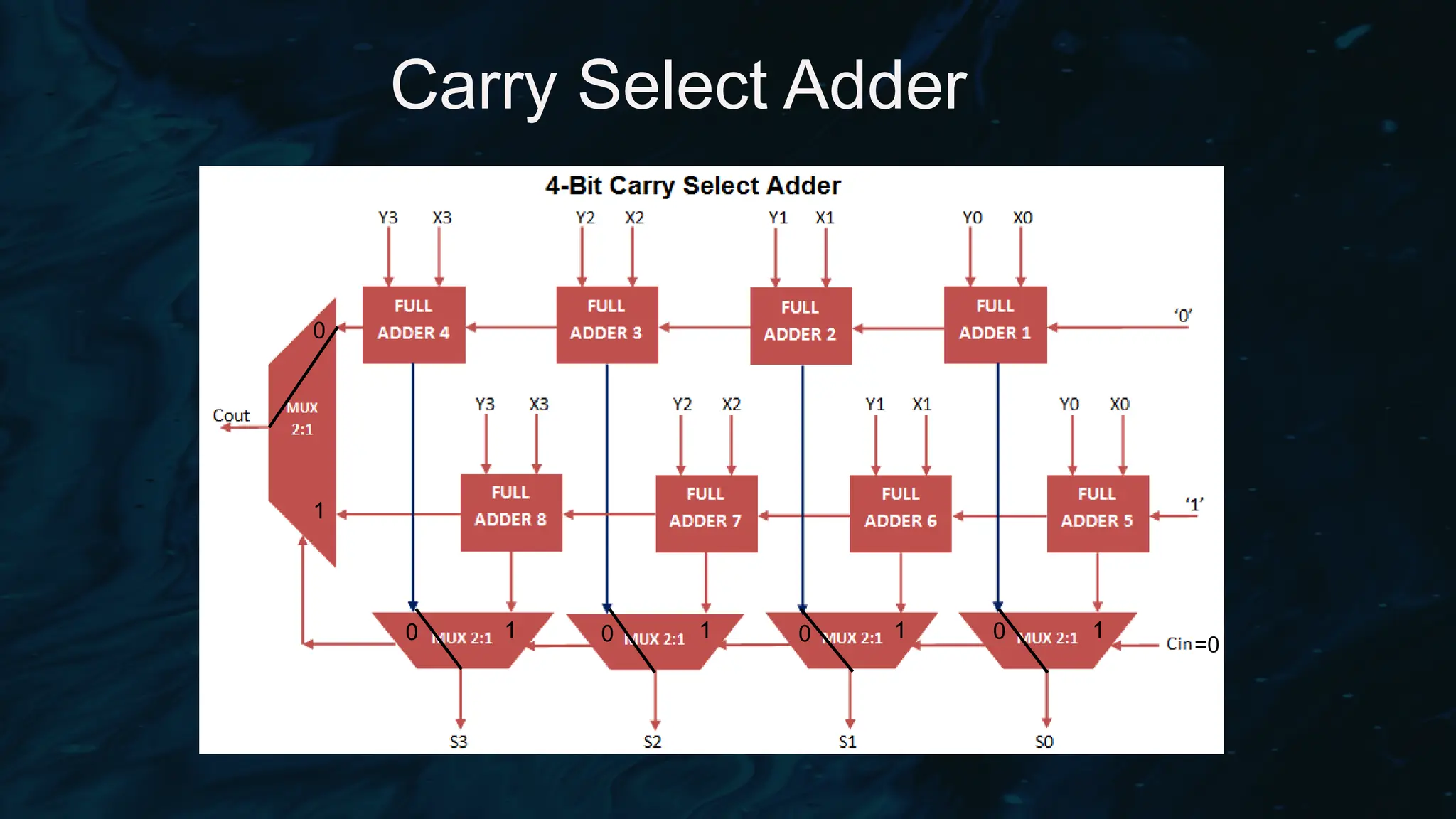

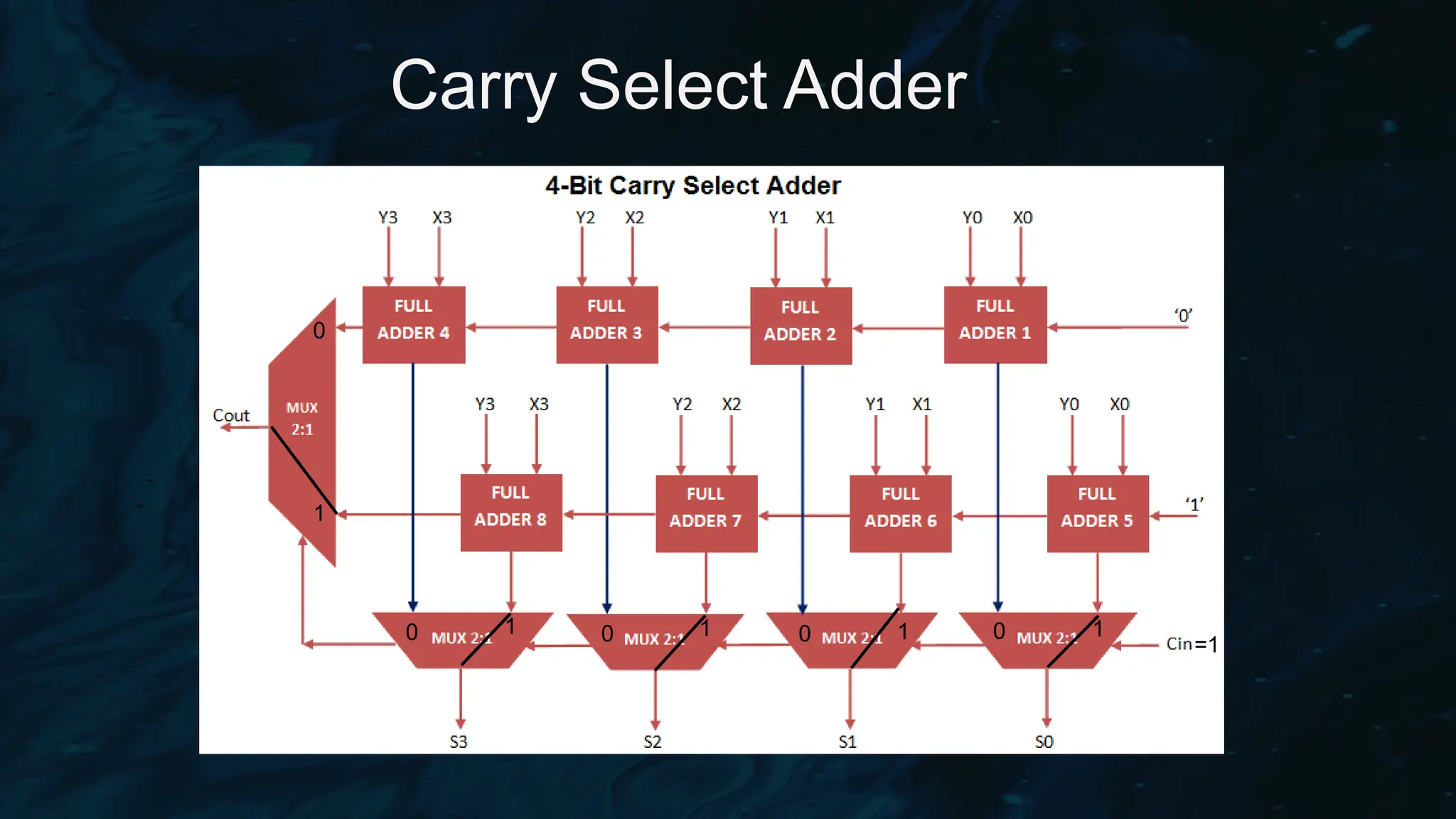

![Carry Select Adder

[1

]](https://image.slidesharecdn.com/anirbannath-241121141403-91f996d1/75/A-Seminar-on-High-Speed-Multiplier-Design-Using-Hybrid-Adder-Framework-6-2048.jpg)

![8-bit Hybrid Adder [1]

Designed for smaller data sizes.

Cou

t](https://image.slidesharecdn.com/anirbannath-241121141403-91f996d1/75/A-Seminar-on-High-Speed-Multiplier-Design-Using-Hybrid-Adder-Framework-16-2048.jpg)

![12-bit Hybrid Adder [1]

Mid-range data size.](https://image.slidesharecdn.com/anirbannath-241121141403-91f996d1/75/A-Seminar-on-High-Speed-Multiplier-Design-Using-Hybrid-Adder-Framework-17-2048.jpg)

![16-bit Hybrid Adder [1]

Designed for larger data sizes.](https://image.slidesharecdn.com/anirbannath-241121141403-91f996d1/75/A-Seminar-on-High-Speed-Multiplier-Design-Using-Hybrid-Adder-Framework-18-2048.jpg)

![Step 1

AND operation of input bits.

Step 2

Generation of partial products.

Step 3

Addition of partial products using a

hybrid adder.

Fig -Partial Product Generation

[1]](https://image.slidesharecdn.com/anirbannath-241121141403-91f996d1/75/A-Seminar-on-High-Speed-Multiplier-Design-Using-Hybrid-Adder-Framework-19-2048.jpg)