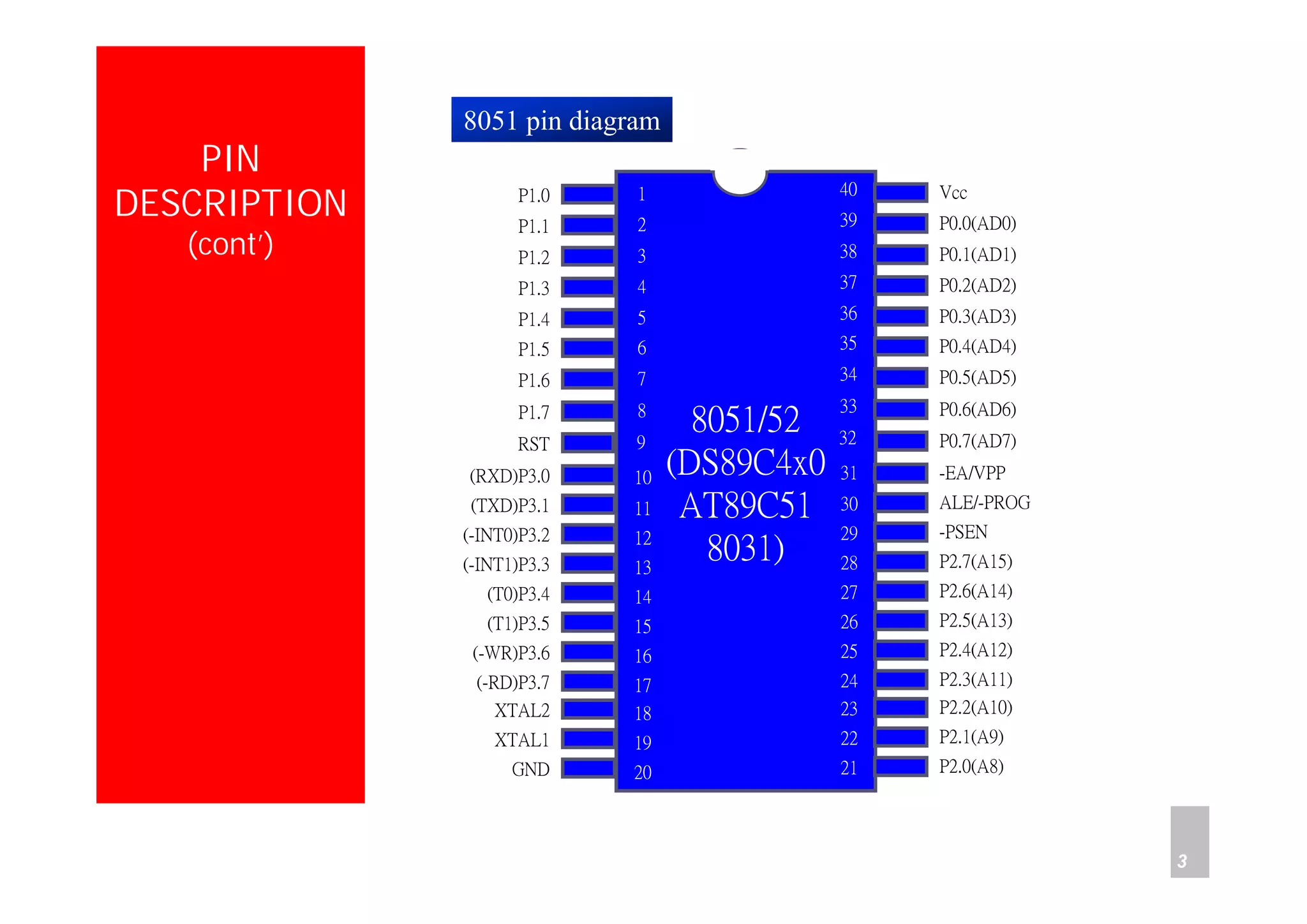

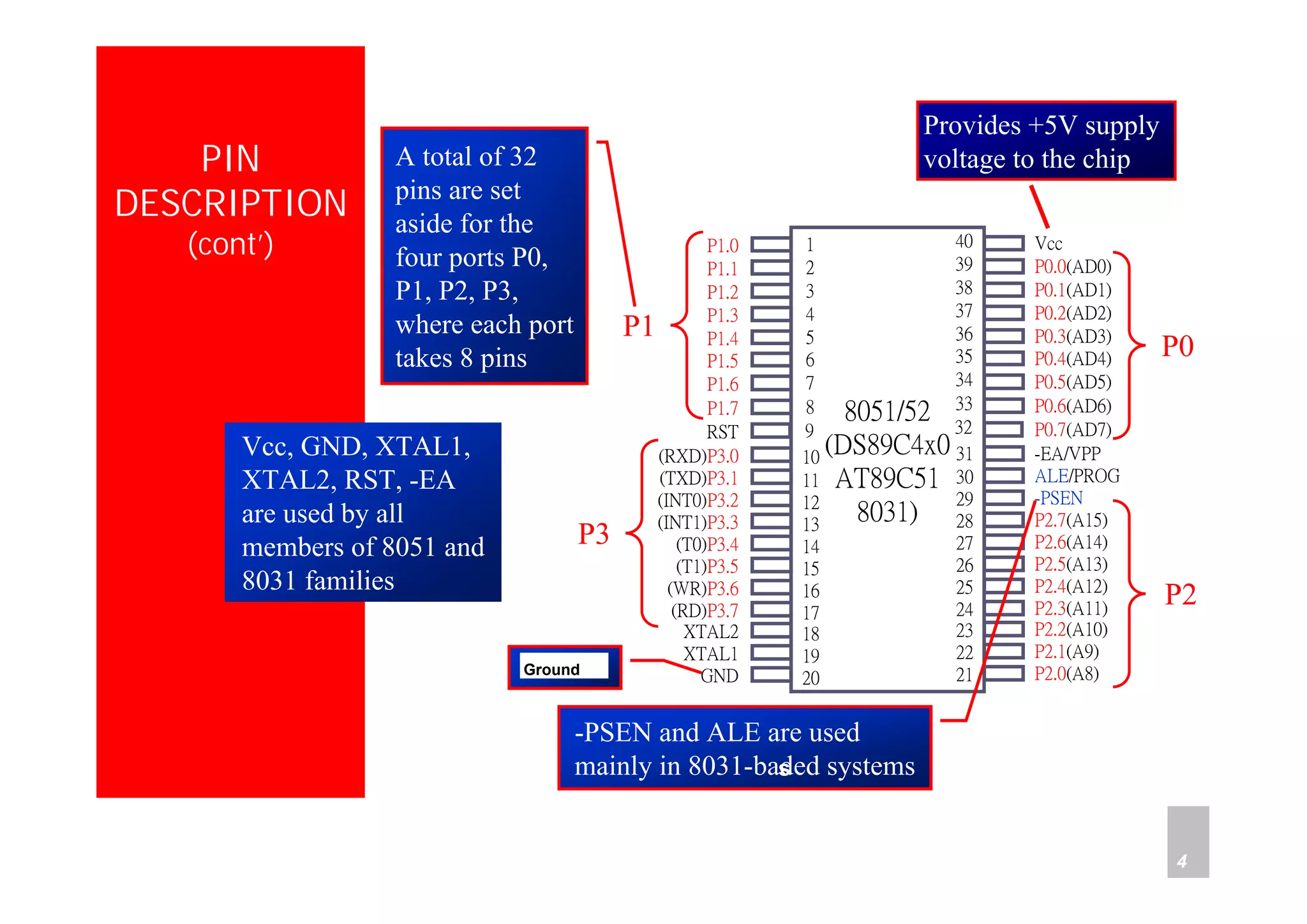

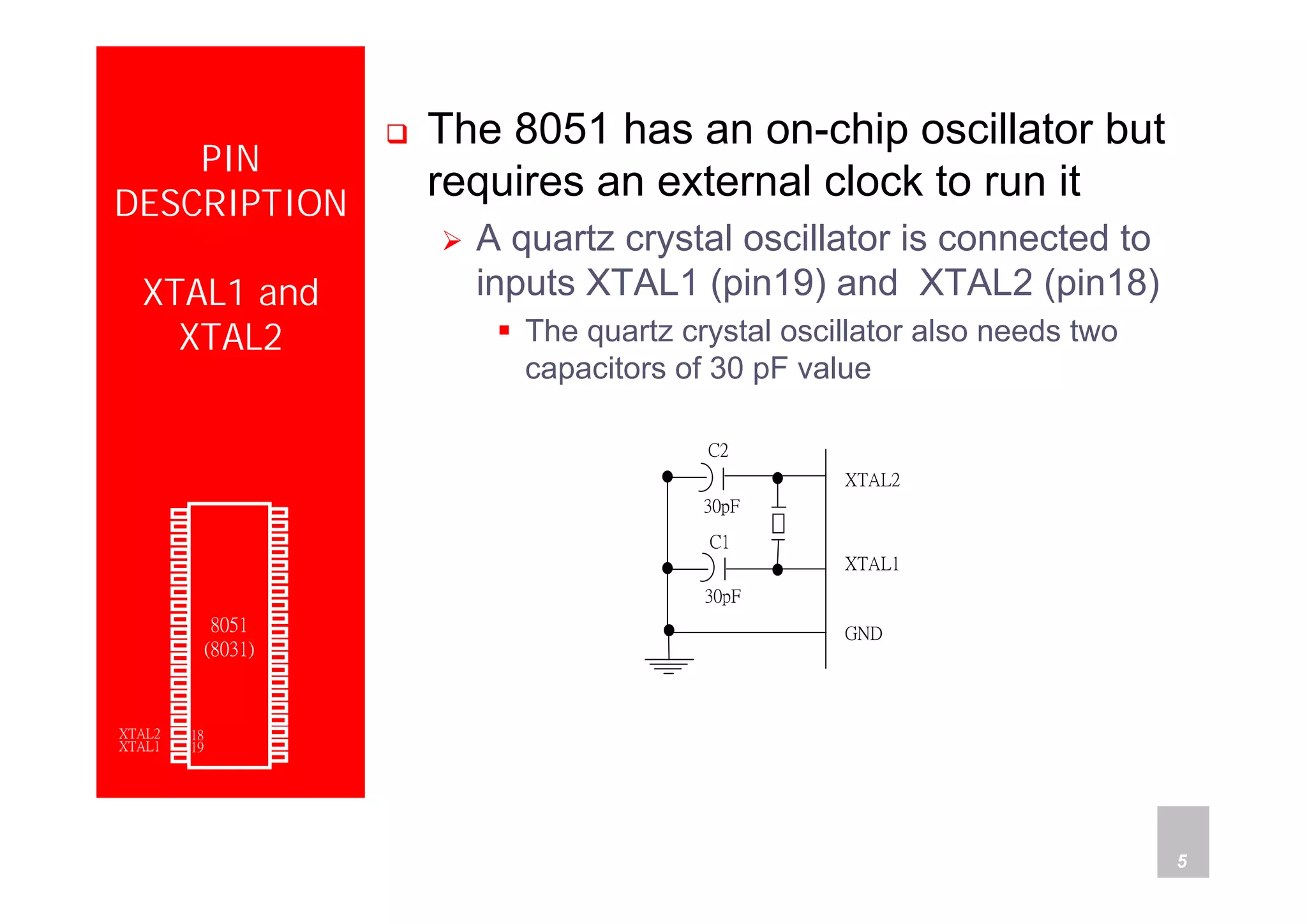

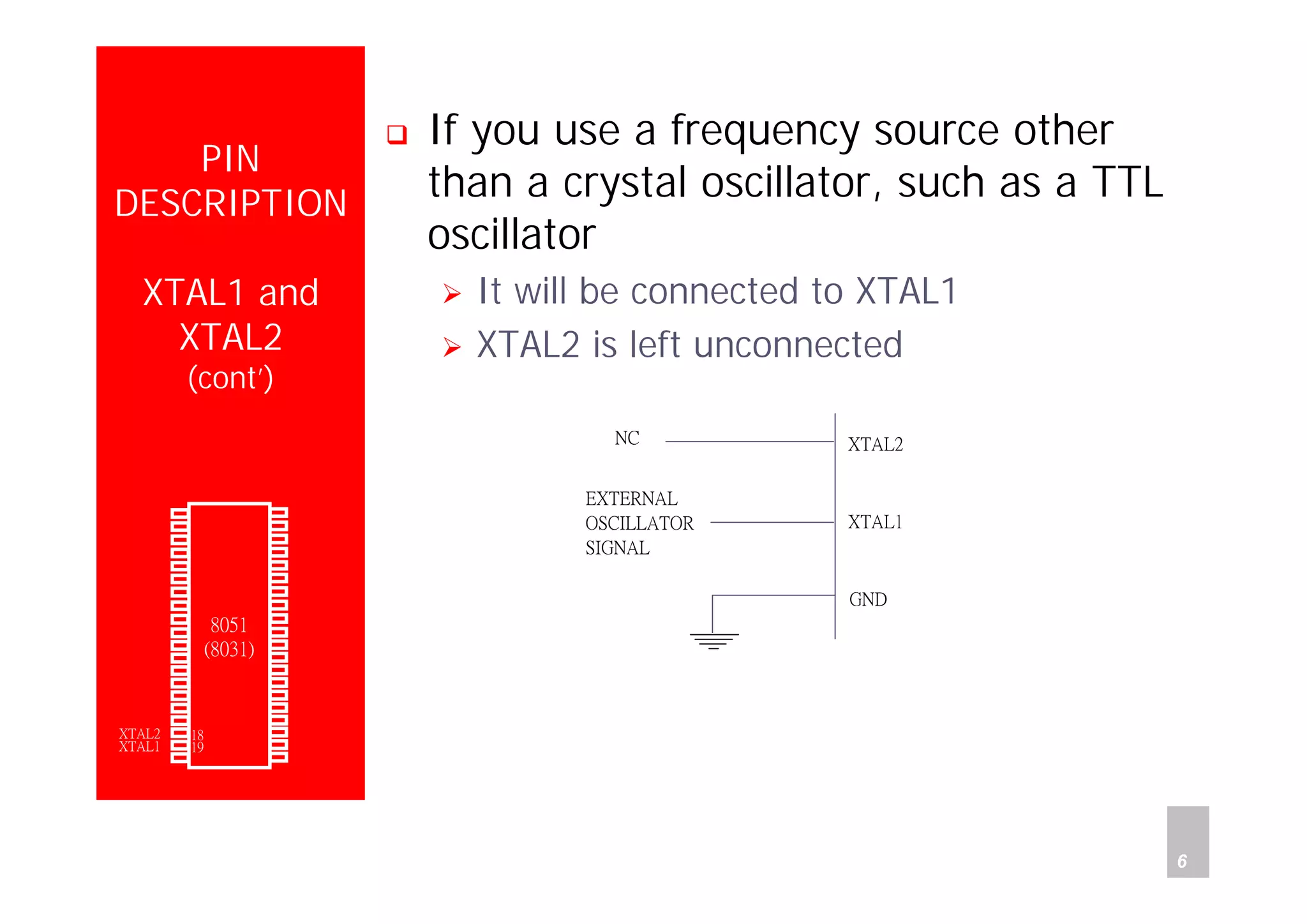

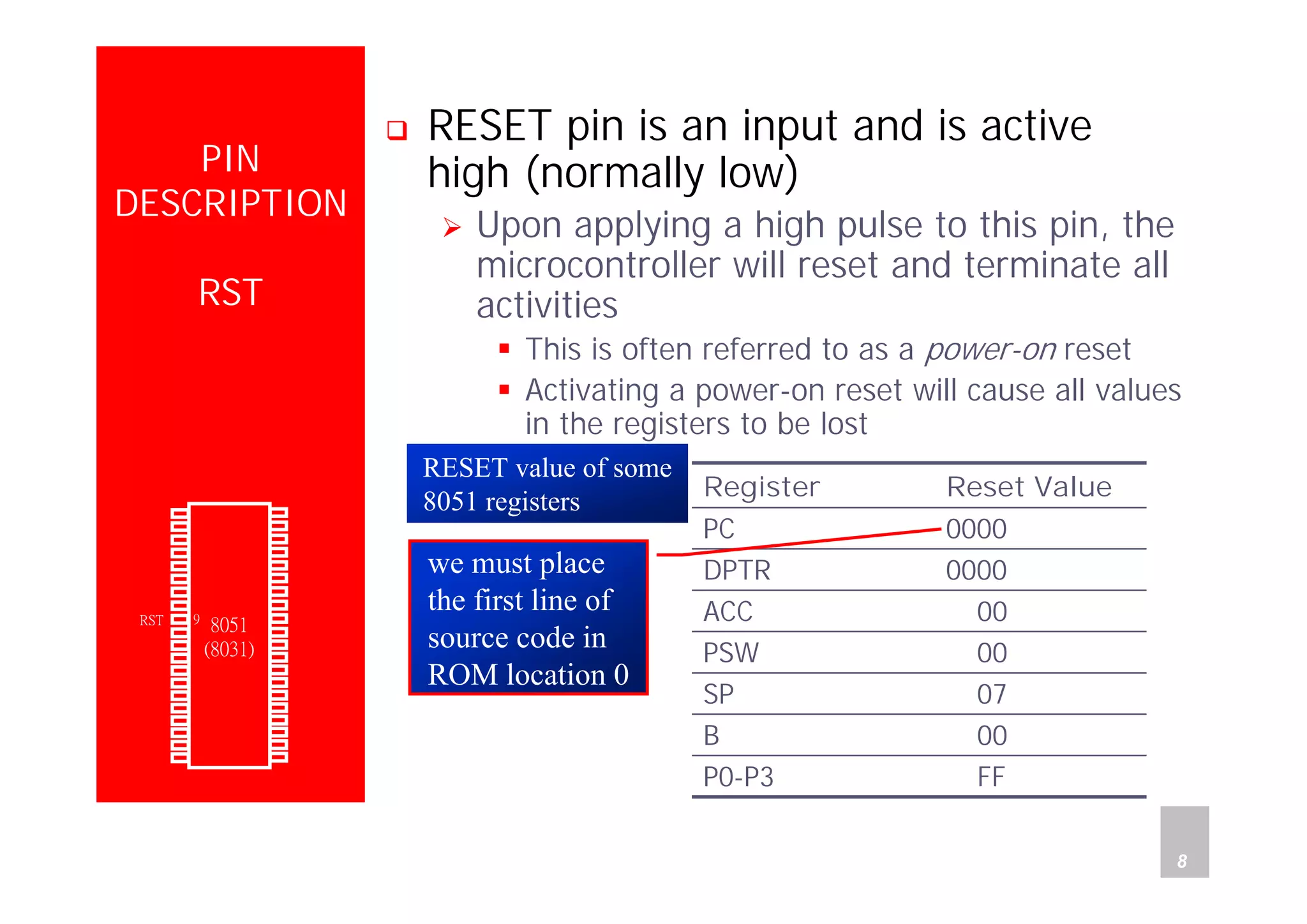

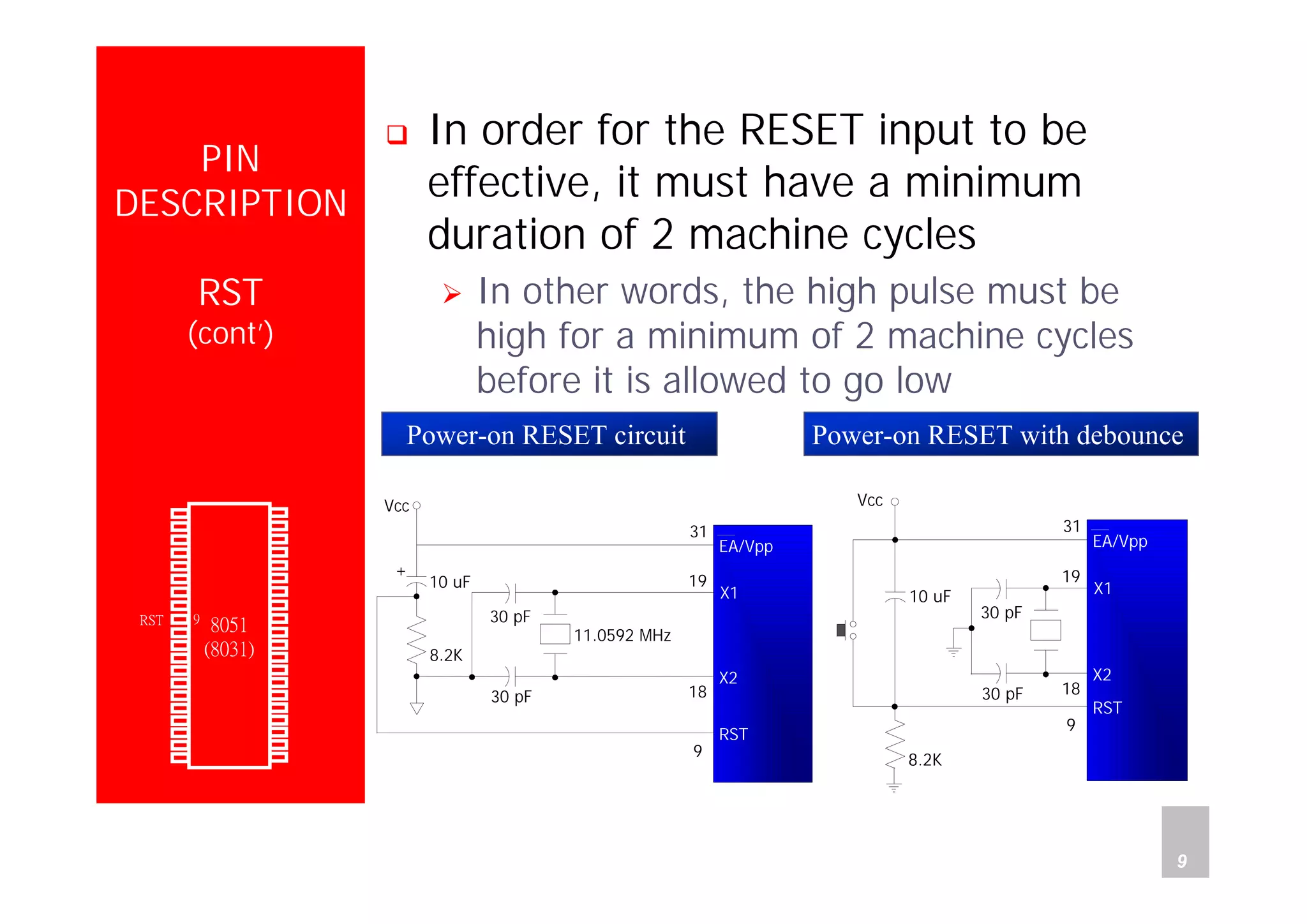

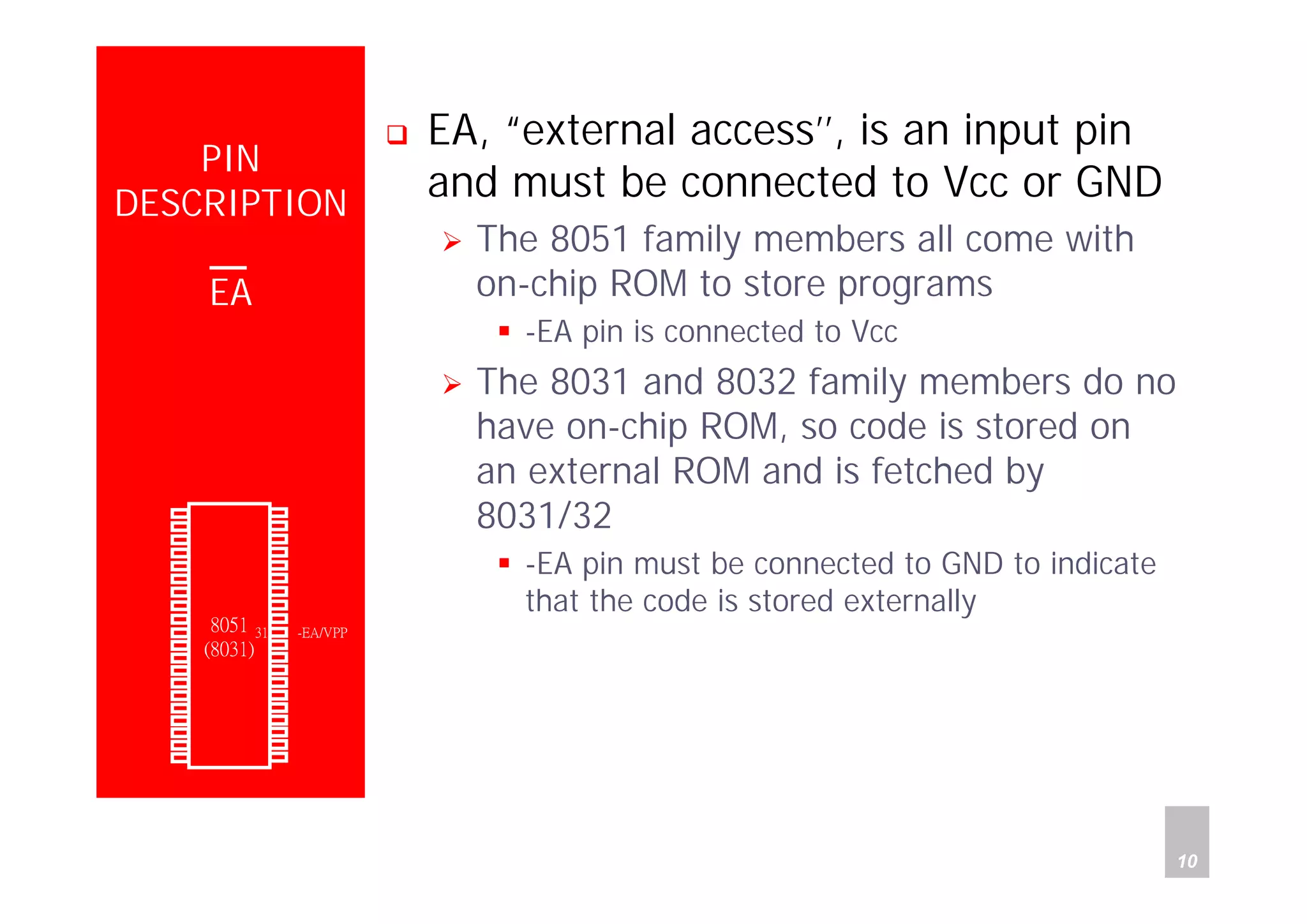

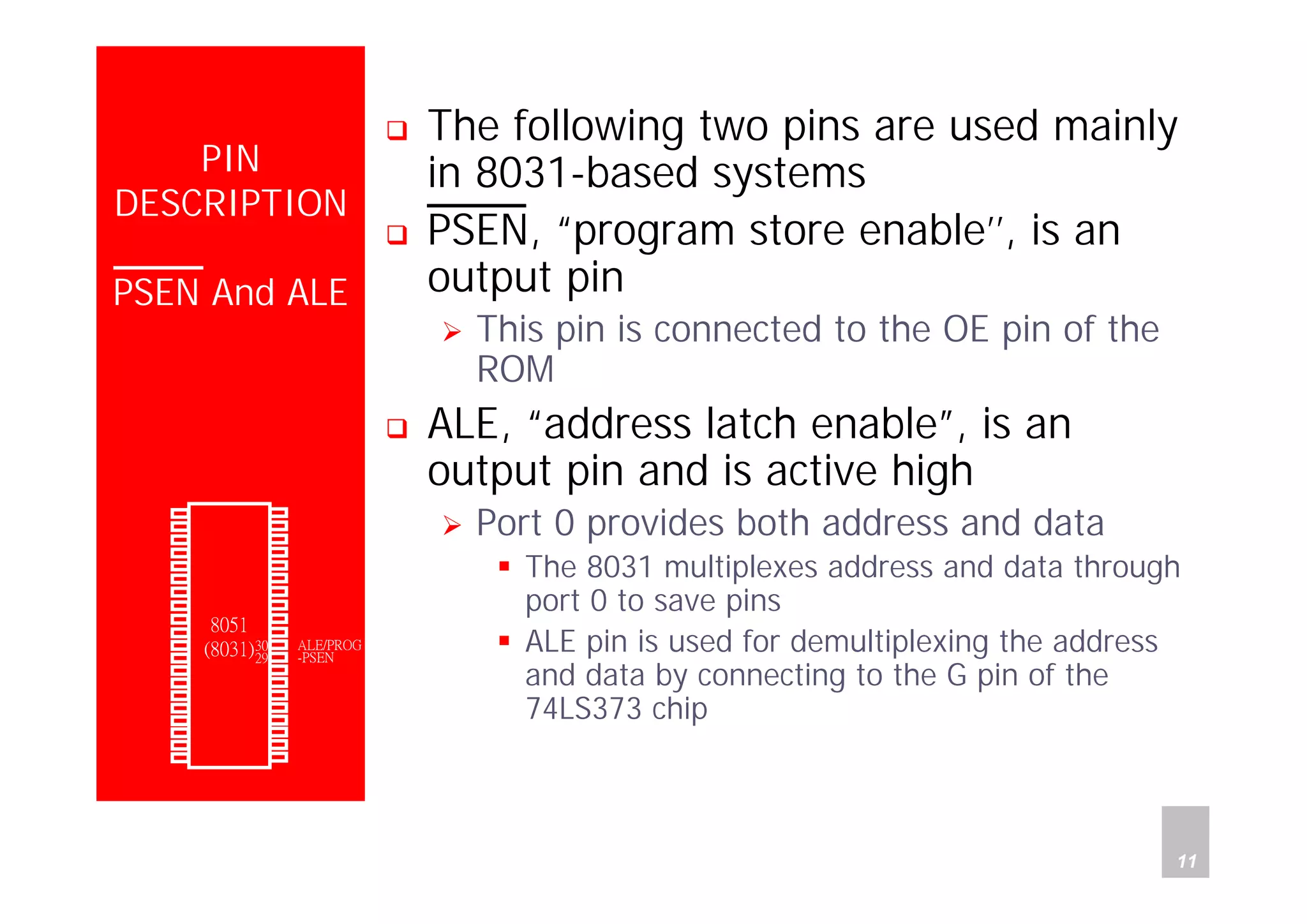

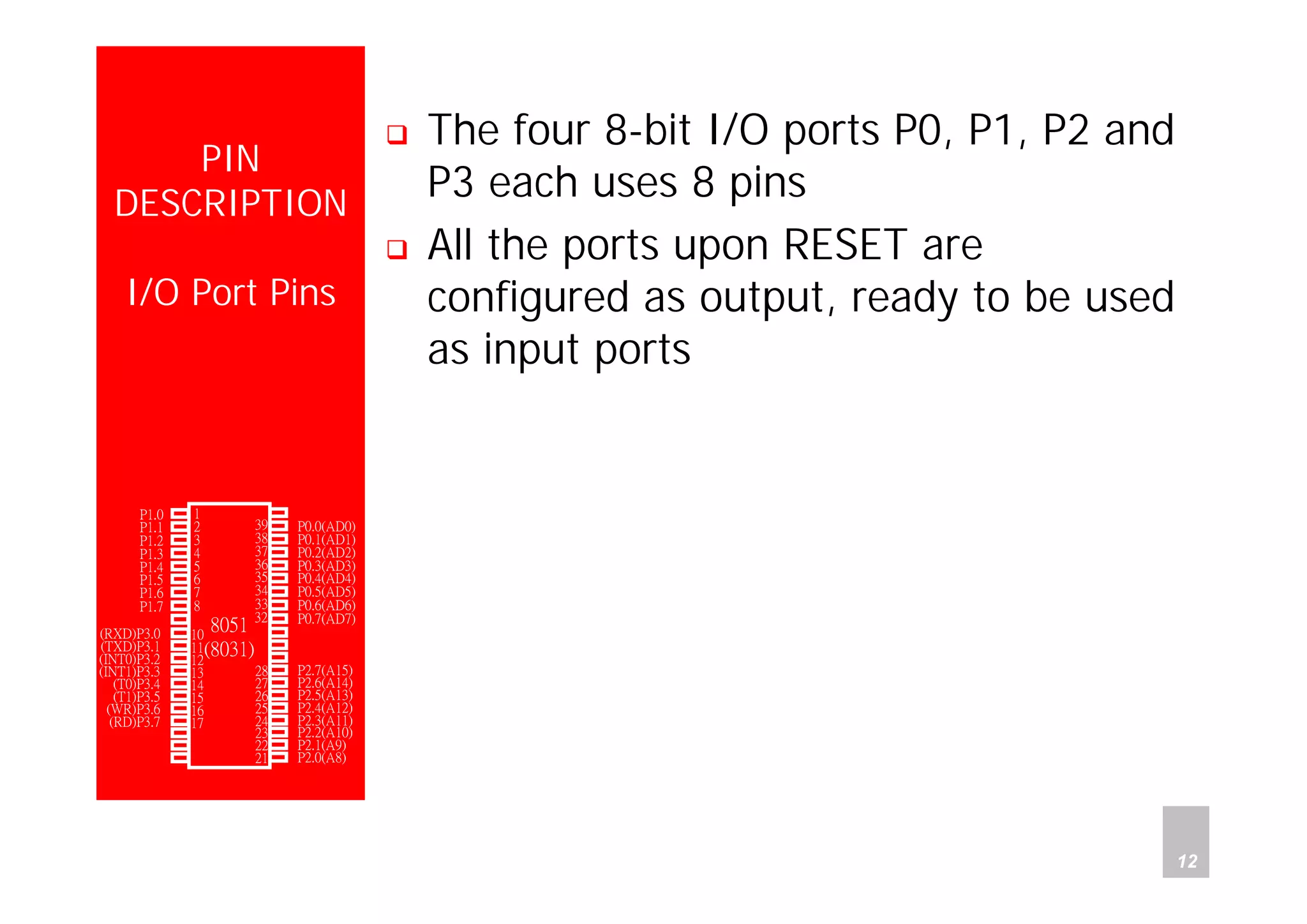

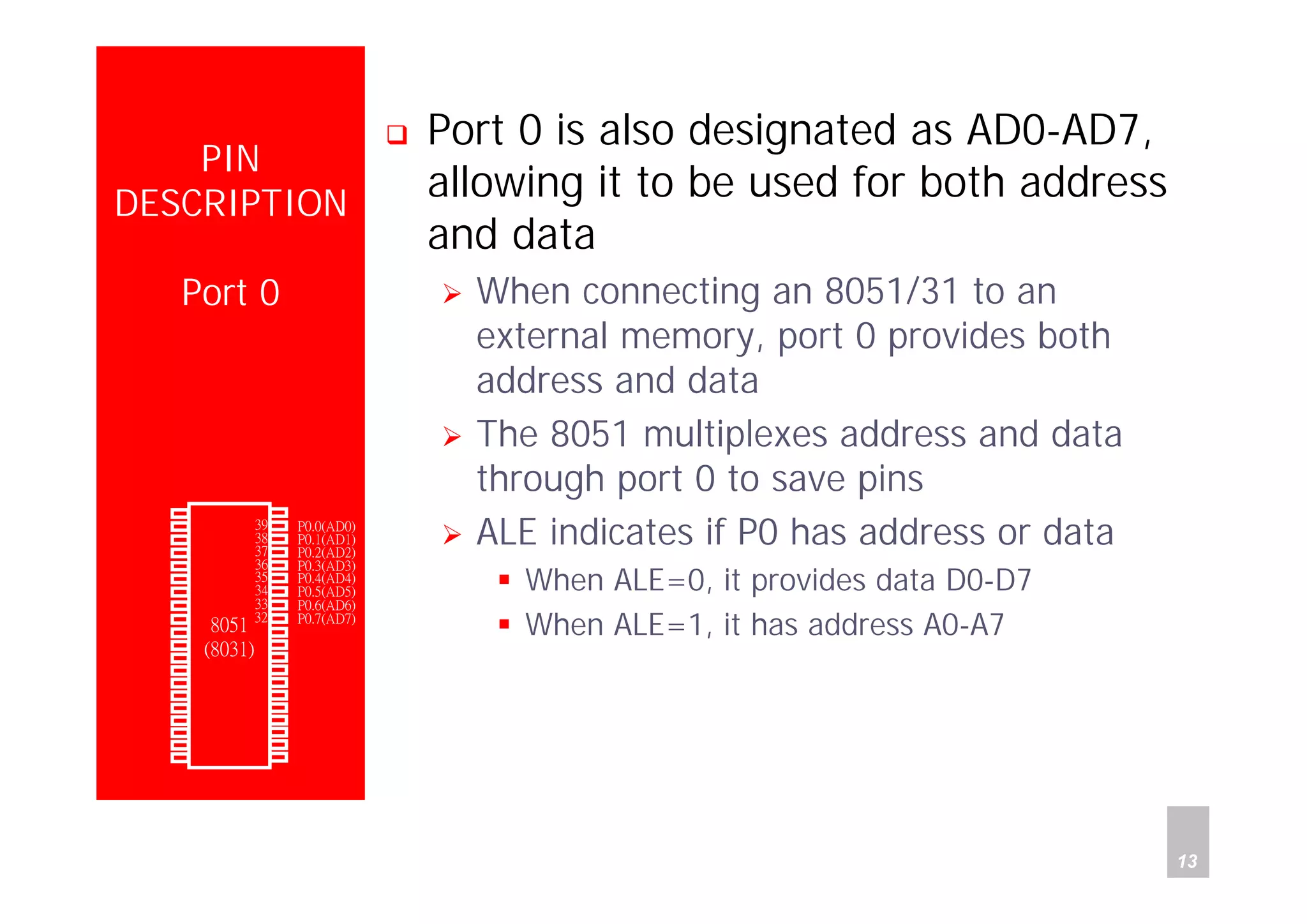

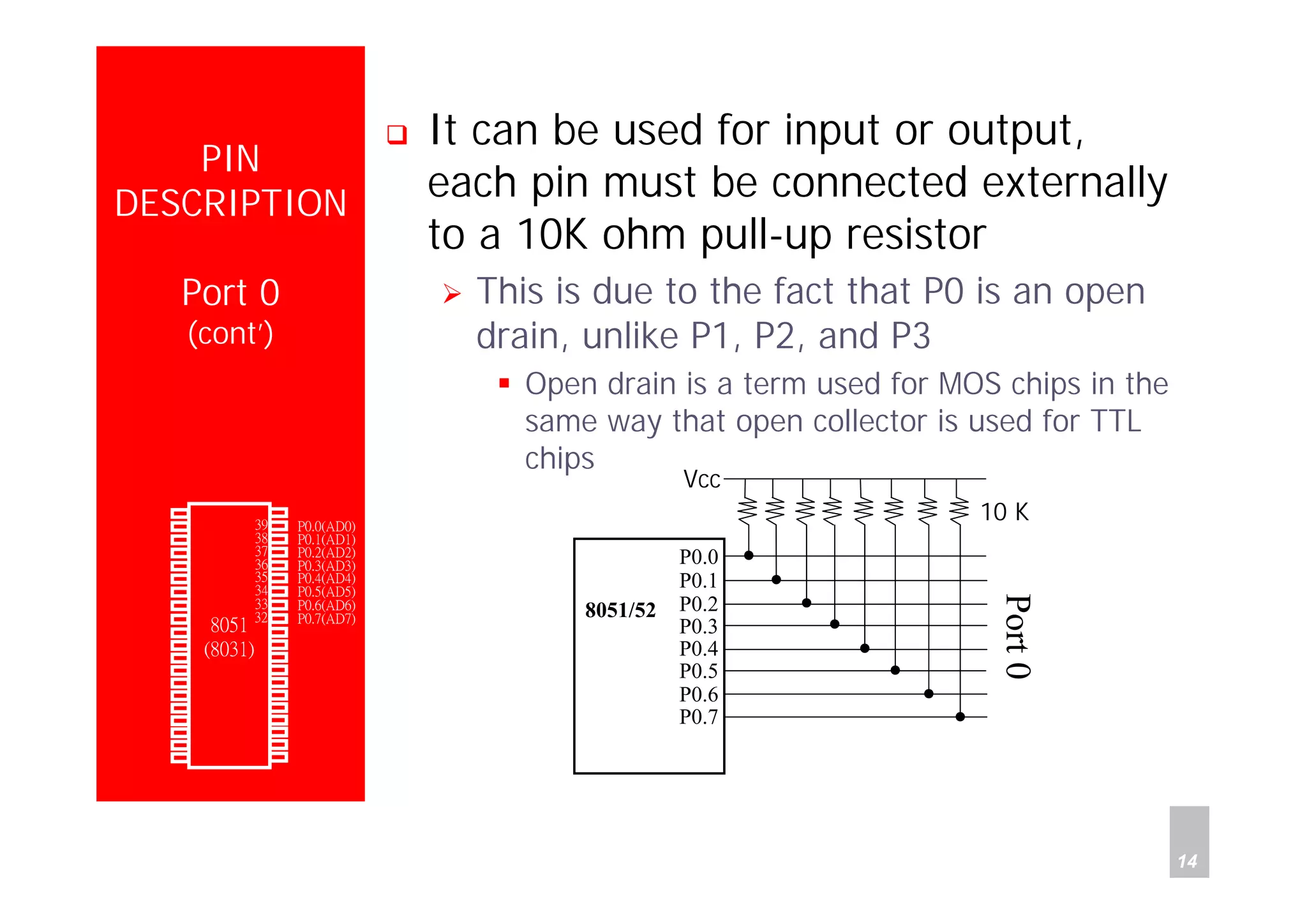

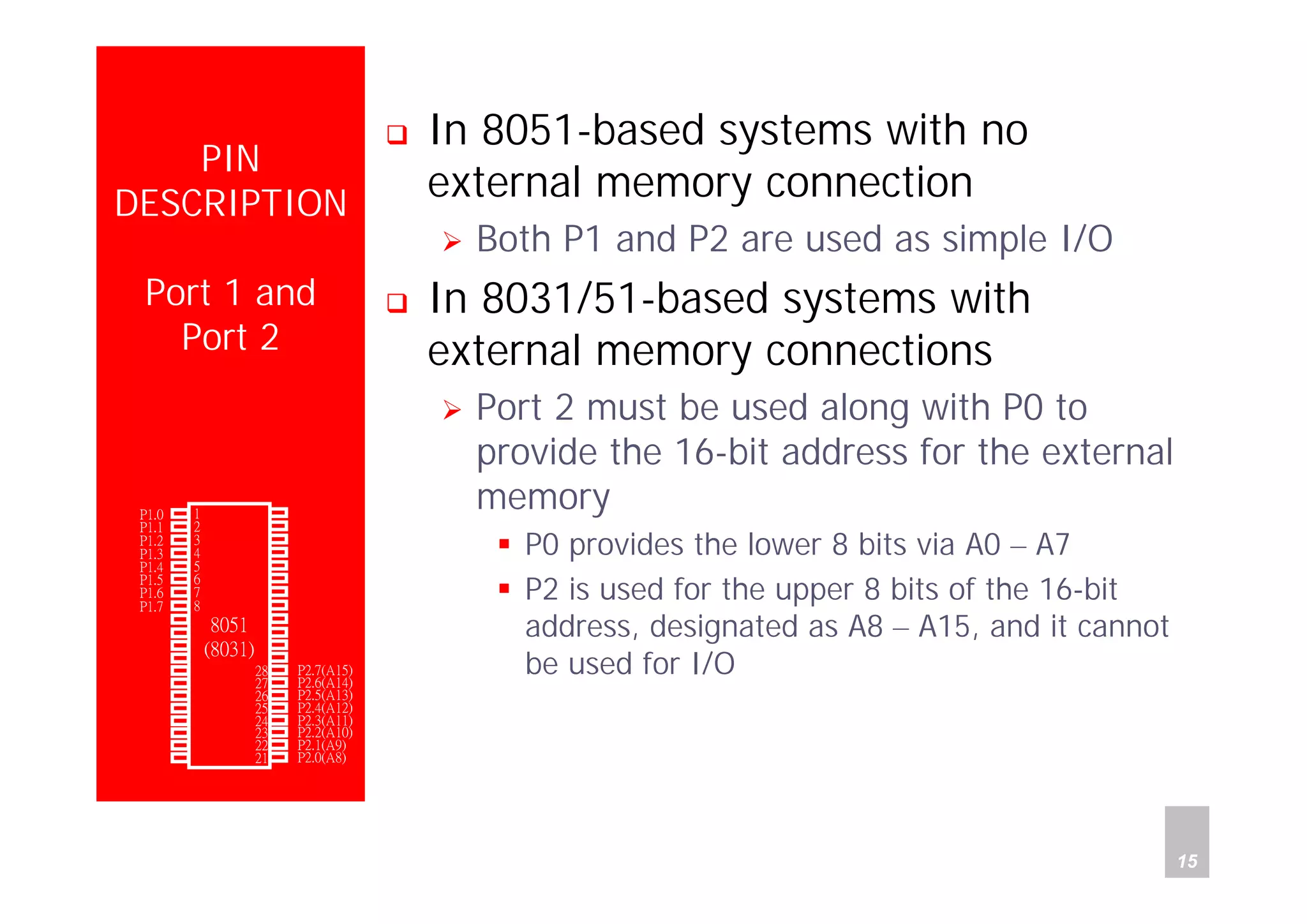

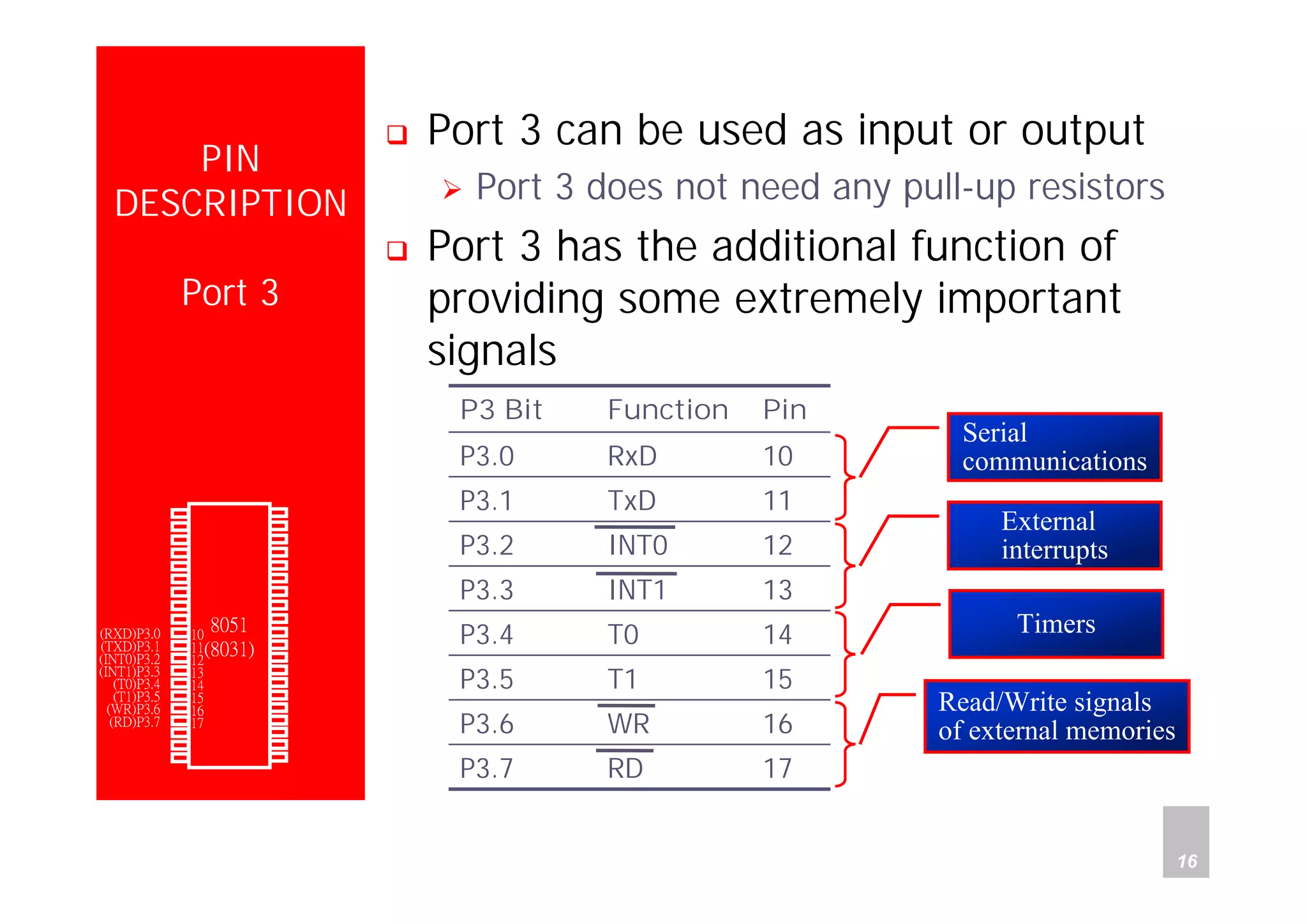

The document describes the pins of the 8051 microcontroller. It discusses the functions of pins such as XTAL1, XTAL2, RST, EA, ports P0-P3, and how they are used to connect the microcontroller to external components like oscillators, memory, and I/O devices. Diagrams are provided to illustrate the pin connections for clock sources, reset circuits, and whether code is stored internally or externally. Key specifications like reset values and required pulse lengths are also mentioned.