Recommended

PDF

本当にわかる Spectre と Meltdown

PDF

PPTX

Openstack zun,virtual kubelet

PDF

PPTX

K8s in 3h - Kubernetes Fundamentals Training

PDF

[Container Plumbing Days 2023] Why was nerdctl made?

PPTX

Neovim으로 생산성 퀀텀점프하기 by 이재열

PPTX

サイバーエージェント様 発表「OpenStackのNWと物理の話」

PDF

【 Unity道場 1月 ~LWRPとシェーダー~】軽量レンダーパイプライン、Light Weight Renderer Pipeline…とは

PDF

PDF

kubernetes-meetup-tokyo-20210624-kubevirt

PDF

Cinemachineで見下ろし視点のカメラを作る

PDF

アーティストの為のプロファイル入門!~楽しいRenderDocの使い方~

PDF

Javaコードが速く実⾏される秘密 - JITコンパイラ⼊⾨(JJUG CCC 2020 Fall講演資料)

PDF

PDF

PDF

Amazon ECS AWS Fargate あるとき~ ないとき~ (トレノケ雲の会 mod2)

PDF

클라우드 컴퓨팅 기반 기술과 오픈스택(Kvm) 기반 Provisioning

PPTX

BuildKitによる高速でセキュアなイメージビルド

PDF

PPTX

PDF

PDF

Introduction to Yocto Project - Let's make customized embedded linux

PDF

Epic Online Services でできること

PDF

PDF

CEDEC 2020 - 高品質かつ低負荷な3Dライブを実現するシェーダー開発 ~『ラブライブ!スクールアイドルフェスティバル ALL STARS』(スク...

PPTX

IncrediBuildでビルド時間を最大90%短縮! - インクレディビルドジャパン株式会社 - GTMF 2018 OSAKA

PDF

【CEDEC2017】Unityを使ったNintendo Switch™向けのタイトル開発・移植テクニック!!

PPTX

PDF

More Related Content

PDF

本当にわかる Spectre と Meltdown

PDF

PPTX

Openstack zun,virtual kubelet

PDF

PPTX

K8s in 3h - Kubernetes Fundamentals Training

PDF

[Container Plumbing Days 2023] Why was nerdctl made?

PPTX

Neovim으로 생산성 퀀텀점프하기 by 이재열

PPTX

サイバーエージェント様 発表「OpenStackのNWと物理の話」

What's hot

PDF

【 Unity道場 1月 ~LWRPとシェーダー~】軽量レンダーパイプライン、Light Weight Renderer Pipeline…とは

PDF

PDF

kubernetes-meetup-tokyo-20210624-kubevirt

PDF

Cinemachineで見下ろし視点のカメラを作る

PDF

アーティストの為のプロファイル入門!~楽しいRenderDocの使い方~

PDF

Javaコードが速く実⾏される秘密 - JITコンパイラ⼊⾨(JJUG CCC 2020 Fall講演資料)

PDF

PDF

PDF

Amazon ECS AWS Fargate あるとき~ ないとき~ (トレノケ雲の会 mod2)

PDF

클라우드 컴퓨팅 기반 기술과 오픈스택(Kvm) 기반 Provisioning

PPTX

BuildKitによる高速でセキュアなイメージビルド

PDF

PPTX

PDF

PDF

Introduction to Yocto Project - Let's make customized embedded linux

PDF

Epic Online Services でできること

PDF

PDF

CEDEC 2020 - 高品質かつ低負荷な3Dライブを実現するシェーダー開発 ~『ラブライブ!スクールアイドルフェスティバル ALL STARS』(スク...

PPTX

IncrediBuildでビルド時間を最大90%短縮! - インクレディビルドジャパン株式会社 - GTMF 2018 OSAKA

PDF

【CEDEC2017】Unityを使ったNintendo Switch™向けのタイトル開発・移植テクニック!!

Viewers also liked

PPTX

PDF

PDF

PDF

PDF

PDF

30日でできない!コンピューター自作入門 - カーネル/VM探検隊@つくば

PDF

PDF

CTF超入門 (for 第12回セキュリティさくら)

PDF

ODP

PDF

PDF

PDF

PDF

PDF

PDF

PPTX

PDF

PDF

バイナリで遊ぼう(オープンソースカンファレンス2014 Tokyo/Fall ライトニングトーク)

PDF

Processing資料(1) Processingの基本

Similar to バイナリより低レイヤな話 (プロセッサの心を読み解く) - カーネル/VM探検隊@北陸1

PDF

リバースエンジニアリングのための新しいトレース手法 - PacSec 2010

PDF

[Basic 7] OS の基本 / 割り込み / システム コール / メモリ管理

PDF

第3回ローレイヤー勉強会 : FPGAでコンピュータを作ってみた

PDF

2011.09.18 v7から始めるunix まとめ

PDF

0章 Linuxカーネルを読む前に最低限知っておくべきこと

PDF

2011.06.11 v7から始めるunix まとめ

PDF

PDF

産学間連携推進室(AC部屋) 2012 成果報告会

PDF

Altera SDK for OpenCL解体新書 : ホストとデバイスの関係

PPT

PDF

PDF

PDF

V6 Interpreter (Nagoya Geek Bar 2011-05-02)

PDF

SpectreとMeltdown:最近のCPUの深い話

PDF

自作コンピューターでなんかする - 第八回 カーネル/VM探検隊&懇親会

PDF

PDF

PPTX

PDF

ODP

More from Hirotaka Kawata

PDF

サーバーサイド Kotlin を社内で普及させてみた - Server-Side Kotlin Night 2025

PDF

Kotest を使って 快適にテストを書こう - KotlinFest 2024

PDF

KotlinConf 2018 から見る 最近の Kotlin サーバーサイド事情

PDF

Micro Python で組み込み Python

PDF

Introduction of PyCon JP 2014 in PyCon SG

PDF

ODP

Open Design Computer Project - Tsukuba.pm

ODP

About University of Tsukuba Linux User Group

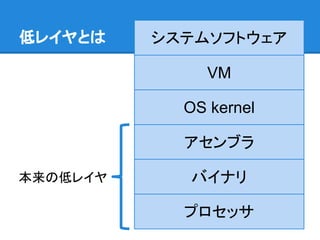

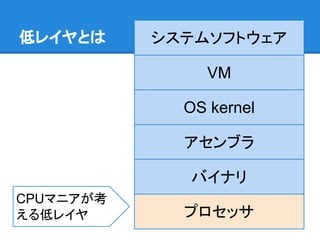

バイナリより低レイヤな話 (プロセッサの心を読み解く) - カーネル/VM探検隊@北陸1 1. 2. @hktechno

川田 裕貴 (かわたひろたか)

● 筑波大学に4月から入院中 (元coins09-AC)

○ システム情報工学研究科

コンピュータサイエンス専攻

○ 実時間組み込みアーキテクチャ研究室

● Open Design Computer Project

○ IPA 未踏 2011 スーパーなんとか

● トプスなんとかっていう会社でバイト中

○ LLVM-IR と最近戯れている

● PyCon JP 2014 プログラムチーム

3. Open Design Computer Project

http://open-arch.org/

● mist32 という自作CPUを作っている

○ 32bit Out of Order RISC コア

○ In-order 版もあるよ

○ FPGA (DE2-115, DE3) 上で動く

● CPU マニアと一緒にやっている

○ @cpu_labs

● 自分はソフトウェアを作っている

○ gcc, binutils, newlib...

○ 最近 xv6 OS が動いた (実機は微妙)

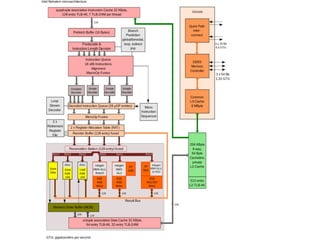

4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. プロセッサの違い

● Intel 第4世代 Core アーキテクチャ

○ Haswell (tock), Broadwell (tick)

● Intel 第3世代 Core アーキテクチャ

○ Sandy Bridge (tock), Ivy Bridge (tick)

違いは何ですか?

● AVX2

● TSX (HTM)

● ???

18. SandyBridge -> Haswell

誰も気にしてくれない進化

● 演算ポートが2つ追加

○ Integer ALU + Branch

○ AGU for stores

● Branch prediction unit の改良

● Reservation station の拡張

● Re-order buffer の拡張

● Physical register file の拡張

そもそもなんだかわからない

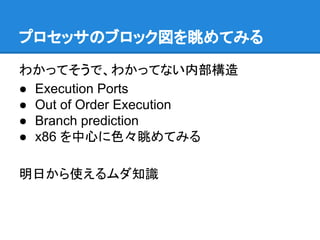

19. 20. 21. ● Instruction Fetch

● Instruction Buffer

● Instruction Decode

● Dispatch

● Execution

MIST32 (In-order: MIST1032ISA)

IB

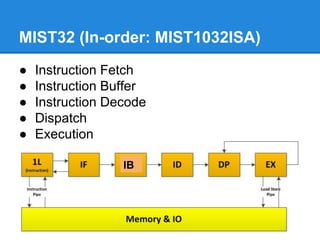

22. 23. 24. Out of Order Execution

mov eax, [eax]

xor ebx, ebx

add ebx, eax

inc ecx

add eax, ecx

Load (遅い)

↑の命令とは依存がない

↑の命令とは依存がない

25. Out of Order Execution

mov eax, [eax]

xor ebx, ebx

add ebx, eax

inc ecx

add eax, ecx

Load (遅い)

↑の命令とは依存がない

↑の命令とは依存がない

1

2

3

2

3

命令の順番を入れ替えても構わない

しかも、開いてるポートに並列に実行できる

26. Out of Order Execution

非順序実行

● 実行できる命令から実行する

プロセッサがやらなければならないこと

1. 命令の依存関係を知る

2. 命令をバッファする

3. 実行できる命令から実行する

4. どの命令が終わったかを知る

5. 本来の順序でレジスタへコミットする

27. Out of Order Execution

● Out of Order

○ Intel P6 から実装 (Pentium Pro)

○ Intel Atom (Silvermont から実装)

○ ARM Cortex-A9 から実装

○ mist32

■ ただし Load/Store OoO は未実装

● In Order

○ Intel Atom (初代 Bonnell)

○ ARM Cortex-A7 以前

速くはなるが

回路規模は大きくなる

28. 29. Out of Order Execution

● Register Renaming

○ 物理レジスタを仮想レジスタにリネームする

○ 命令の依存をより少なくできる

○ (アウトオブオーダー実行に必須ではないが...)

mov eax, [eax]

inc eax

mov [eax], eax

mov eax, ebx

mov eax, [eax]

同じ eax レジスタ

だが、依存はない

← 先に実行可能

30. Out of Order Execution

代表的な OoO の実装

● Reorder Buffer

○ 命令のコミットを制御するバッファ

○ 演算の結果は一度ここへ書かれる

● Reservation Station

○ 命令の依存関係を待つところ

○ ソースレジスタが利用可能かを監視して、

実行可能であれば実行を開始する

○ Unified な方式、実行ポートごとに持たせる方式

31. 32. 33. 34. 35. 36. 37. 38. 最近? の uOPs

● Micro-OPs Fusion

○ Fused Micro-OP

○ 一部 uOP をまとめてパイプラインに流す

■ uOP 帯域の削減

● Macro-OPs Fusion

○ 複数の x86 命令をまとめる

○ 例えば CMP + Jxx

○ Macro-OP レベルの並列性を向上

■ 少ないデコーダで実現

39. Branch prediction

分岐予測

● ブランチは厄介

○ taken / not taken は直前になるまでわからない

○ ミスするとパイプラインをフラッシュしてやり直し

■ すごい大きなペナルティになる

○ ブランチするかしないか、予測する必要がある

分岐予測以外のアイデア

● Condition-Code (ARM)

○ AArch64 では消え去りました

40. 41. Branch prediction

● 分岐予測がアツイ (らしい)

○ 電力があまり食わない上に性能向上に直結する

○ Intel の 3% ルール

○ 最近もいろいろな変更がある (ただし企業秘密?)

● 基本的な分岐予測

○ 分岐しない (or する) 方向で常に予測しておく

■ 486

○ 前回分岐した結果を保存しておく

○ ループを検出する

○ ...

42. 43. Branch prediction

● Loop detector

○ n 回目で必ず分岐するなら、n を記憶しておく

○ 過去 n 回の分岐パターンを記憶する

● Global branch predictor

○ ある特定の分岐をそれぞれ記憶するのではなく、

すべての分岐のパターンを記憶しておく

○ 周りの分岐命令との相関関係

最近のプロセッサは、ハイブリッド分岐予測器

● Bimodal + Loop detector + Global

● どれか有効なものを使用する

44. 45. 47. 48. 49. 最近の Intel のプロセッサ

● Zeroing Idioms

○ xor eax, eax のような命令をゼロレジスタに、

リネームする

● uOP Cache

○ uOp の変換をキャッシュする

○ フロントエンドが眠ることができる

○ Intel のデコーダはでかい

■ でかいデコーダを眠らせると電力効率アップ

● 実行ポートの増加

○ ブランチユニット、AGU が増えた

50. 最近の Intel プロセッサ

他にも...

● Physical Register File

○ 物理レジスタファイルへ直接書き込む

○ 待ち受け命令への ROB からのコピーを削減

● 分岐予測機のさらなる改良

○ 詳細不明、エントリが増えてるなど

● ROB, RS のエントリの追加

● Macro-Fusion の命令の追加

51. 最近の Intel のプロセッサ

● デコードの隠蔽に力を入れているっぽい

○ x86 のクソ命令セットが重い

○ デコーダに負担がかかる

■ デコーダ回路もでかい + 電力食い

○ いかにデコーダを回さないか

■ uOP Cache

■ uOP レベルでの分岐予測

● なぜ、あんなに性能が出るのか

○ 命令セットはクズなのに

○ Intel すごすぎ

52. 54. 55. 56.

![Out of Order Execution

mov eax, [eax]

xor ebx, ebx

add ebx, eax

inc ecx

add eax, ecx

Load (遅い)

↑の命令とは依存がない

↑の命令とは依存がない](https://image.slidesharecdn.com/kernelvm-140712043800-phpapp01/85/VM-1-24-320.jpg)

![Out of Order Execution

mov eax, [eax]

xor ebx, ebx

add ebx, eax

inc ecx

add eax, ecx

Load (遅い)

↑の命令とは依存がない

↑の命令とは依存がない

1

2

3

2

3

命令の順番を入れ替えても構わない

しかも、開いてるポートに並列に実行できる](https://image.slidesharecdn.com/kernelvm-140712043800-phpapp01/85/VM-1-25-320.jpg)

![Out of Order Execution

● Register Renaming

○ 物理レジスタを仮想レジスタにリネームする

○ 命令の依存をより少なくできる

○ (アウトオブオーダー実行に必須ではないが...)

mov eax, [eax]

inc eax

mov [eax], eax

mov eax, ebx

mov eax, [eax]

同じ eax レジスタ

だが、依存はない

← 先に実行可能](https://image.slidesharecdn.com/kernelvm-140712043800-phpapp01/85/VM-1-29-320.jpg)

![Branch prediction

mov eax, [eax]

cmp eax, 0

je is_zero

...

...

is_zero:

...

実行完了するまで

分岐するかわからない](https://image.slidesharecdn.com/kernelvm-140712043800-phpapp01/85/VM-1-40-320.jpg)