Autonomus syllabus12 mtechcse_mtech sem1_mtech model papers_co model paper

•Download as DOCX, PDF•

0 likes•132 views

Report

Share

Report

Share

Recommended

Recommended

More Related Content

What's hot

What's hot (20)

Power and Delay Analysis of Logic Circuits Using Reversible Gates

Power and Delay Analysis of Logic Circuits Using Reversible Gates

FPGA Implementation of Mix and Inverse Mix Column for AES Algorithm

FPGA Implementation of Mix and Inverse Mix Column for AES Algorithm

ICML2013読み会 Large-Scale Learning with Less RAM via Randomization

ICML2013読み会 Large-Scale Learning with Less RAM via Randomization

III EEE-CS2363-Computer-Networks-important-questions-for-unit-3-for-may-june-...

III EEE-CS2363-Computer-Networks-important-questions-for-unit-3-for-may-june-...

Solid state device modeling and simulation jan2013 (1)

Solid state device modeling and simulation jan2013 (1)

COUPLED FPGA/ASIC IMPLEMENTATION OF ELLIPTIC CURVE CRYPTO-PROCESSOR

COUPLED FPGA/ASIC IMPLEMENTATION OF ELLIPTIC CURVE CRYPTO-PROCESSOR

Cycle’s topological optimizations and the iterative decoding problem on gener...

Cycle’s topological optimizations and the iterative decoding problem on gener...

Parallel iterative solution of the hermite collocation equations on gpus

Parallel iterative solution of the hermite collocation equations on gpus

Viewers also liked

Viewers also liked (6)

Similar to Autonomus syllabus12 mtechcse_mtech sem1_mtech model papers_co model paper

5th Semester (June-2016) Computer Science and Information Science Engineering...

5th Semester (June-2016) Computer Science and Information Science Engineering...BGS Institute of Technology, Adichunchanagiri University (ACU)

8th Semester Electronic and Communication Engineering (2013-June) Question Pa...

8th Semester Electronic and Communication Engineering (2013-June) Question Pa...BGS Institute of Technology, Adichunchanagiri University (ACU)

7th Semester (June; July-2015) Computer Science and Information Science Engin...

7th Semester (June; July-2015) Computer Science and Information Science Engin...BGS Institute of Technology, Adichunchanagiri University (ACU)

1st Semester M Tech CMOS VLSI Design (Dec-2013) Question Papers

1st Semester M Tech CMOS VLSI Design (Dec-2013) Question PapersBGS Institute of Technology, Adichunchanagiri University (ACU)

6th EC CBCS Model question papers

6th EC CBCS Model question papersCoorg Institute of Technology, Department Of Library & Information Center , Ponnampet

8th Semester Electronic and Communication Engineering (June/July-2015) Questi...

8th Semester Electronic and Communication Engineering (June/July-2015) Questi...BGS Institute of Technology, Adichunchanagiri University (ACU)

5th Semester CS / IS (2013-June) Question Papers

5th Semester CS / IS (2013-June) Question PapersBGS Institute of Technology, Adichunchanagiri University (ACU)

5th Semester (Dec-2015; Jan-2016) Computer Science and Information Science En...

5th Semester (Dec-2015; Jan-2016) Computer Science and Information Science En...BGS Institute of Technology, Adichunchanagiri University (ACU)

5th Semester (June; July-2015) Computer Science and Information Science Engin...

5th Semester (June; July-2015) Computer Science and Information Science Engin...BGS Institute of Technology, Adichunchanagiri University (ACU)

Similar to Autonomus syllabus12 mtechcse_mtech sem1_mtech model papers_co model paper (20)

Digital Control Systems Jntu Model Paper{Www.Studentyogi.Com}

Digital Control Systems Jntu Model Paper{Www.Studentyogi.Com}

D I G I T A L C O N T R O L S Y S T E M S J N T U M O D E L P A P E R{Www

D I G I T A L C O N T R O L S Y S T E M S J N T U M O D E L P A P E R{Www

5th Semester (June-2016) Computer Science and Information Science Engineering...

5th Semester (June-2016) Computer Science and Information Science Engineering...

8th Semester Electronic and Communication Engineering (2013-June) Question Pa...

8th Semester Electronic and Communication Engineering (2013-June) Question Pa...

7th Semester (June; July-2015) Computer Science and Information Science Engin...

7th Semester (June; July-2015) Computer Science and Information Science Engin...

Mf5102 computer-integrated-manufacturing-systems 1

Mf5102 computer-integrated-manufacturing-systems 1

1st Semester M Tech CMOS VLSI Design (Dec-2013) Question Papers

1st Semester M Tech CMOS VLSI Design (Dec-2013) Question Papers

8th Semester Electronic and Communication Engineering (June/July-2015) Questi...

8th Semester Electronic and Communication Engineering (June/July-2015) Questi...

5th Semester (Dec-2015; Jan-2016) Computer Science and Information Science En...

5th Semester (Dec-2015; Jan-2016) Computer Science and Information Science En...

5th Semester (June; July-2015) Computer Science and Information Science Engin...

5th Semester (June; July-2015) Computer Science and Information Science Engin...

Autonomus syllabus12 mtechcse_mtech sem1_mtech model papers_co model paper

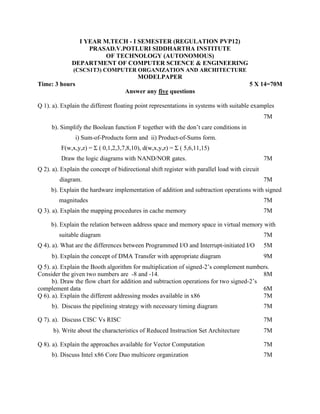

- 1. I YEAR M.TECH - I SEMESTER (REGULATION PVP12) PRASAD.V.POTLURI SIDDHARTHA INSTITUTE OF TECHNOLOGY (AUTONOMOUS) DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING (CSCS1T3) COMPUTER ORGANIZATION AND ARCHITECTURE MODELPAPER Time: 3 hours 5 X 14=70M Answer any five questions Q 1). a). Explain the different floating point representations in systems with suitable examples 7M b). Simplify the Boolean function F together with the don’t care conditions in i) Sum-of-Products form and ii) Product-of-Sums form. F(w,x,y,z) = Σ ( 0,1,2,3,7,8,10), d(w,x,y,z) = Σ ( 5,6,11,15) Draw the logic diagrams with NAND/NOR gates. 7M Q 2). a). Explain the concept of bidirectional shift register with parallel load with circuit diagram. 7M b). Explain the hardware implementation of addition and subtraction operations with signed magnitudes 7M Q 3). a). Explain the mapping procedures in cache memory 7M b). Explain the relation between address space and memory space in virtual memory with suitable diagram 7M Q 4). a). What are the differences between Programmed I/O and Interrupt-initiated I/O 5M b). Explain the concept of DMA Transfer with appropriate diagram 9M Q 5). a). Explain the Booth algorithm for multiplication of signed-2’s complement numbers. Consider the given two numbers are -8 and -14. 8M b). Draw the flow chart for addition and subtraction operations for two signed-2’s complement data 6M Q 6). a). Explain the different addressing modes available in x86 7M b). Discuss the pipelining strategy with necessary timing diagram 7M Q 7). a). Discuss CISC Vs RISC 7M b). Write about the characteristics of Reduced Instruction Set Architecture 7M Q 8). a). Explain the approaches available for Vector Computation 7M b). Discuss Intel x86 Core Duo multicore organization 7M