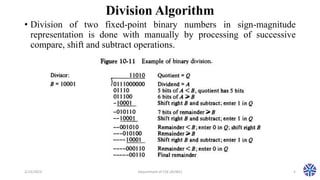

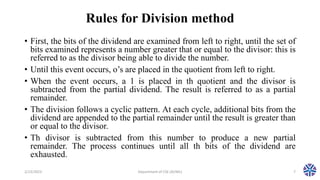

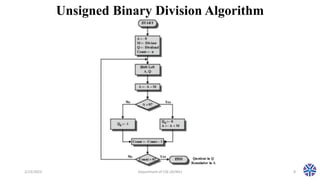

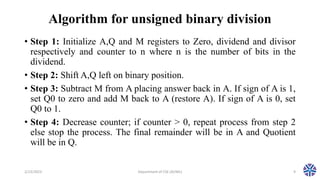

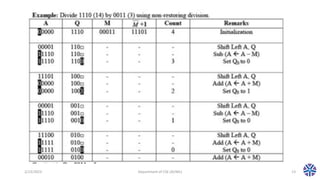

This document summarizes the topics covered in Session 21 of the CS304PC course on Computer Organization and Architecture. It discusses division algorithms for fixed-point binary numbers using successive compare, shift, and subtract operations. The unsigned and signed binary division algorithms are presented step-by-step. Division overflow is also explained, which can occur when the quotient exceeds the standard register length. The next session will cover floating-point arithmetic operations.