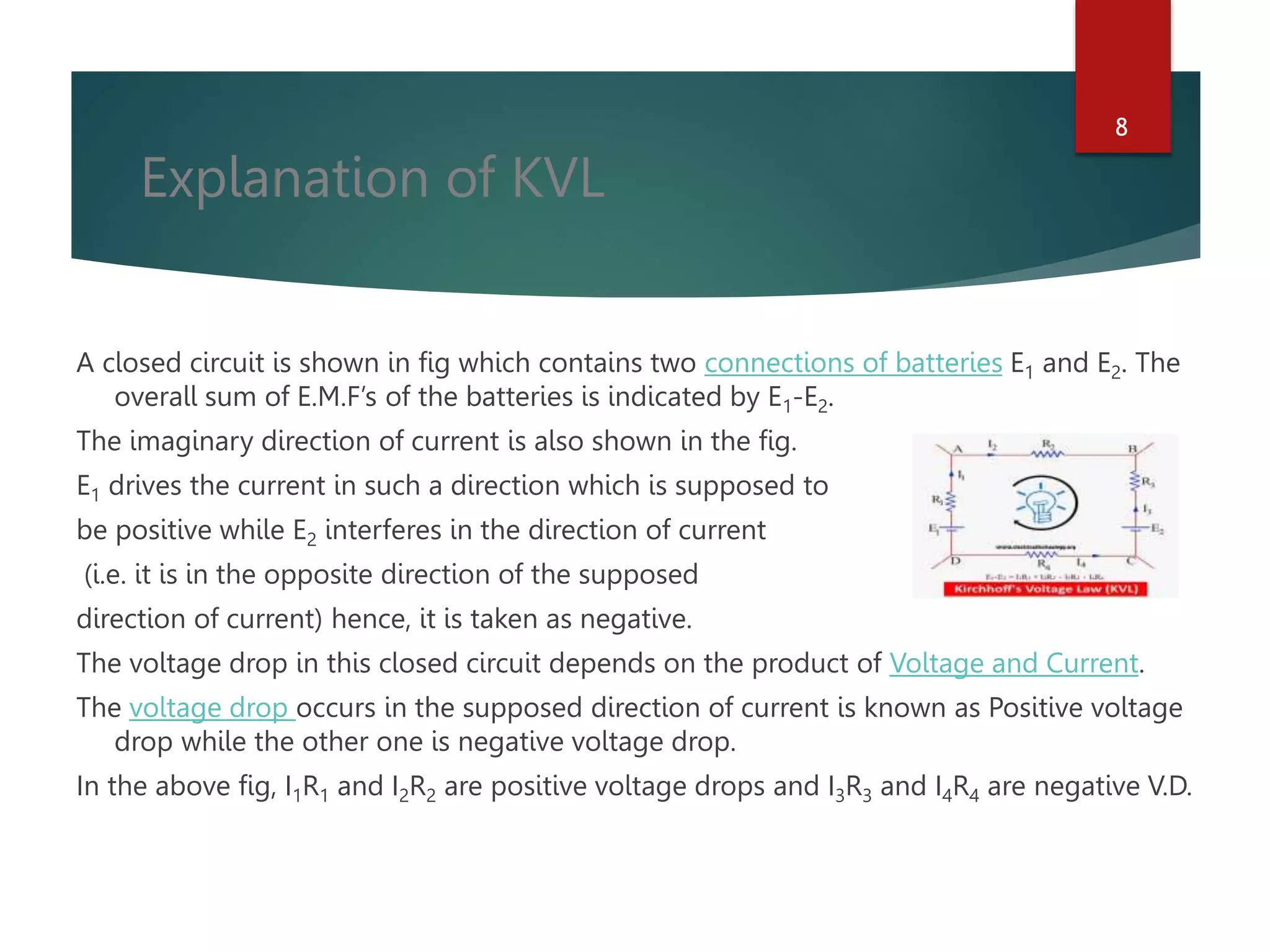

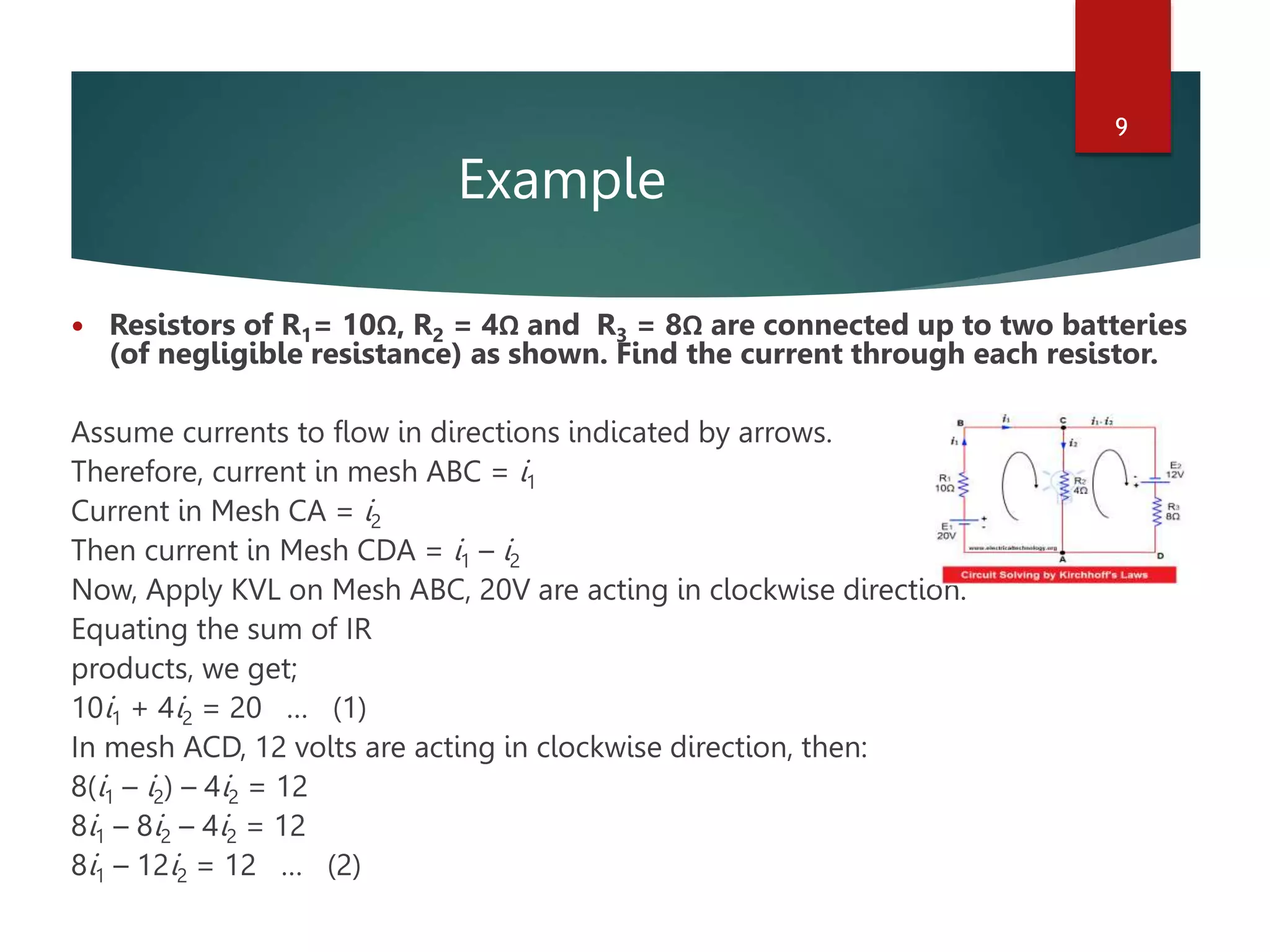

This document provides an overview of Kirchhoff’s Current Law (KCL) and Kirchhoff’s Voltage Law (KVL), which are fundamental principles in electrical circuit analysis. KCL states that the sum of currents entering a node equals the sum of currents leaving it, while KVL dictates that the sum of voltages around a loop is zero. The document also includes formulations of both laws, examples of calculations using these laws, and their applications in determining unknown circuit values.