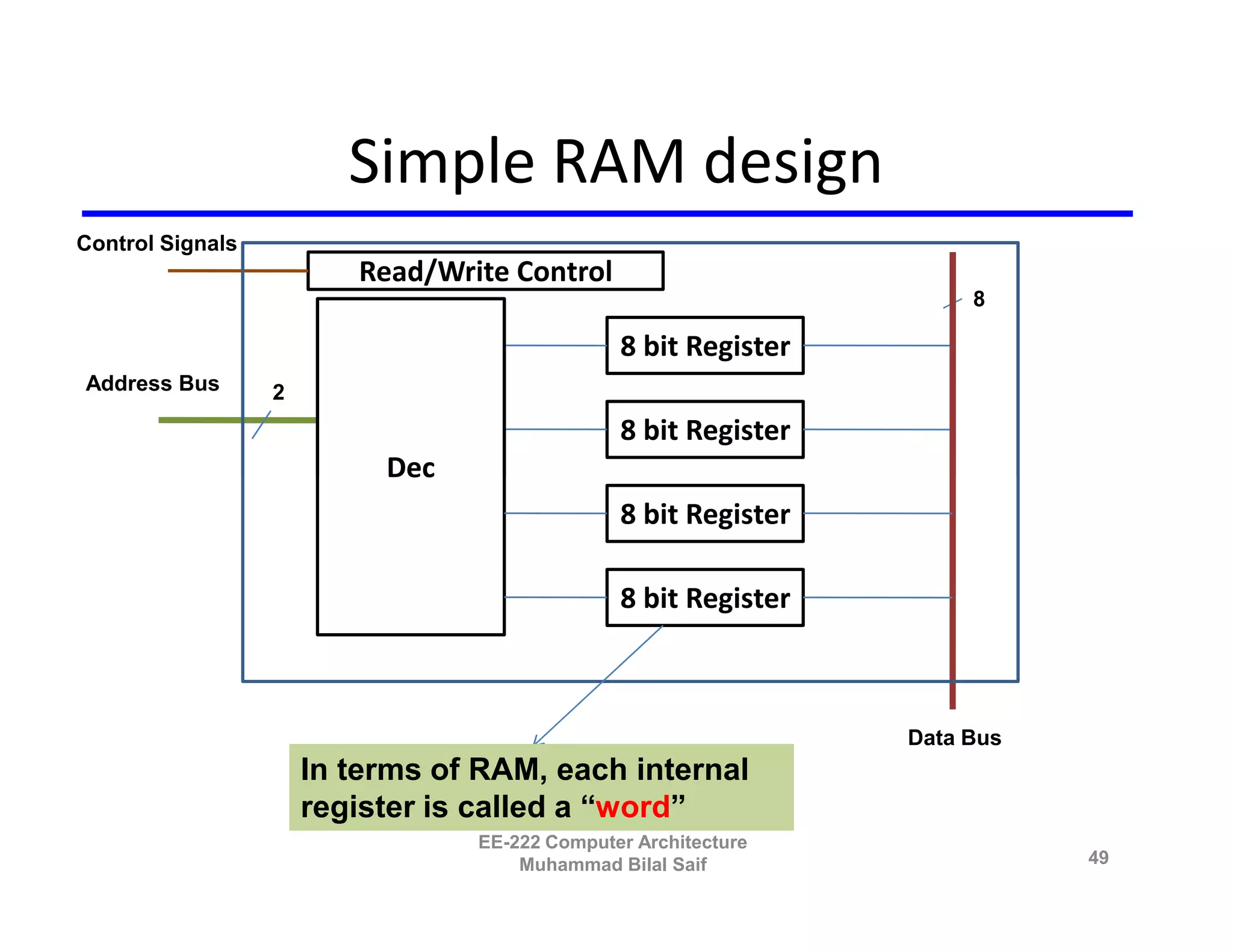

Here are the key points about RAM calculation:

- RAM size is specified in number of words

- Each word has a fixed number of bits (typically 8, 16, 32, 64 bits)

- To calculate total RAM size in bits:

- Number of words x Bits per word

- For example, a 2K RAM with 8-bit words would have:

- 2,000 words

- 8 bits per word

- So total size is 2,000 x 8 = 16,000 bits = 2KB

- The number of address lines needed is equal to the base 2 logarithm of the number of words

- For a 2K RAM, log2(2,000) = 11 address

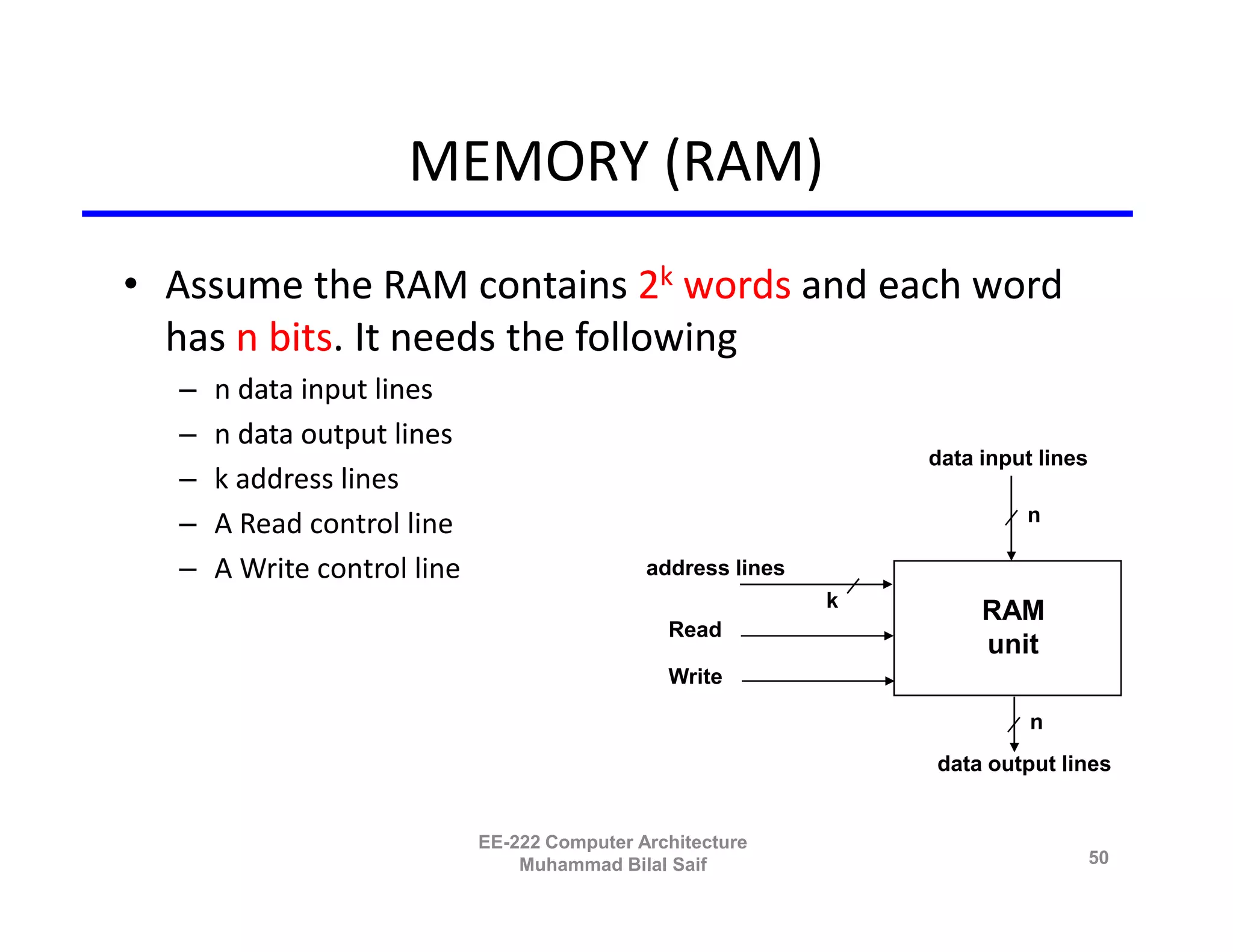

![MEMORY READ

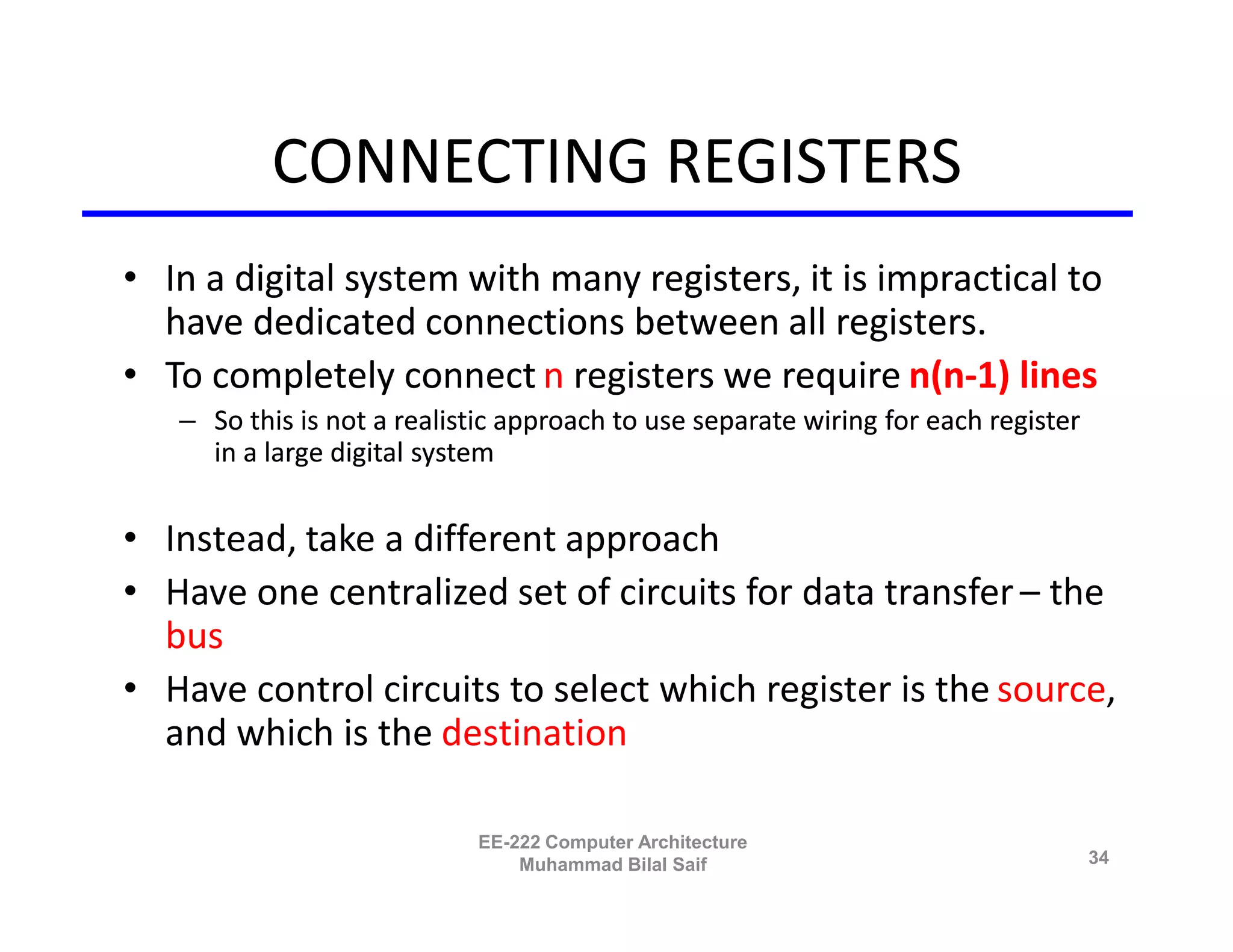

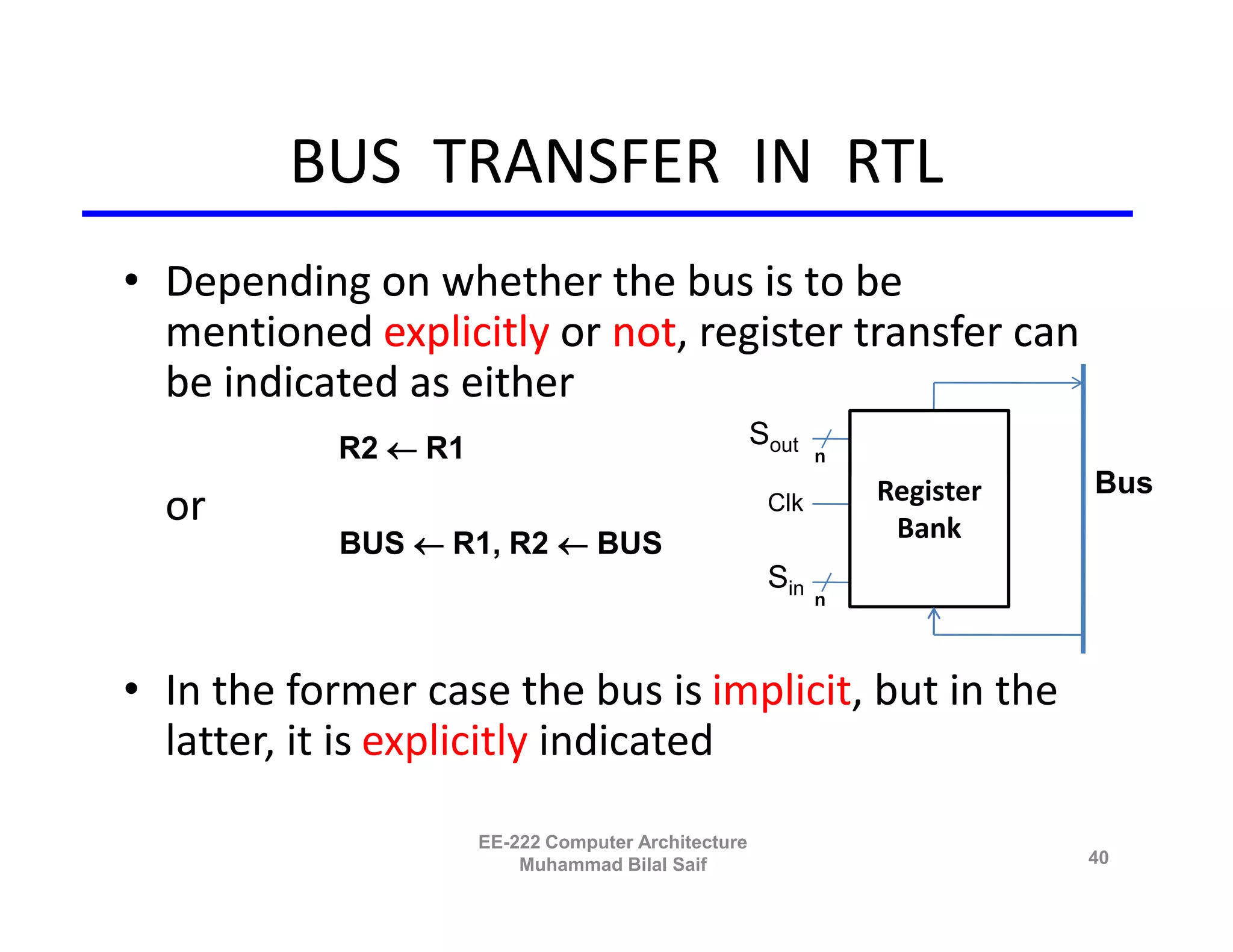

• To read a value from a location in memory and load it into a register,

the register transfer language notation looks like this:

R1 M[MAR]

• This causes the following actions to occur

– The contents of the MAR get sent to the memory address lines

– A Read (= 1) gets sent to the memory unit

– The contents of the specified address are put on the memory’s output data lines

– These get sent over the bus to be loaded into register R1

EE-222 Computer Architecture

Muhammad Bilal Saif 53](https://image.slidesharecdn.com/lecture2-100803195947-phpapp02/75/Lecture-2-20-2048.jpg)

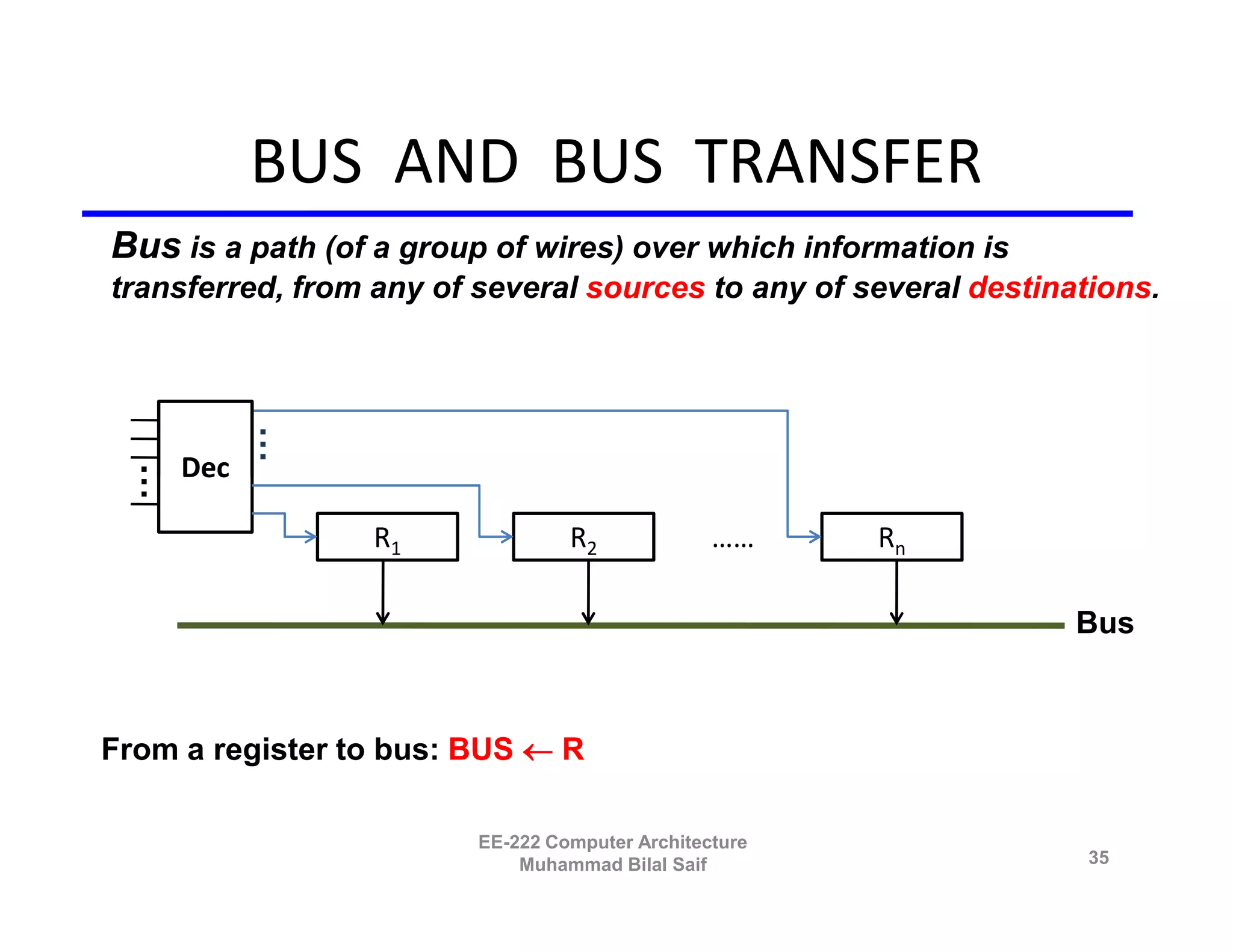

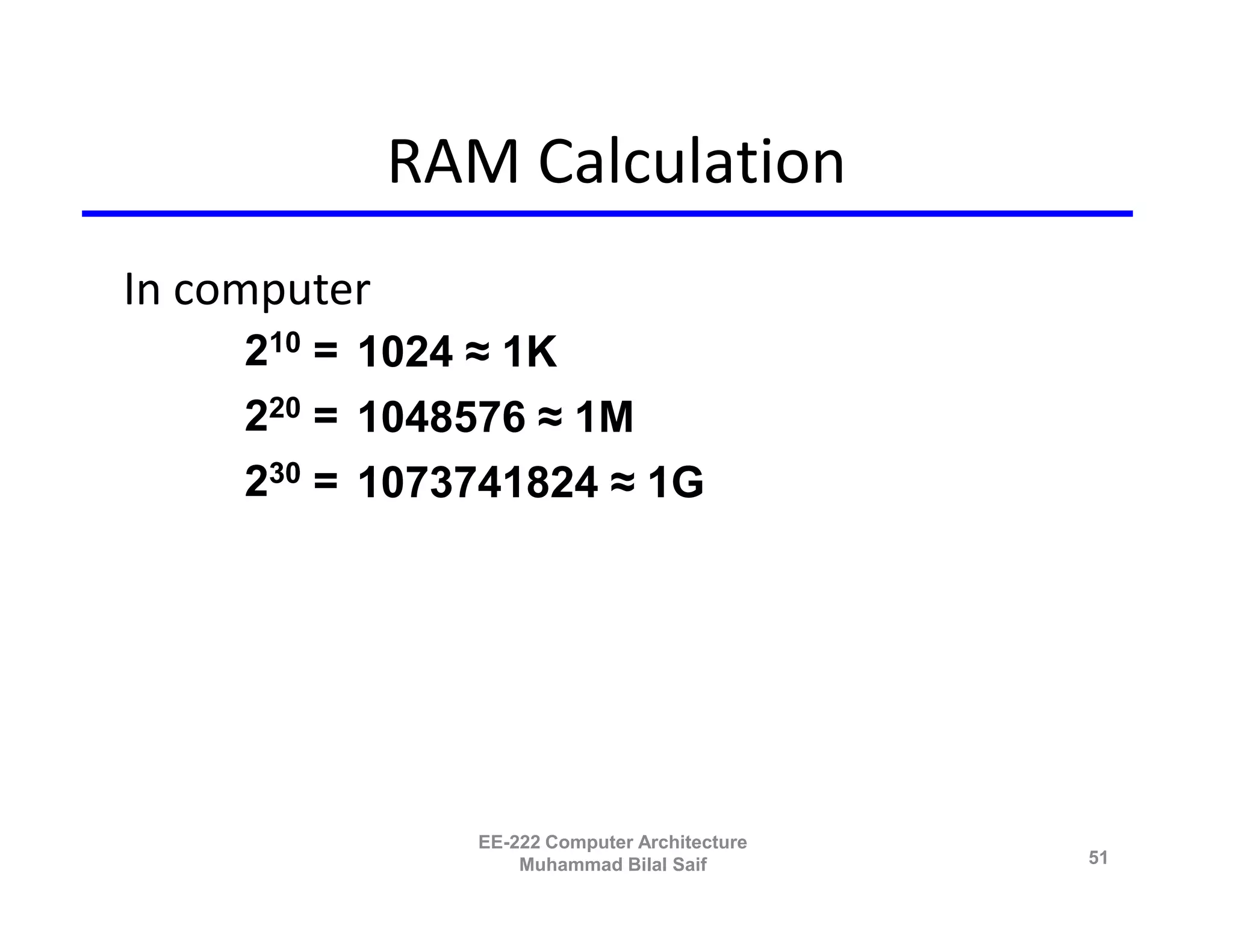

![MEMORY WRITE

• To write a value from a register to a location in memory looks like

this in register transfer language:

M[MAR] R1

• This causes the following to occur

– The contents of the MAR get sent to the memory address lines

– The values in register R1 get sent over the bus to the data input lines of the

memory

– A Write (= 1) gets sent to the memory unit

– The values get loaded into the specified address in the memory

EE-222 Computer Architecture

Muhammad Bilal Saif 54](https://image.slidesharecdn.com/lecture2-100803195947-phpapp02/75/Lecture-2-21-2048.jpg)

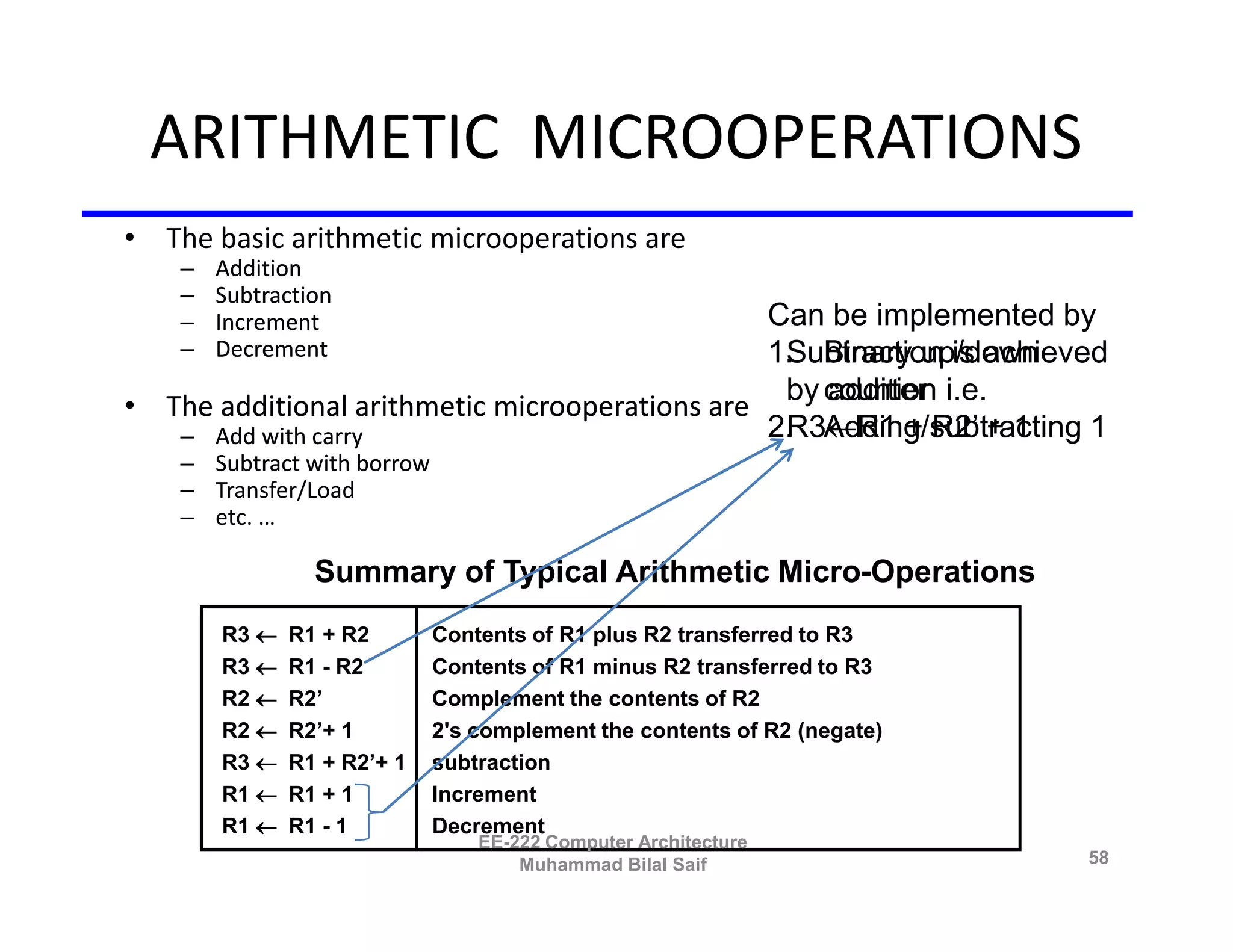

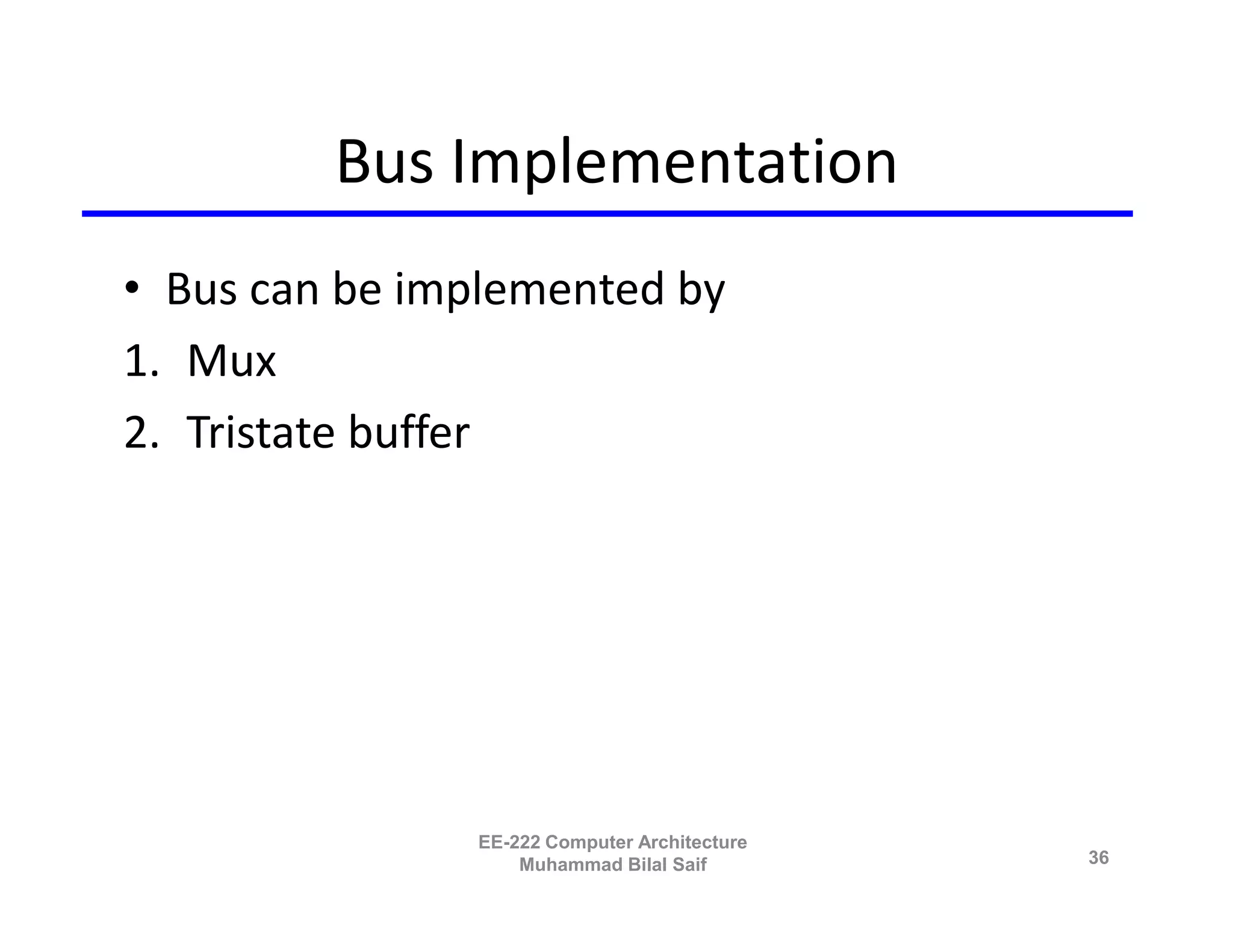

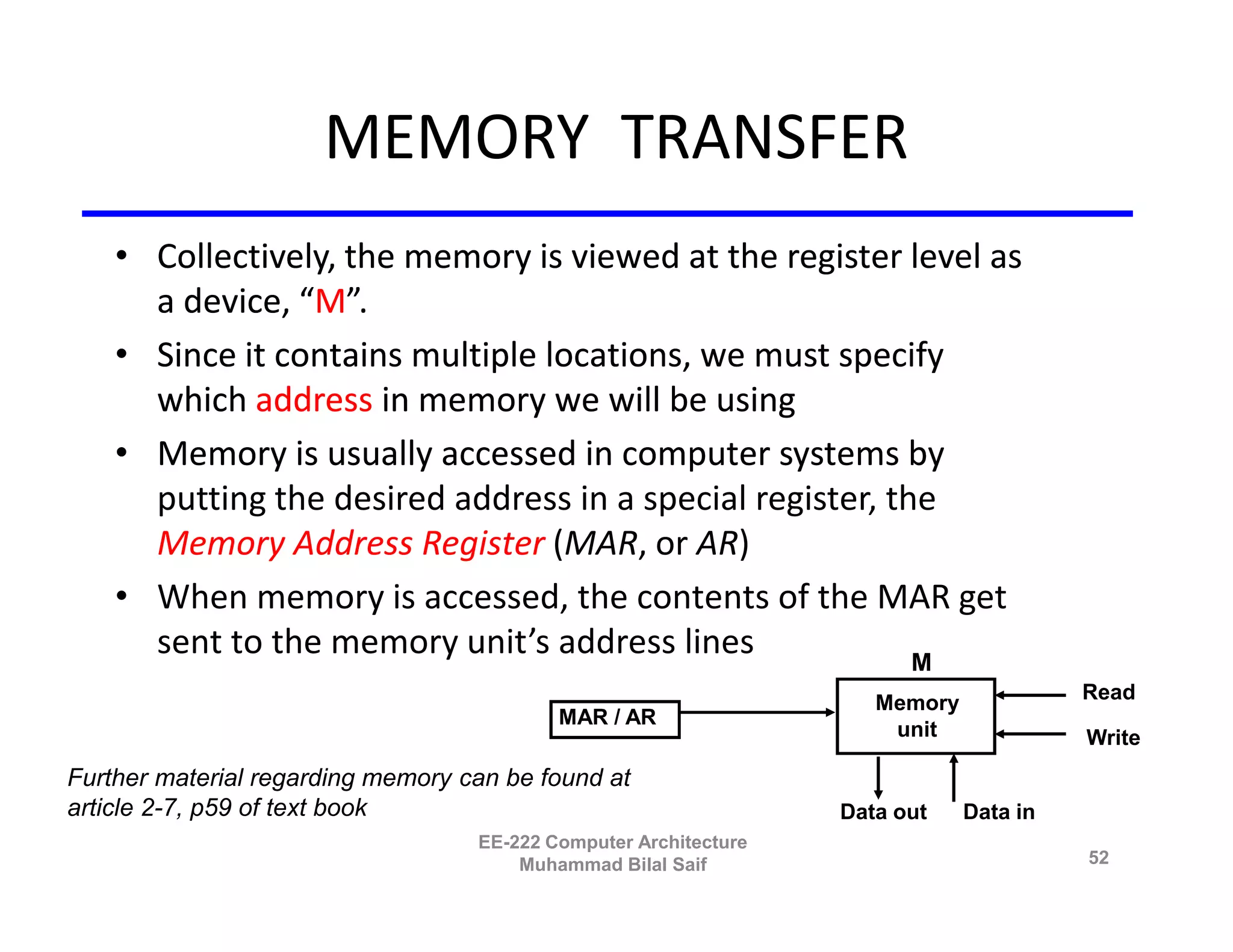

![SUMMARY OF R. TRANSFER MICROOPERATIONS

A B Transfer content of reg. B into reg. A

AR DR(AD) Transfer content of AD portion of reg. DR into reg. AR

A constant Transfer a binary constant into reg. A

BUS R1, Transfer content of R1 into bus and, at the same time,

R2 BUS transfer content of bus into R2

AR Address register

DR Data register

M[AR] Memory word specified by reg. AR

M Equivalent to M[AR]

DR M Memory read operation: transfers content of

memory word specified by AR into DR

M DR Memory write operation: transfers content of

DR into memory word specified by AR

EE-222 Computer Architecture

Muhammad Bilal Saif 55](https://image.slidesharecdn.com/lecture2-100803195947-phpapp02/75/Lecture-2-22-2048.jpg)