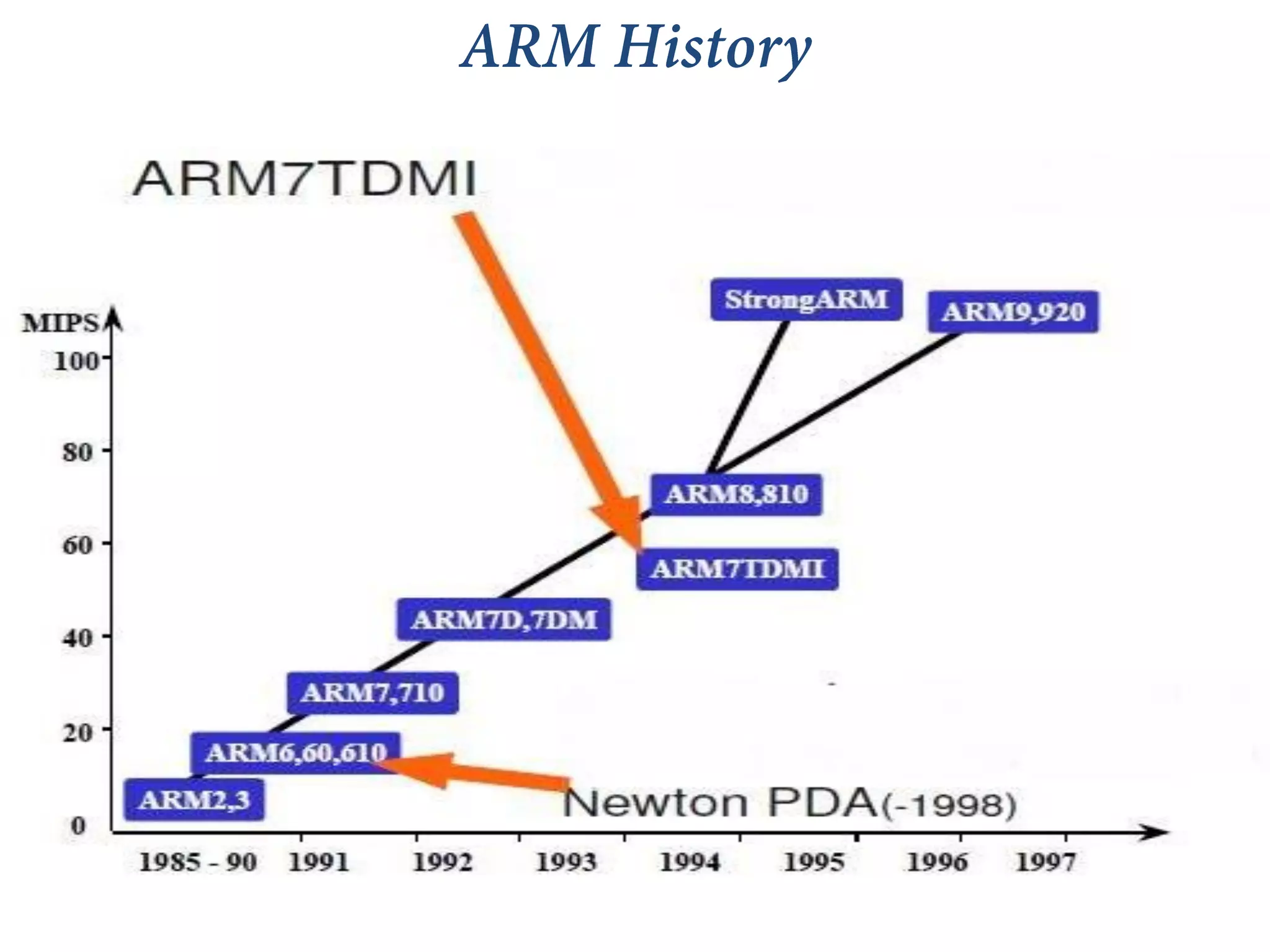

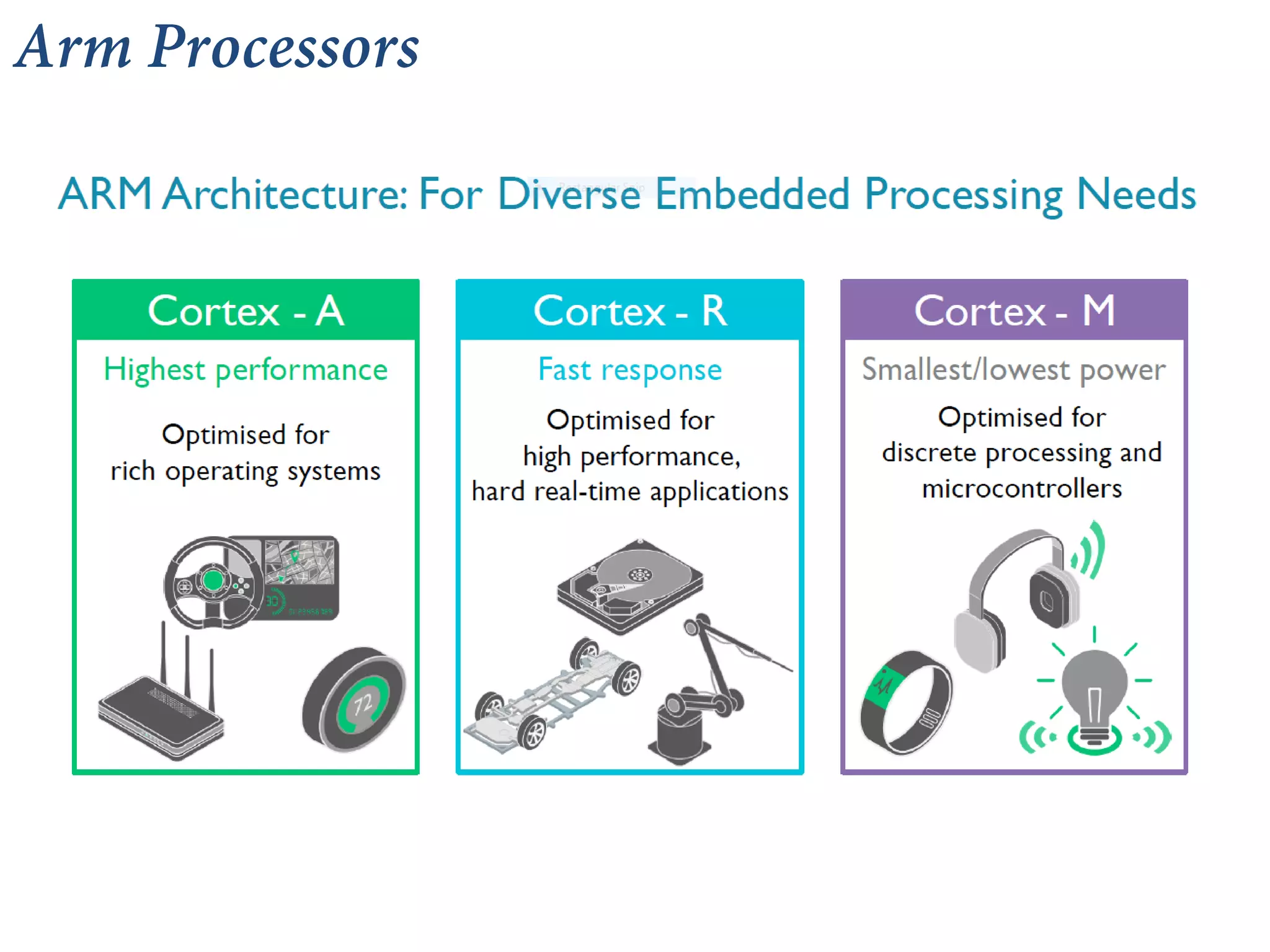

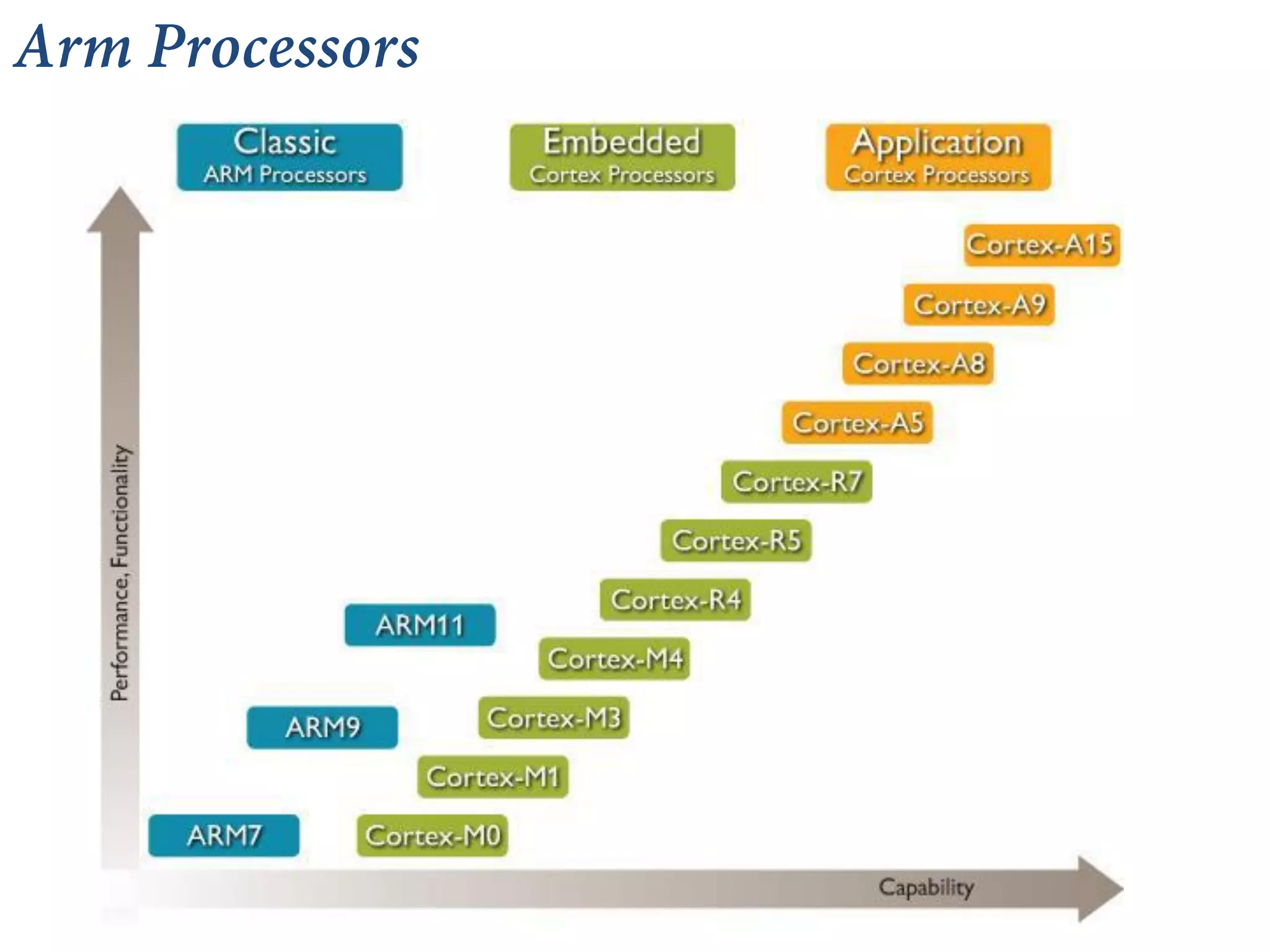

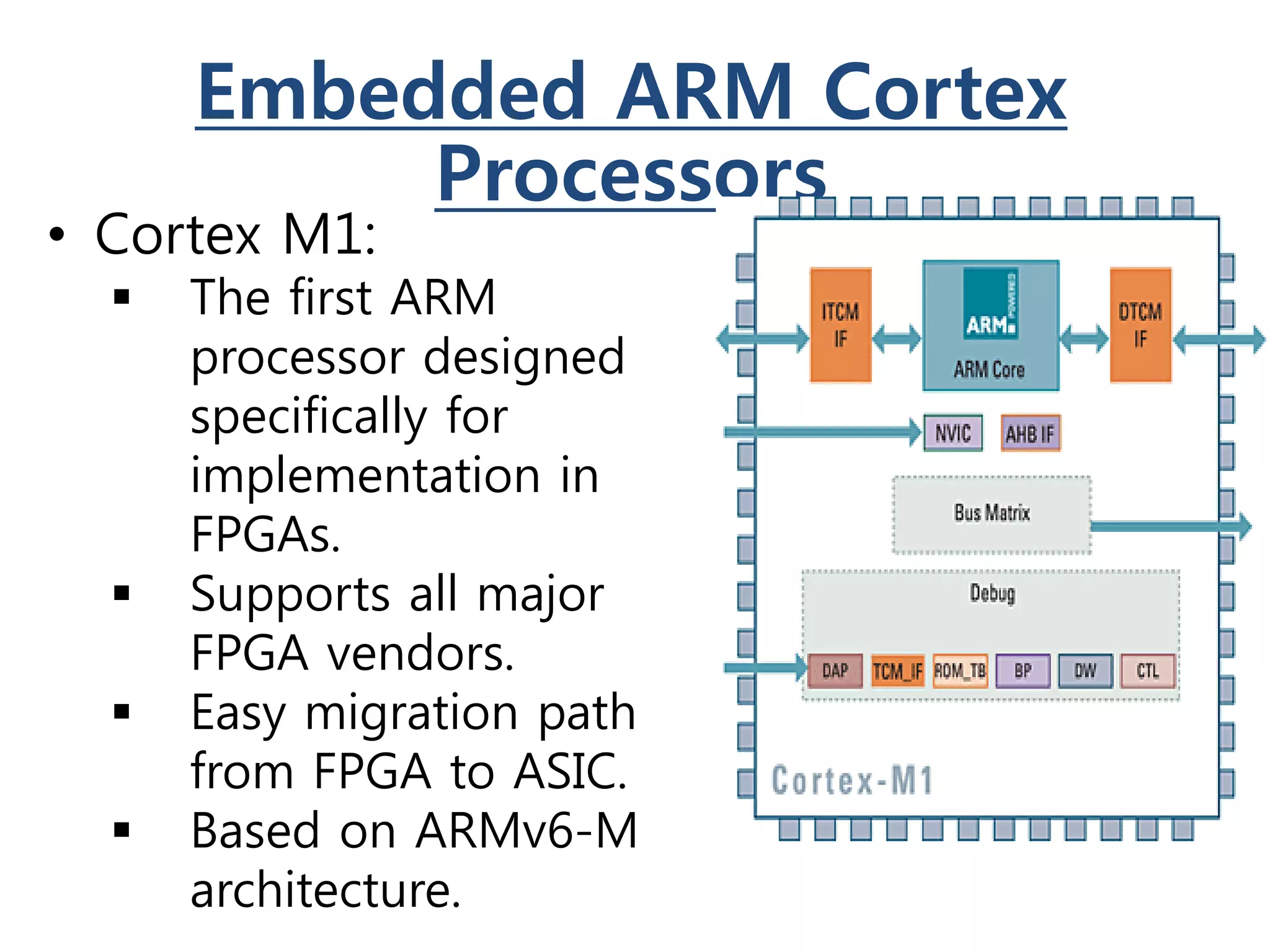

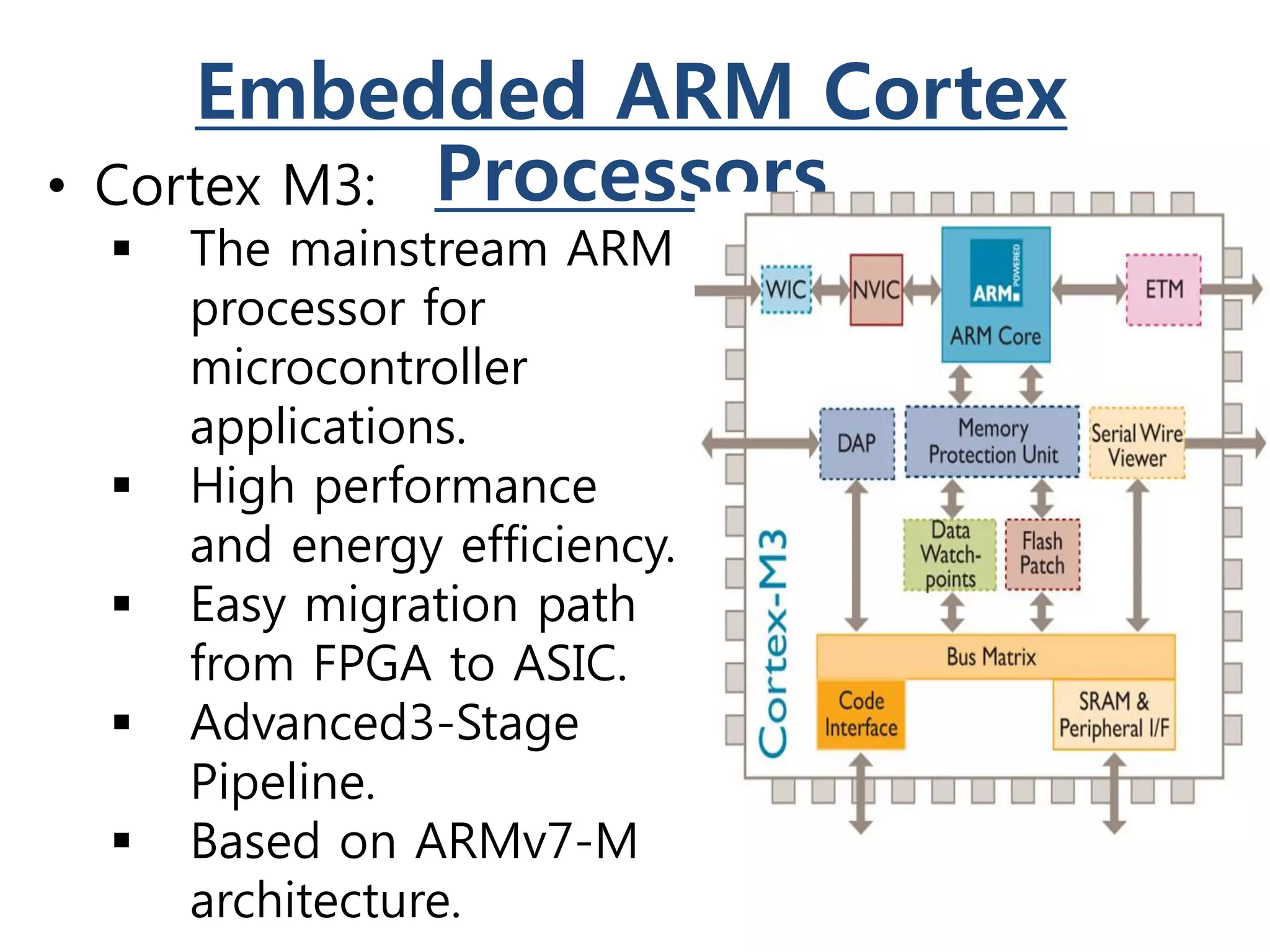

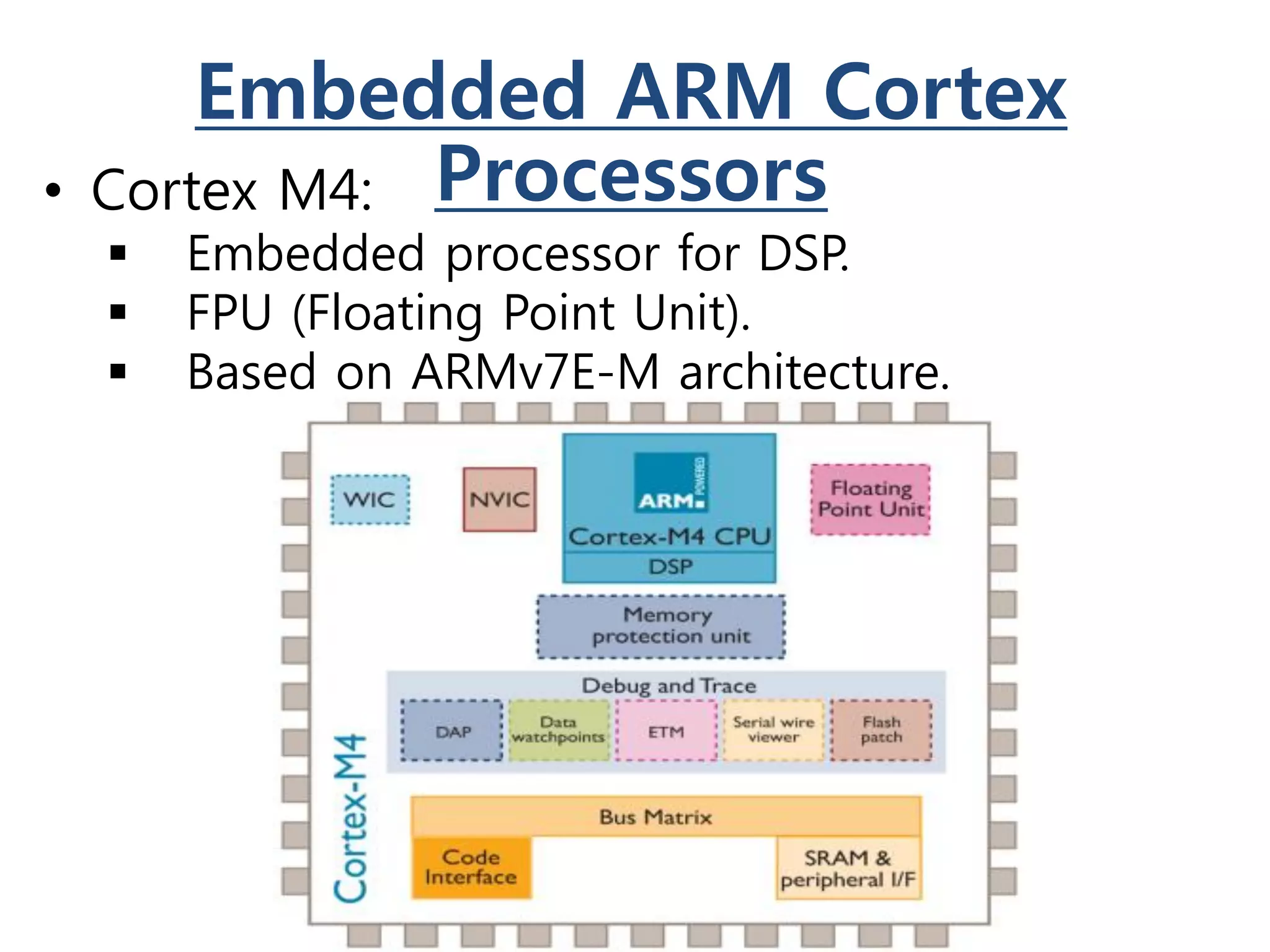

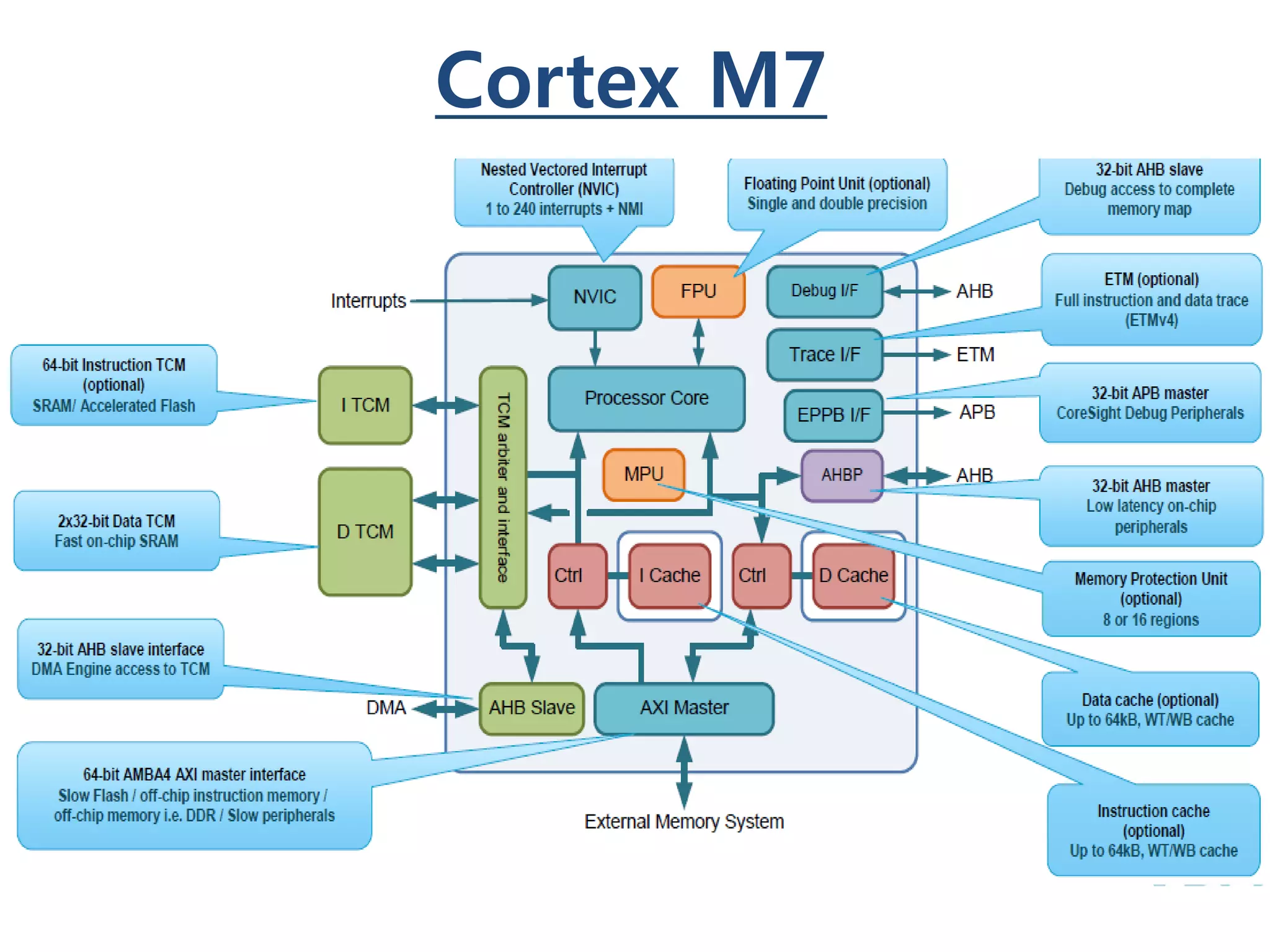

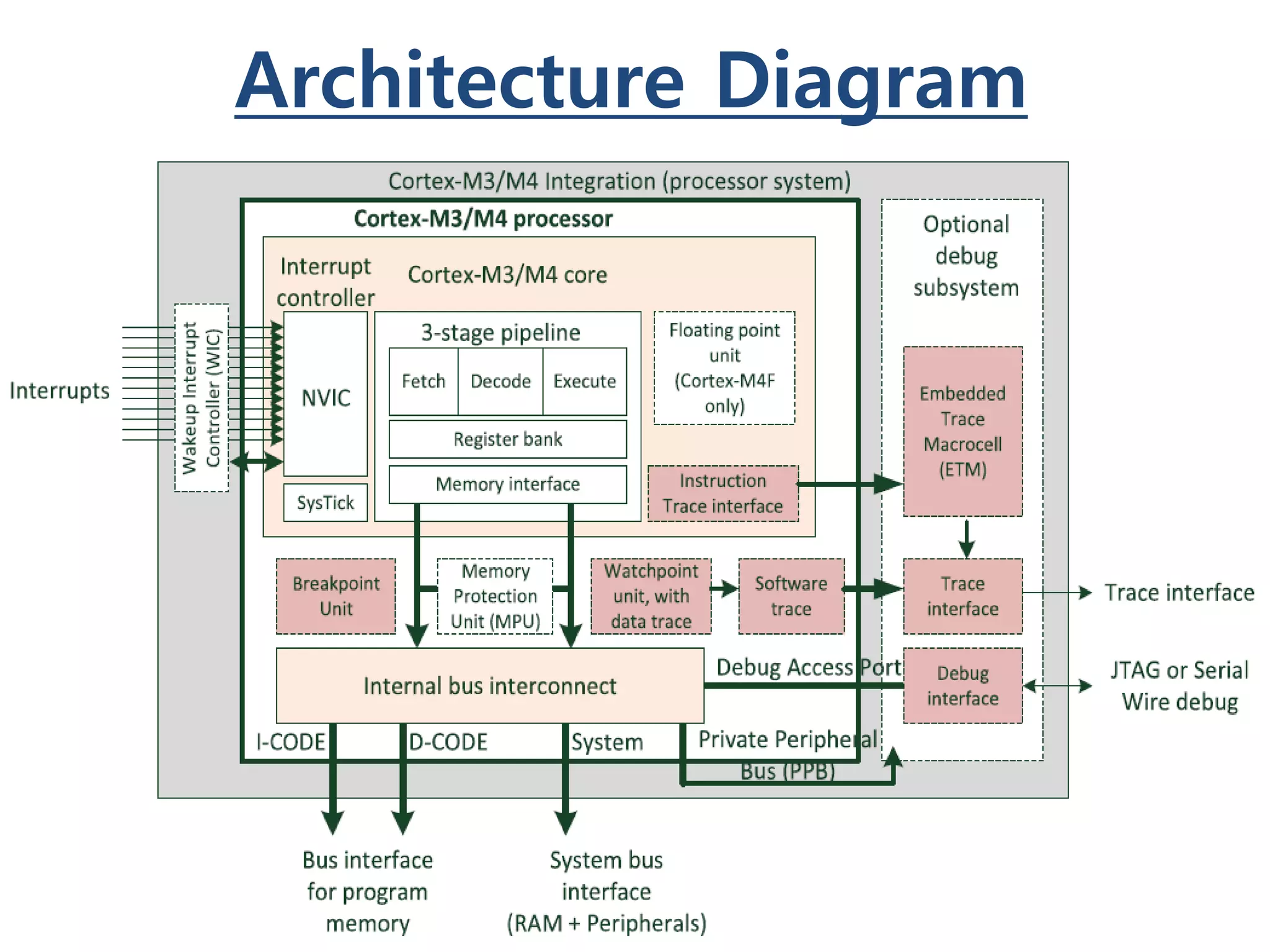

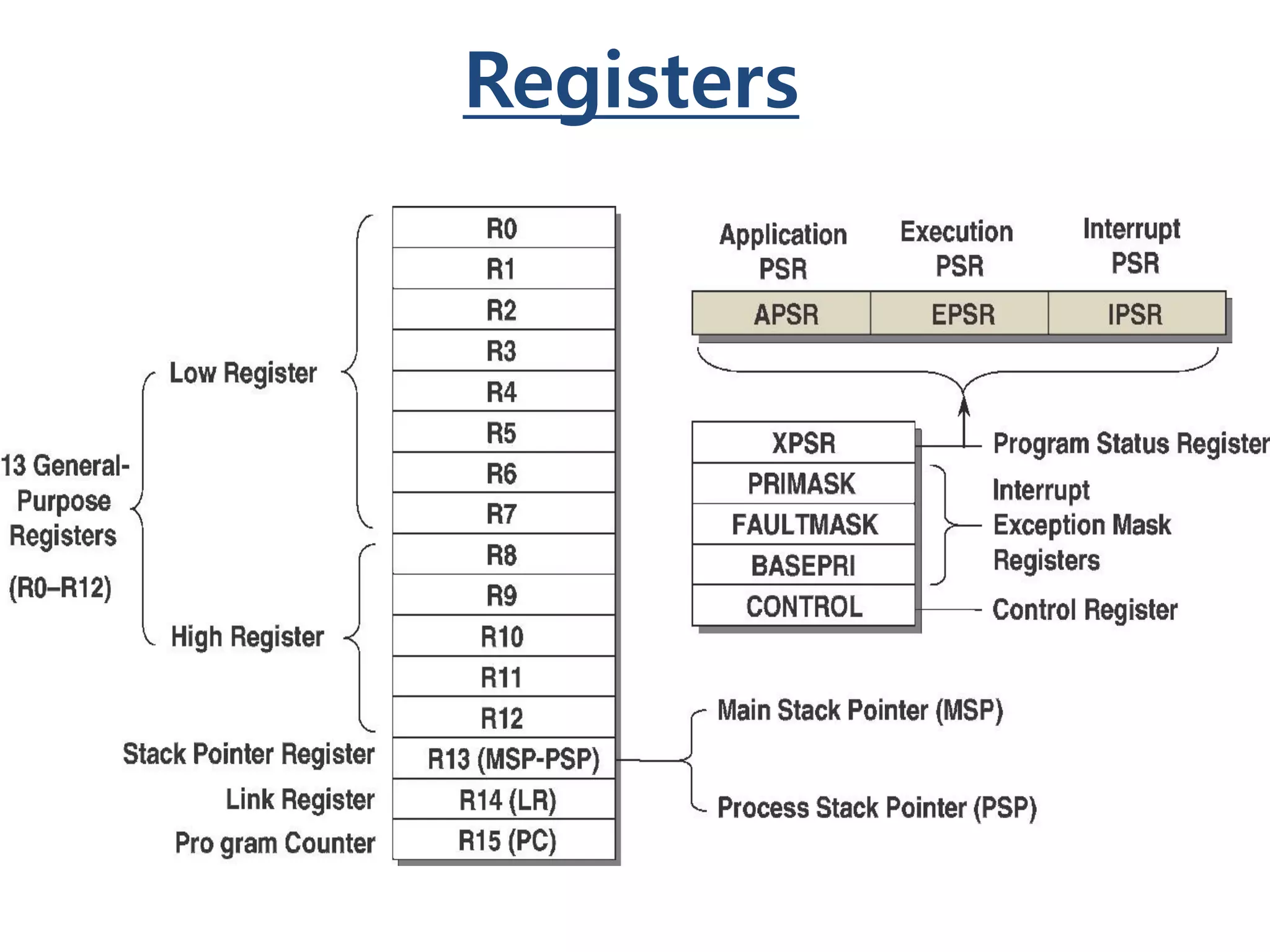

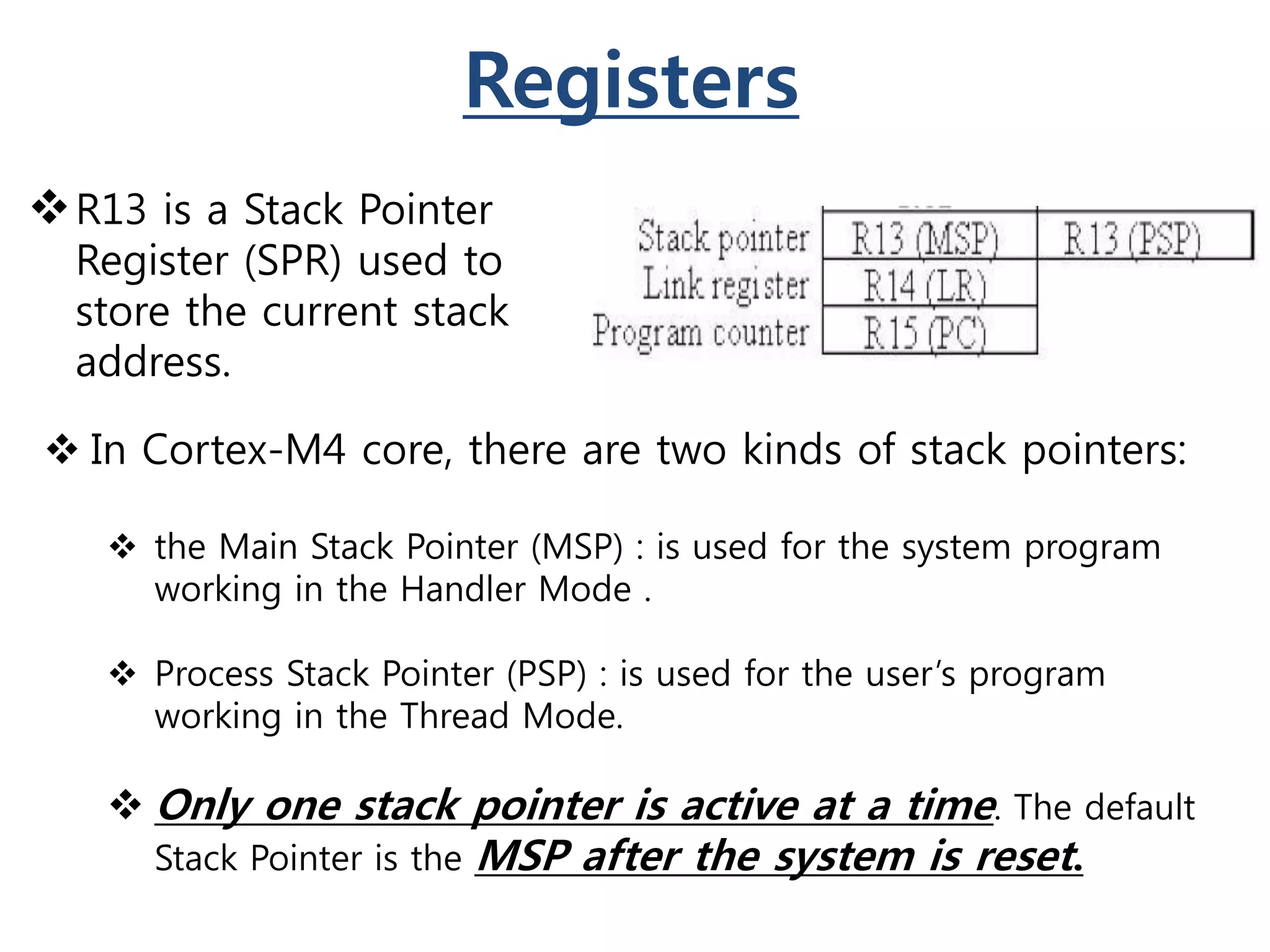

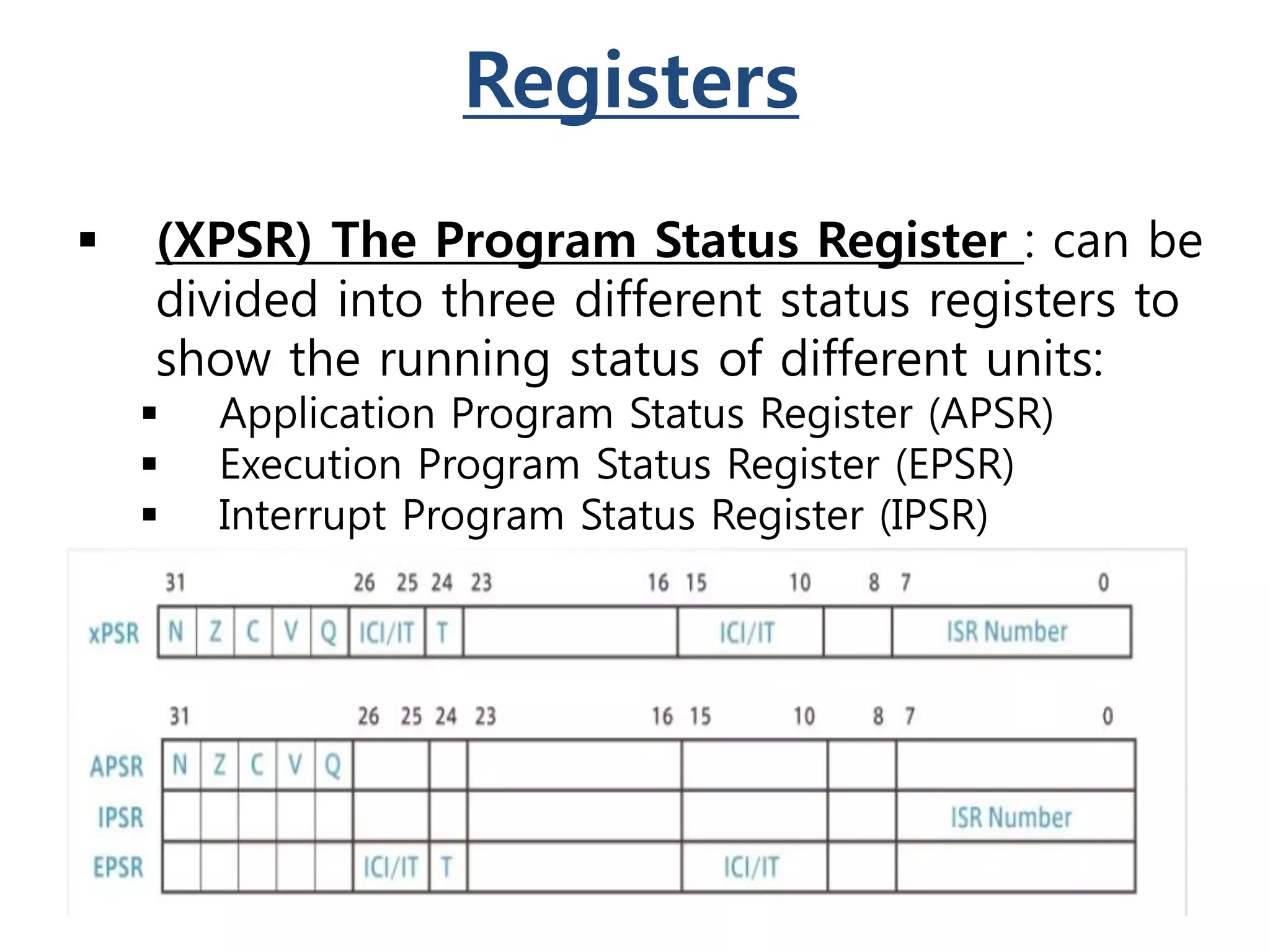

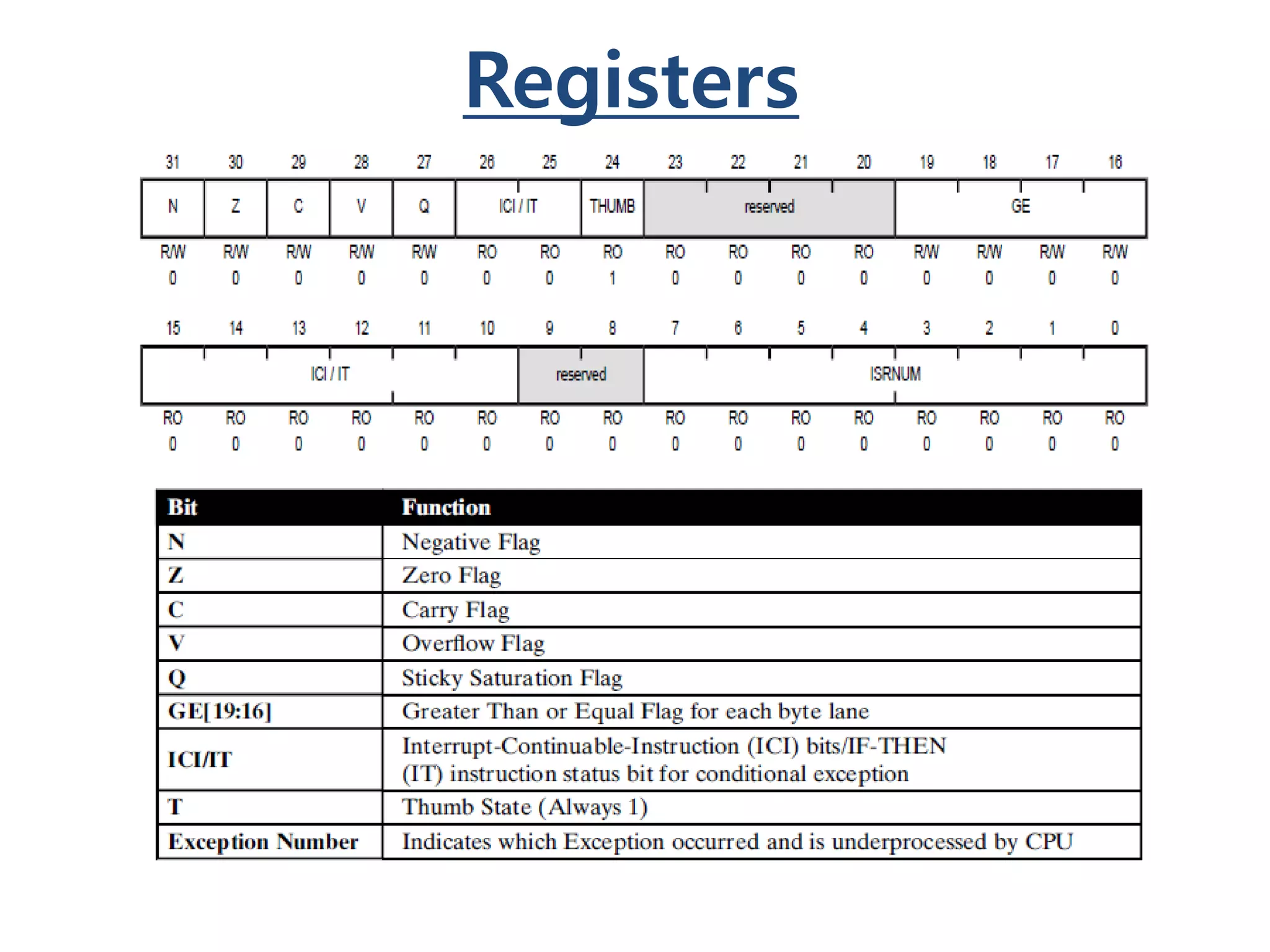

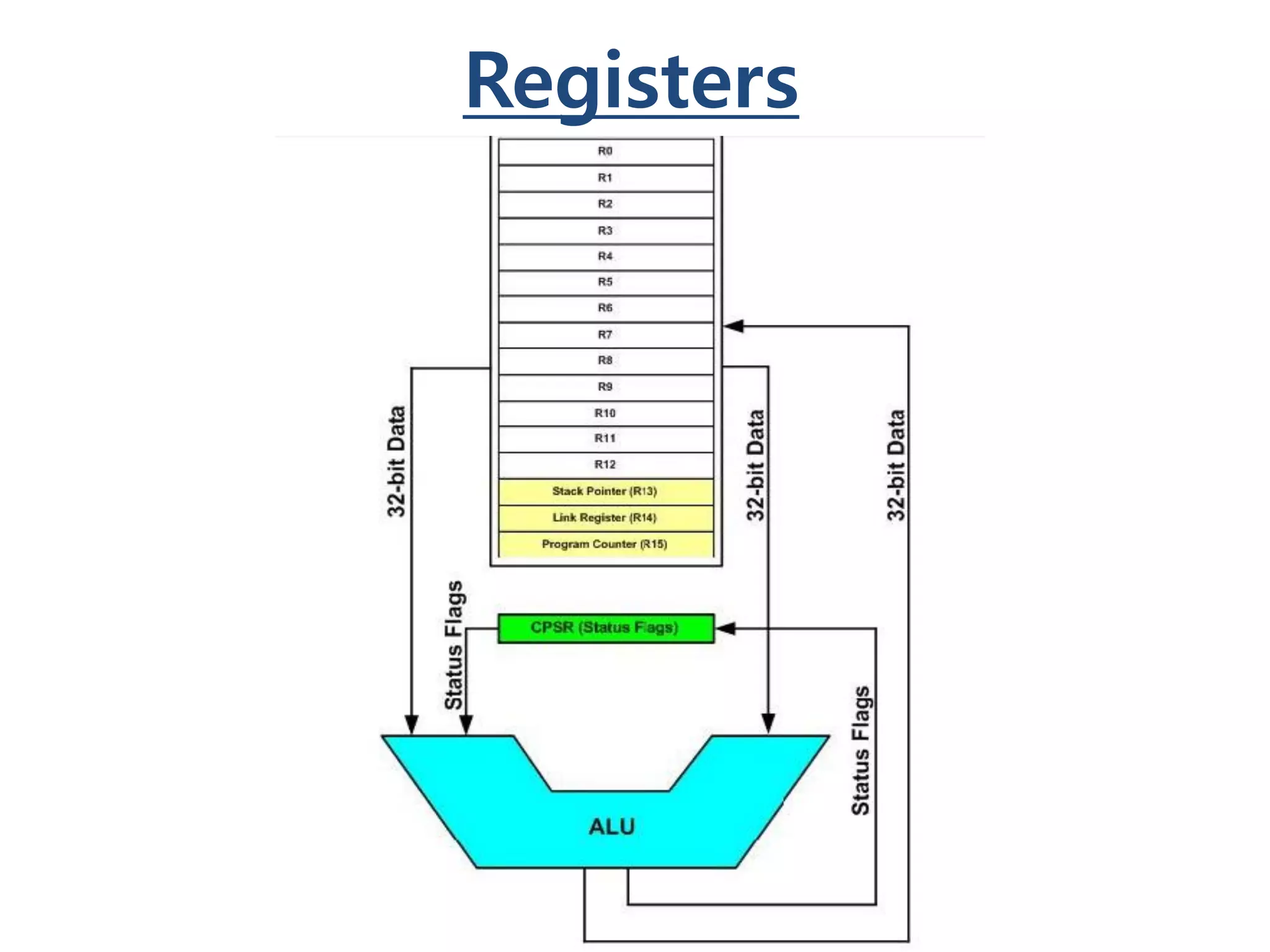

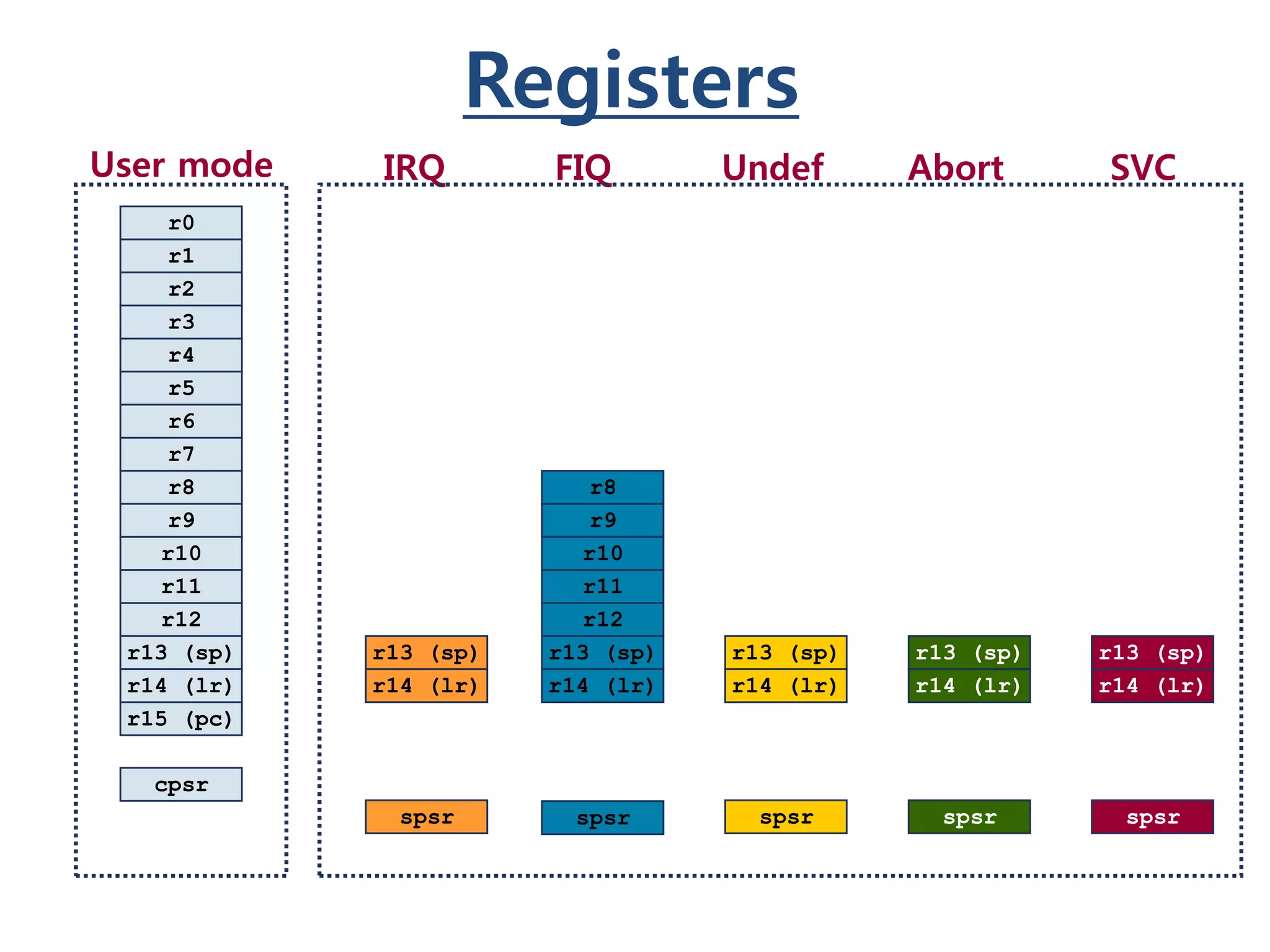

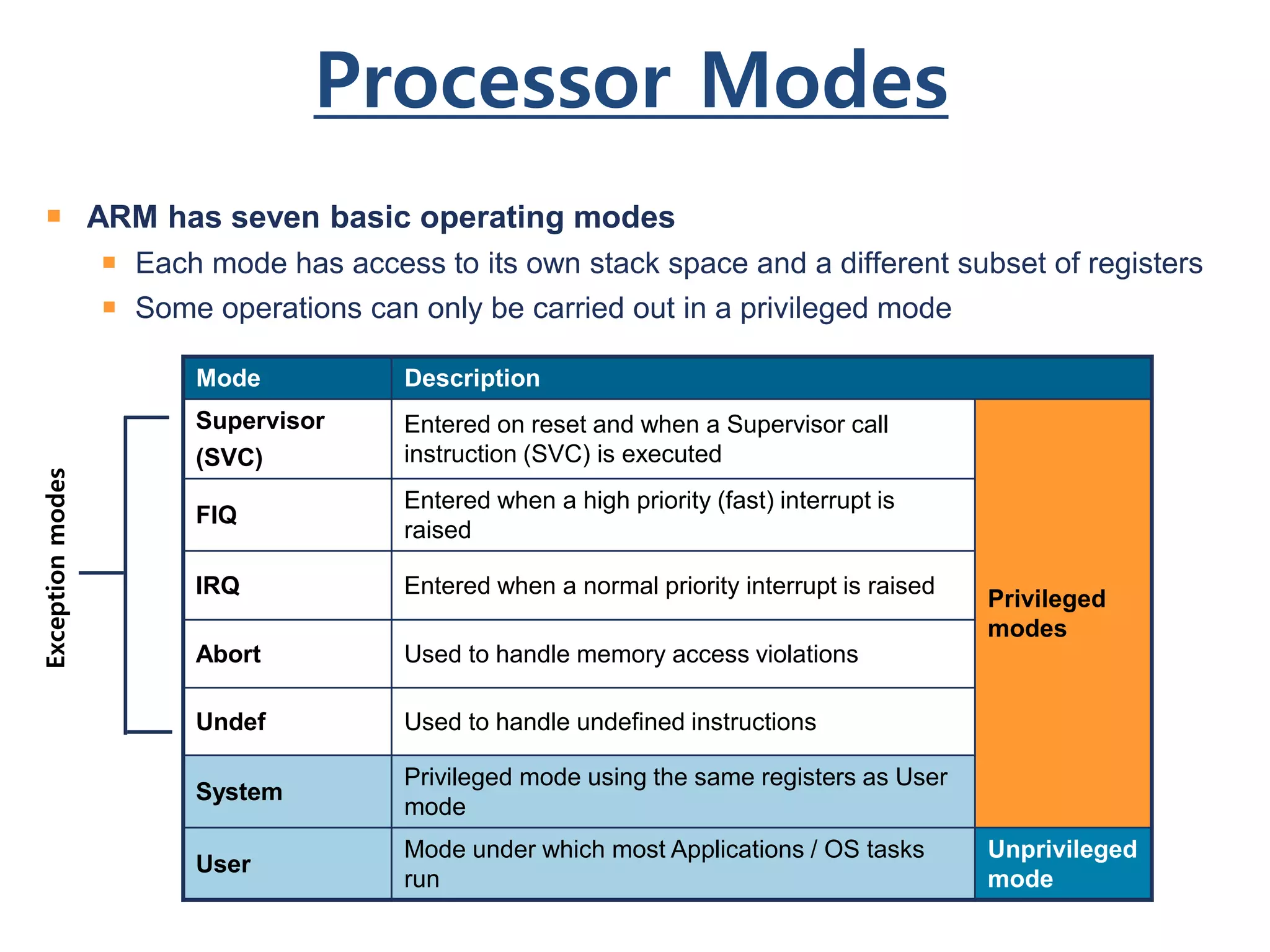

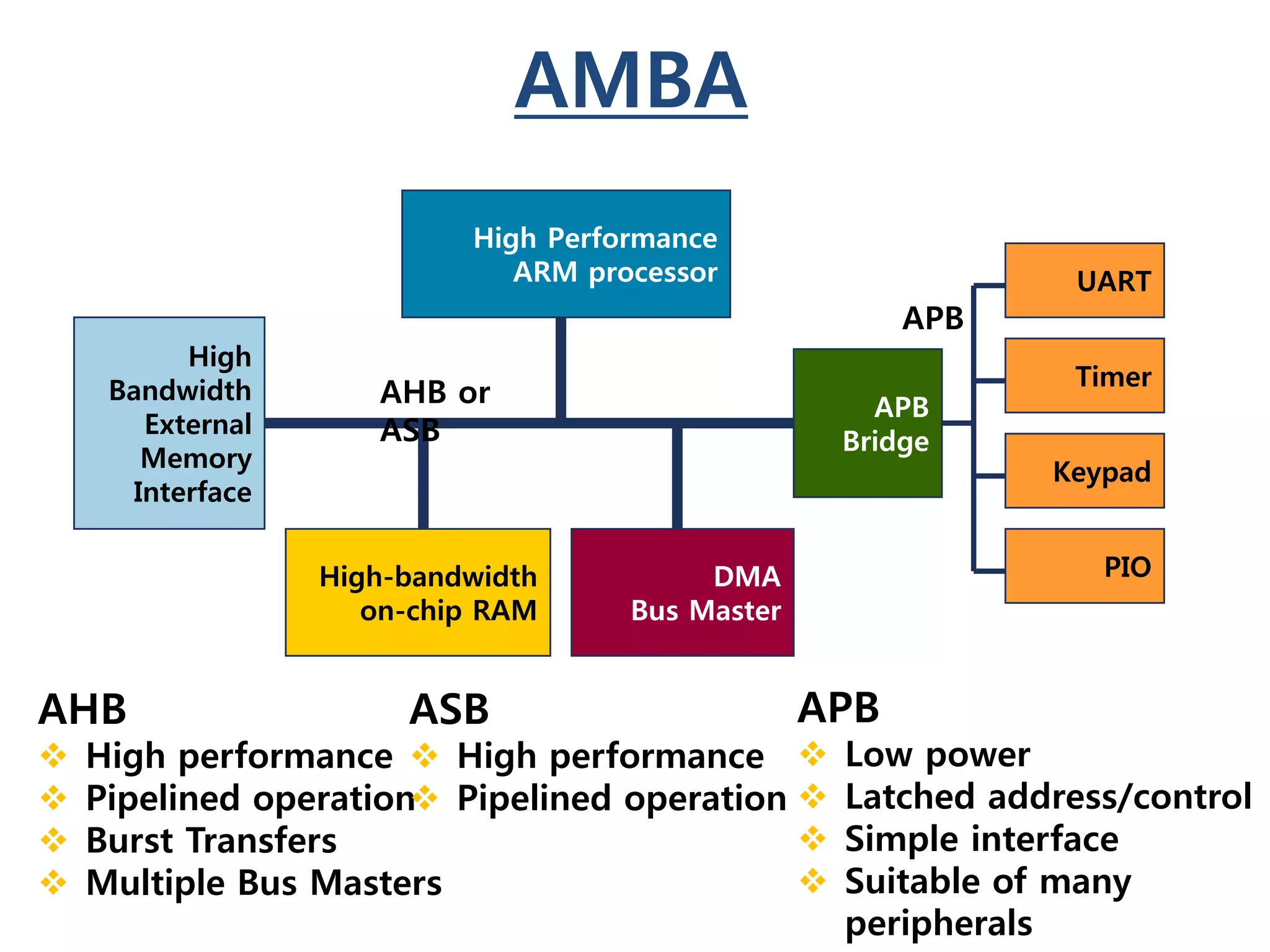

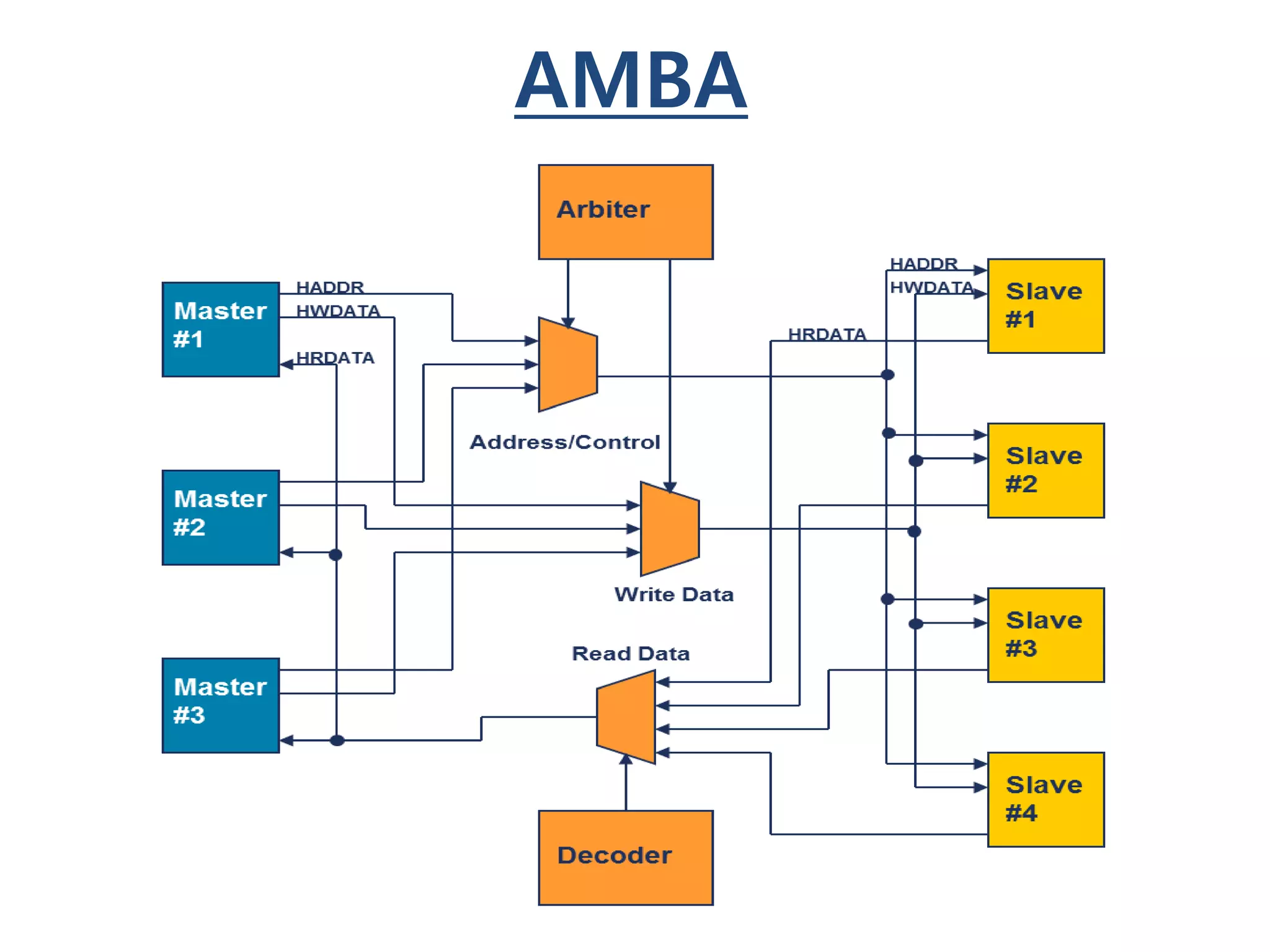

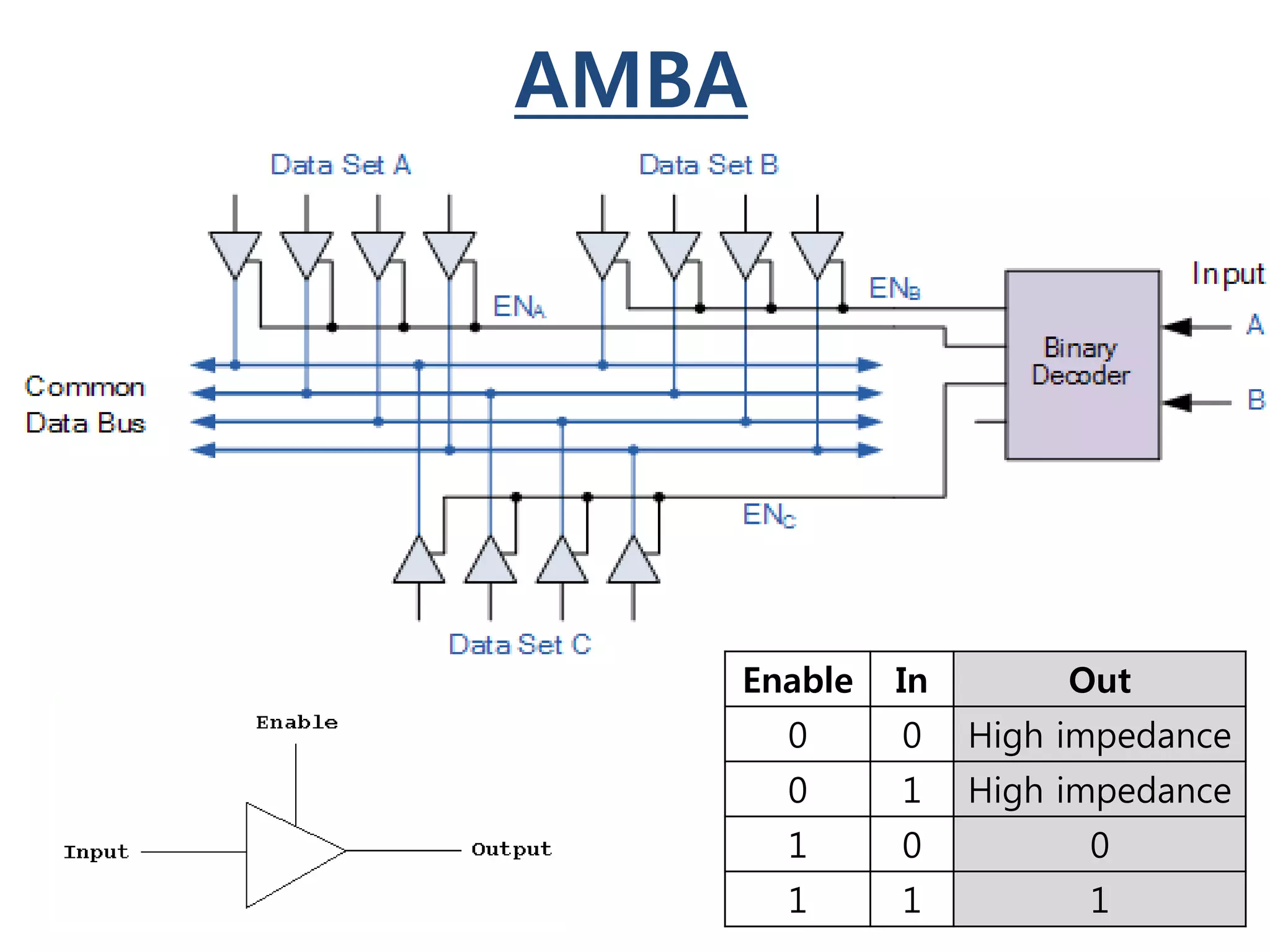

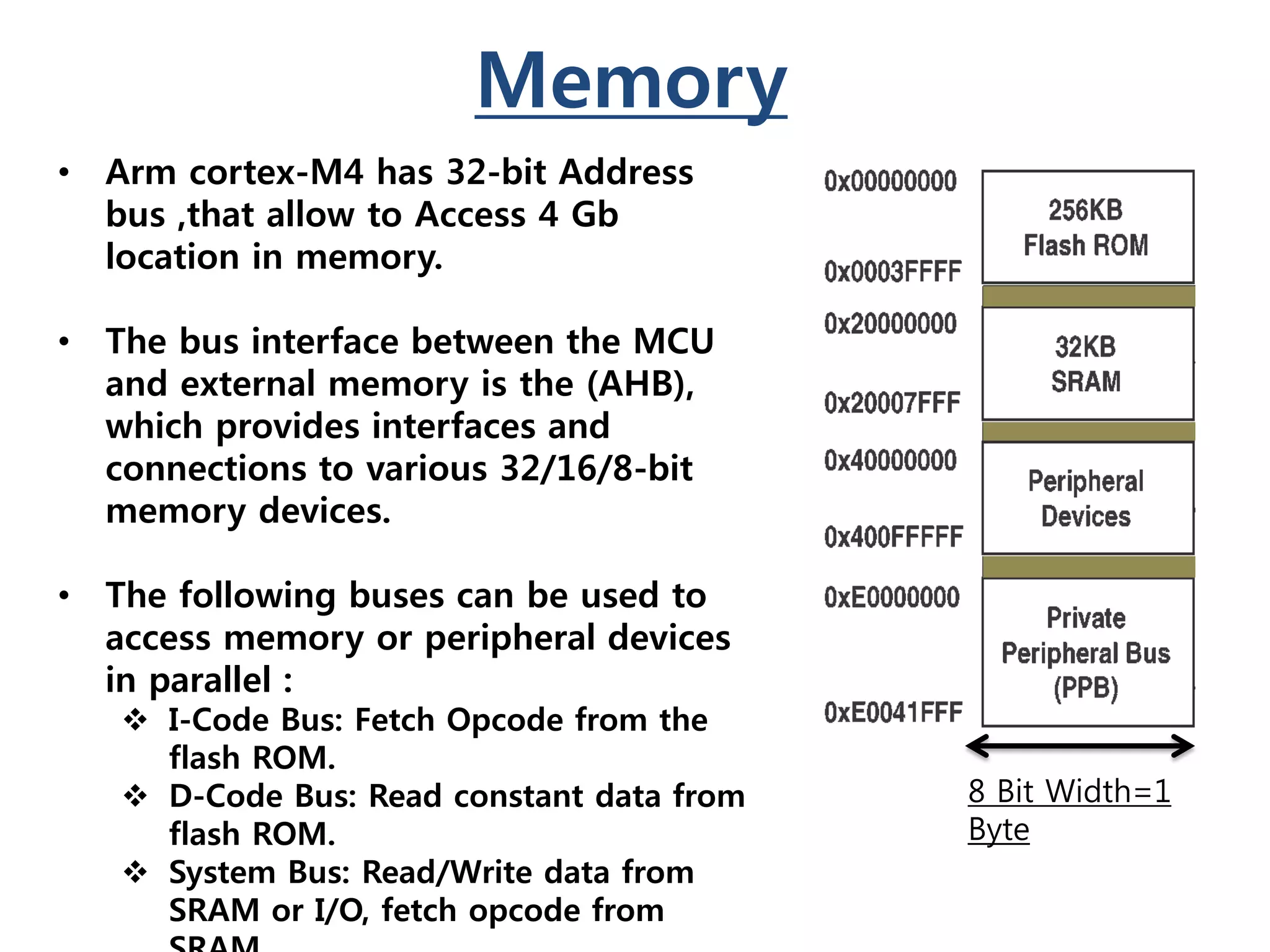

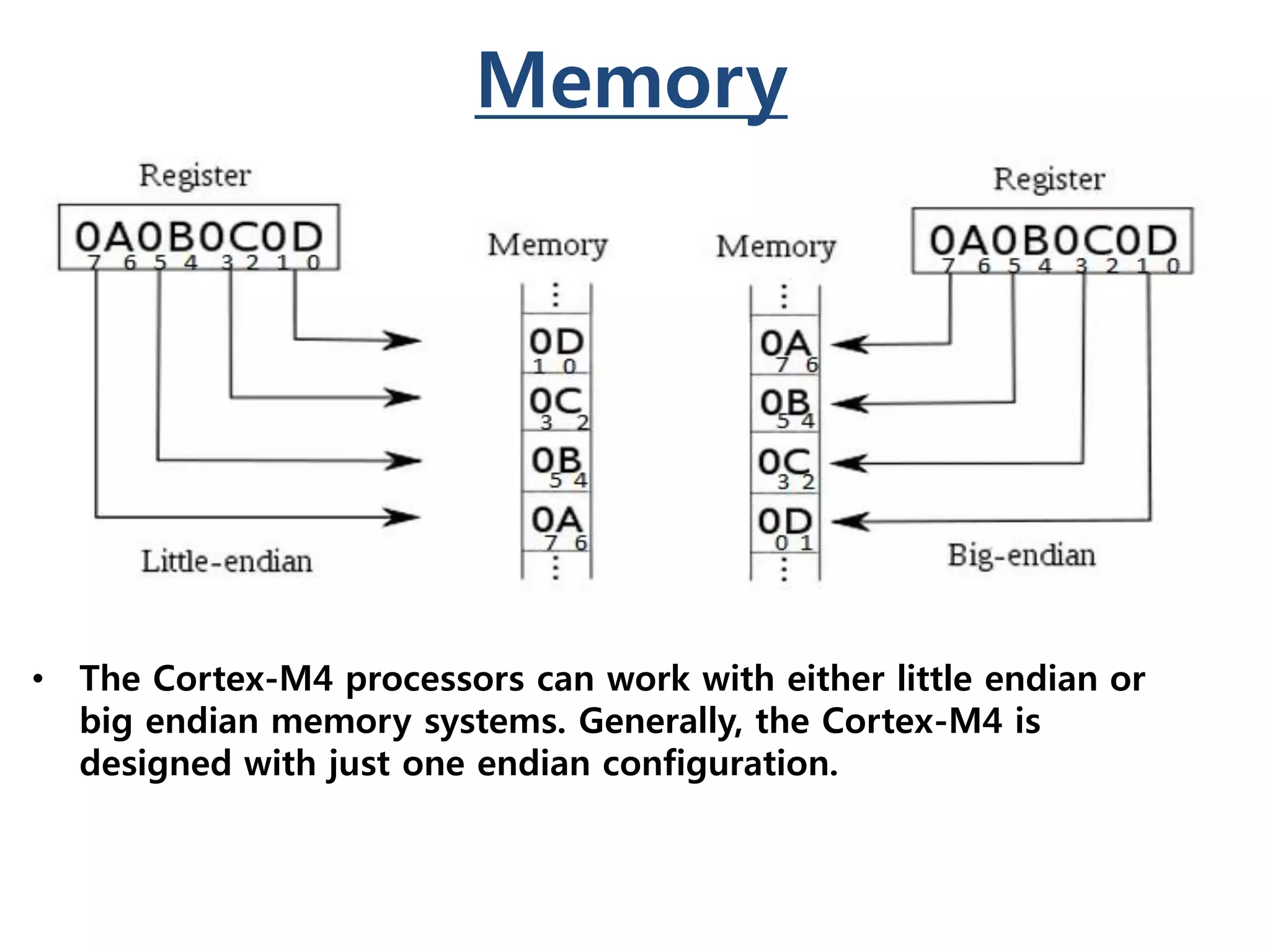

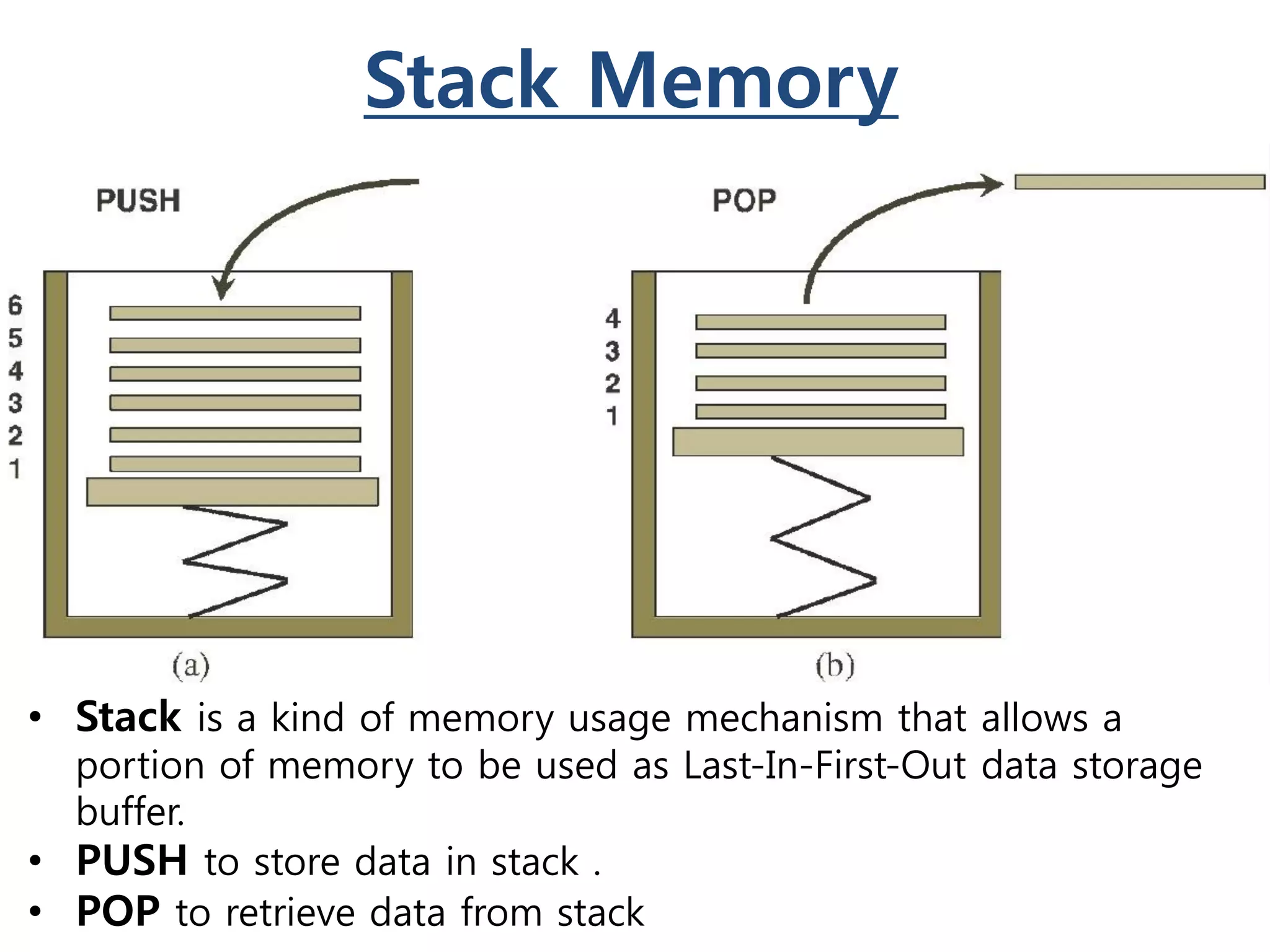

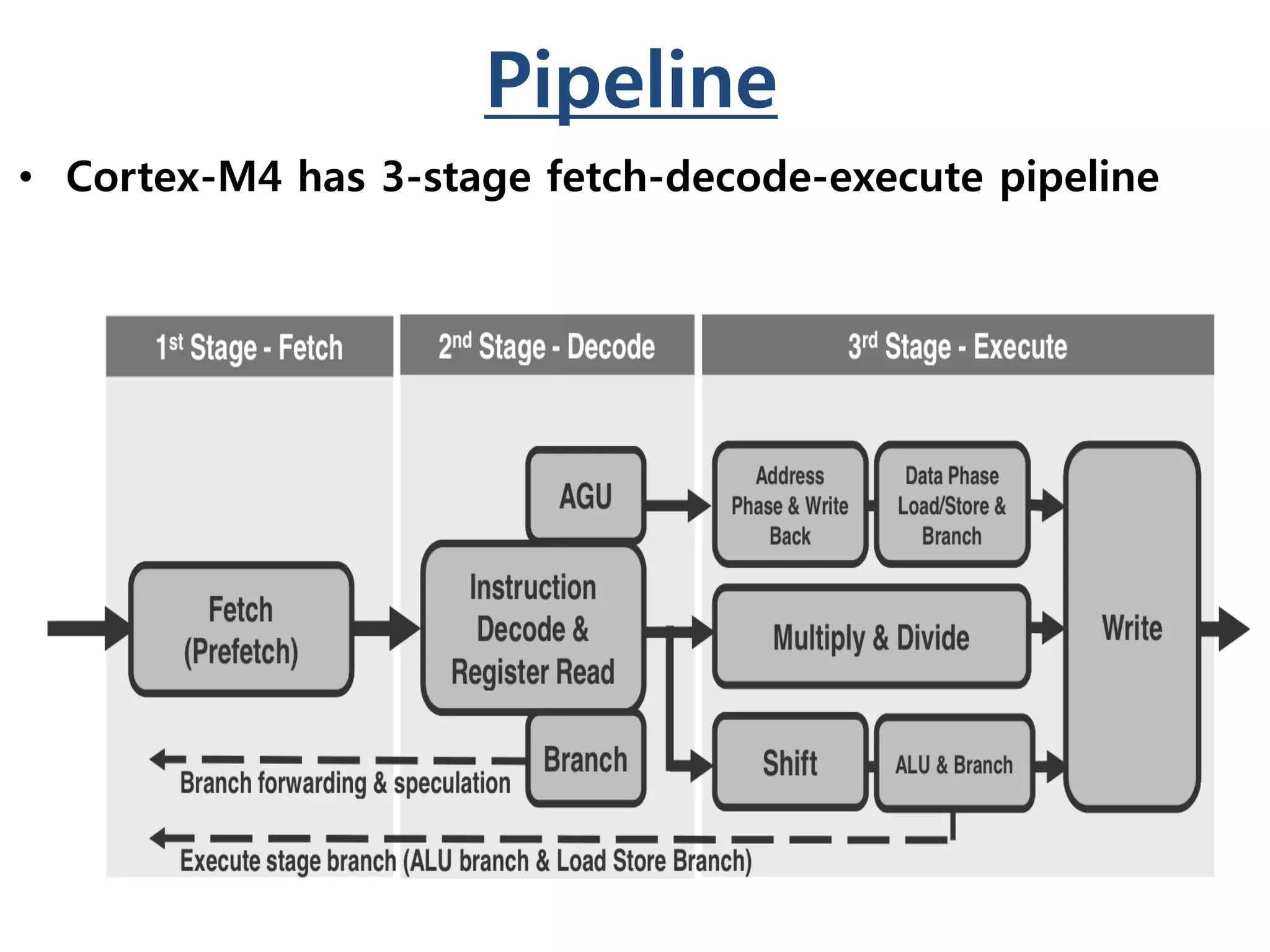

The document provides an overview of ARM architecture and its various embedded Cortex processors, highlighting their features and applications. It discusses the company's history, the architecture's load store nature, and the registers used in the ARM Cortex-M4 processor. Additionally, it outlines the Advanced Microcontroller Bus Architecture (AMBA) and stack memory operations within the ARM systems.