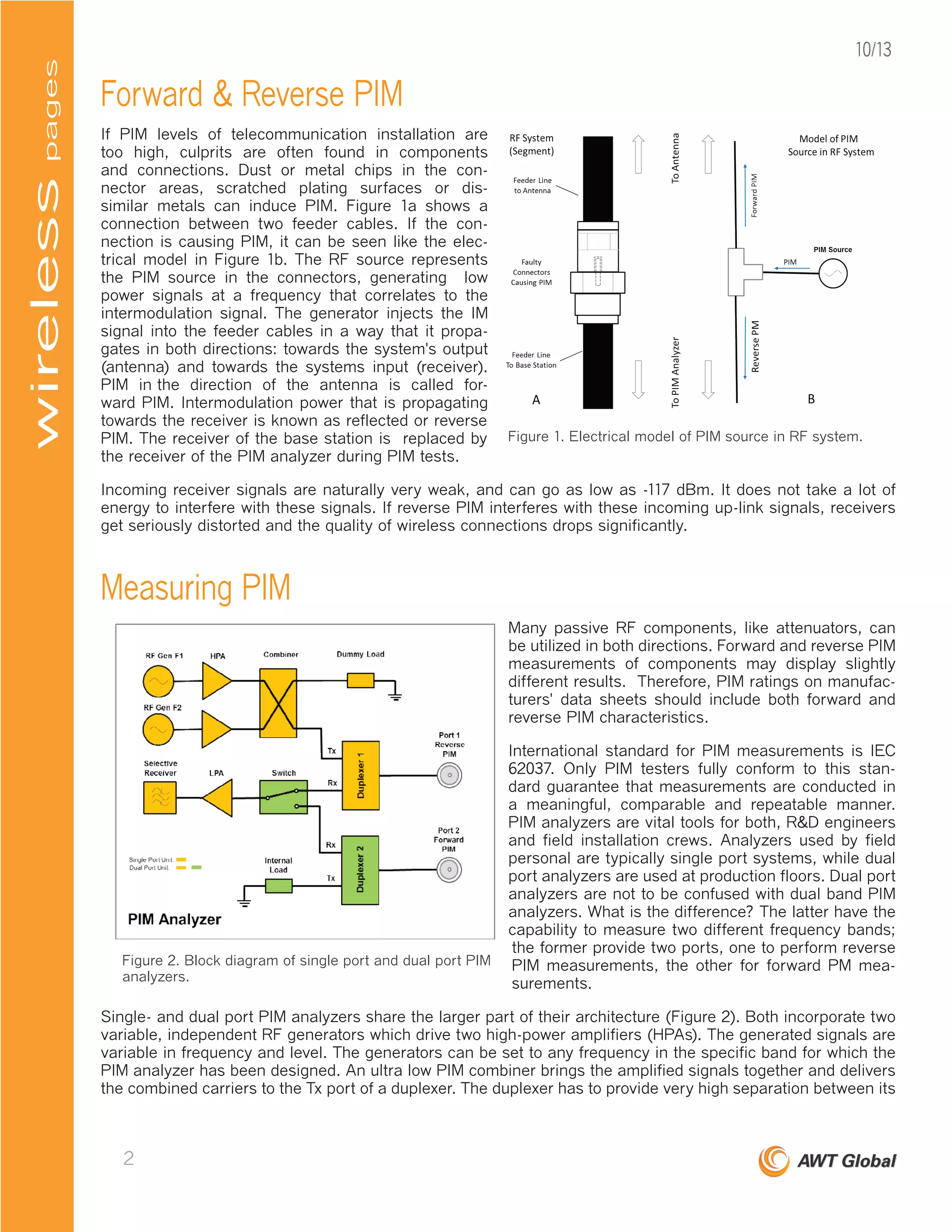

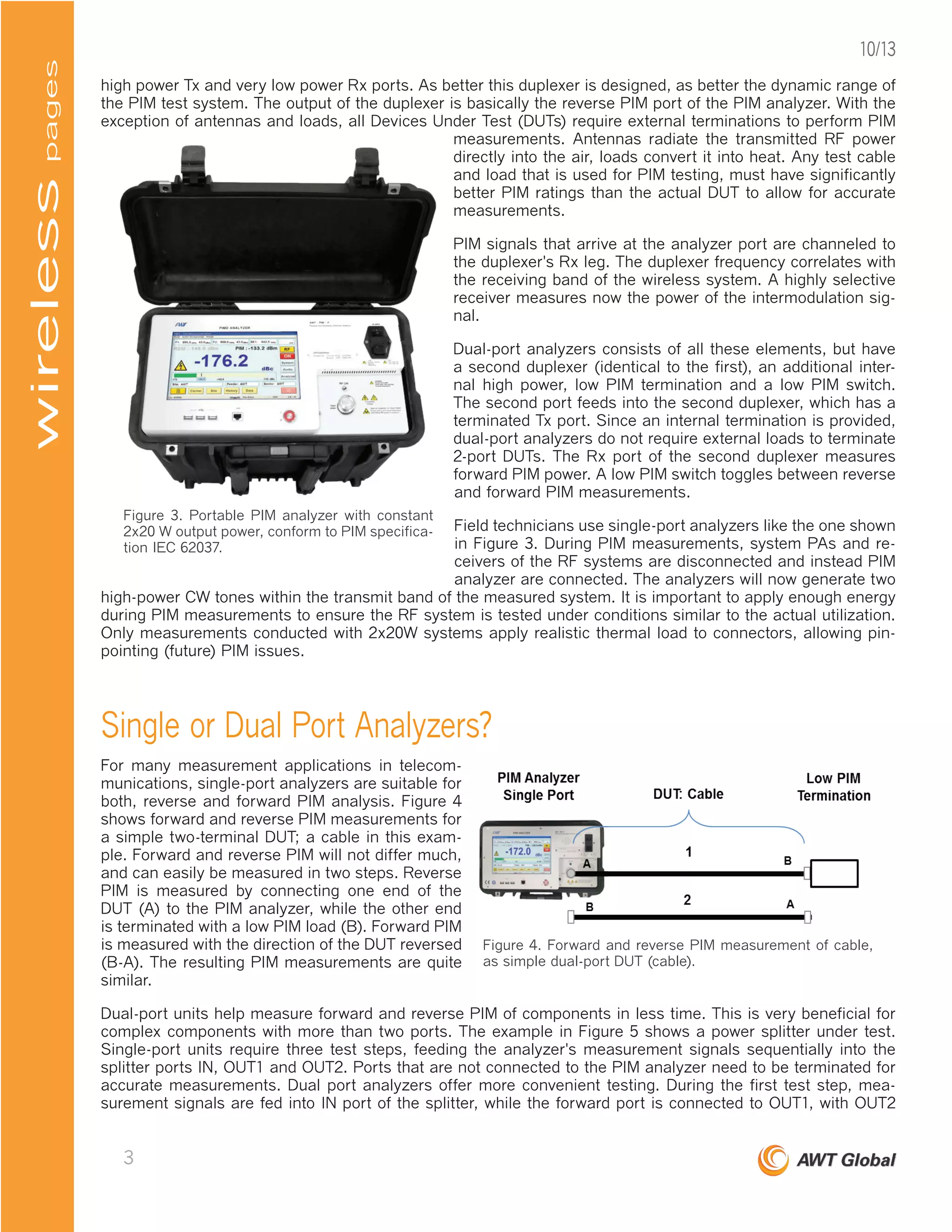

Passive intermodulation (PIM) distortion poses significant challenges for telecommunications operators due to increasing data demands and can severely degrade mobile network quality. PIM is caused by non-linear behavior of passive components when multiple RF signals are present, and it can lead to dropped calls and poor service for users. Effective testing and measurement of PIM using specialized analyzers is crucial to ensure network performance and mitigate interference, particularly in systems with multiple carriers.