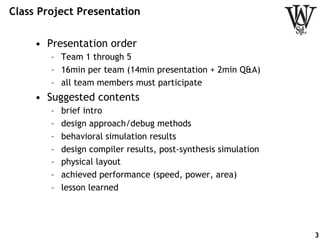

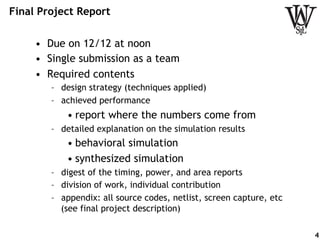

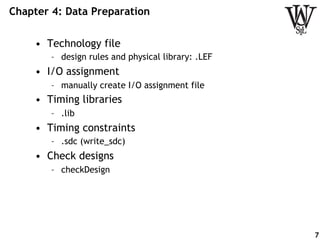

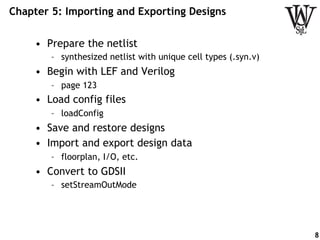

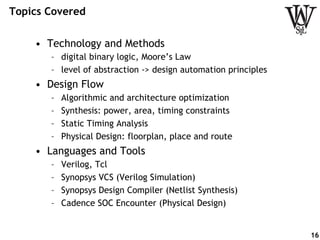

This document summarizes the final class topics for an integrated circuit design course. It outlines the final project presentation requirements, including timing and content. It also provides details on the final project report due date and required contents. The document concludes with an overview of the course topics covered, including design flow, languages and tools, and trends in integrated circuit design.