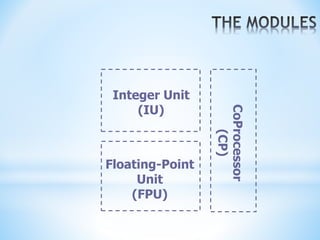

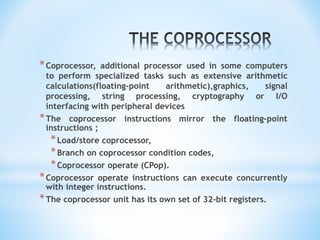

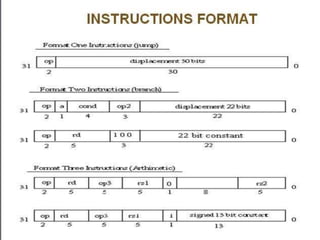

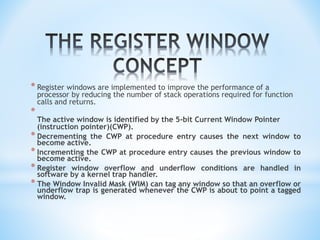

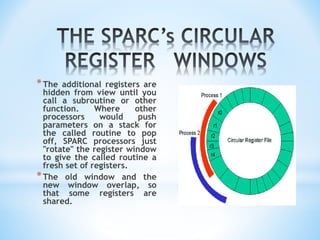

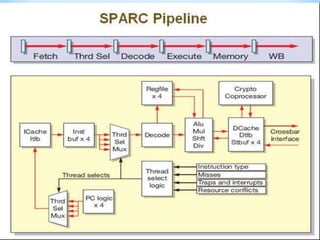

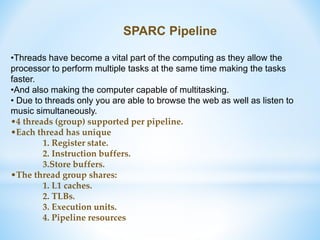

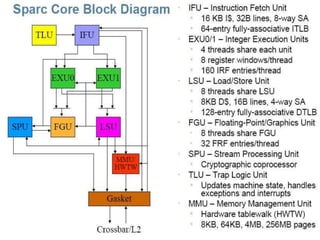

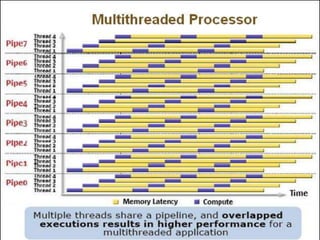

SPARC (Scalable Processor Architecture), developed by the SPARC Consortium and adopted by Sun Microsystems in 1985, is a CPU instruction set architecture based on RISC designs. It features an integer unit, floating-point unit, and optional coprocessor, supporting advanced multitasking through threads and register window techniques for efficient function calls. The architecture includes various instruction categories and is designed for high performance with concurrent processing capabilities.