Recommended

PDF

FPGA エクストリーム・コンピューティング第3回

PDF

Pynqでカメラ画像をリアルタイムfastx コーナー検出

PPTX

PDF

PDF

PDF

PPTX

ODP

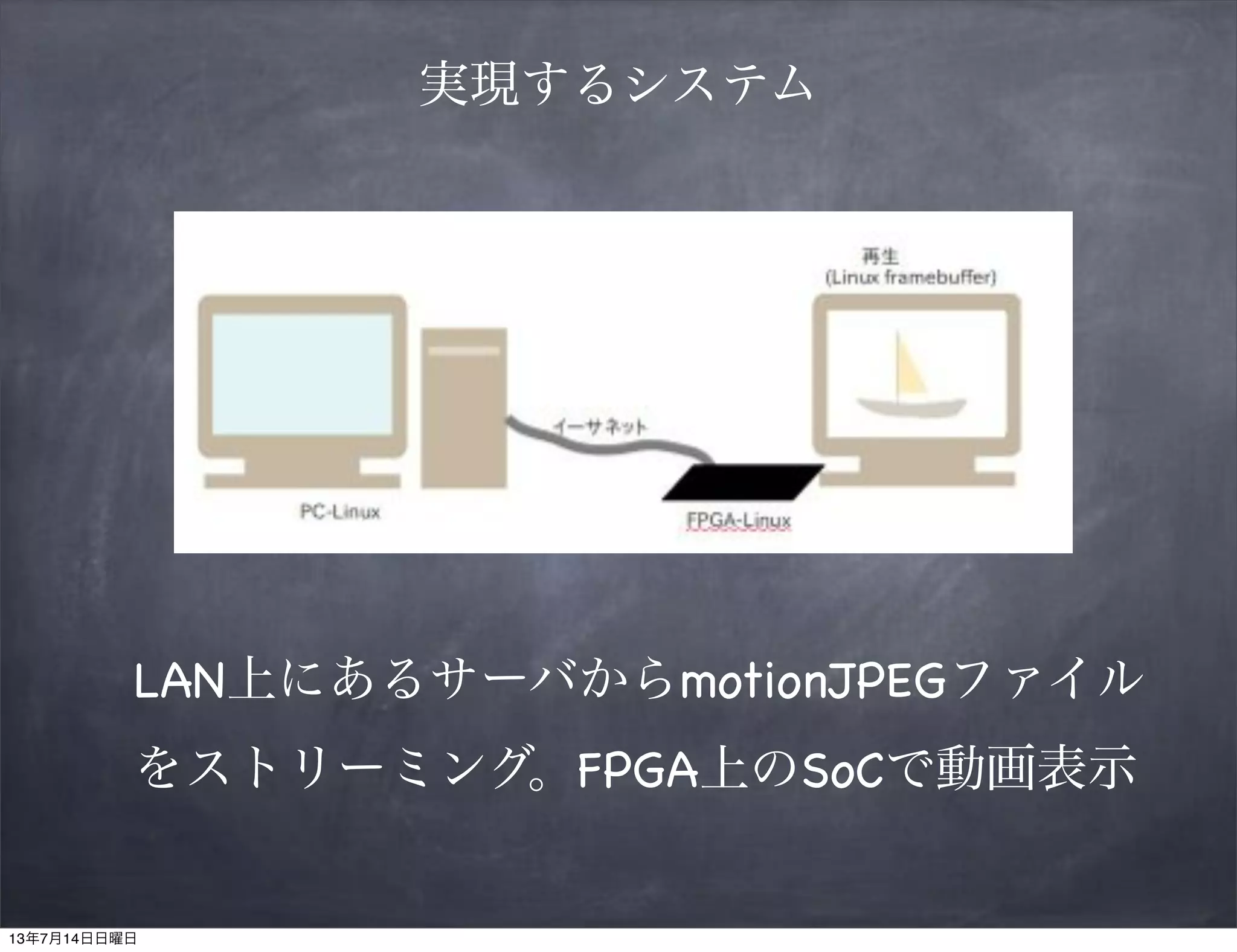

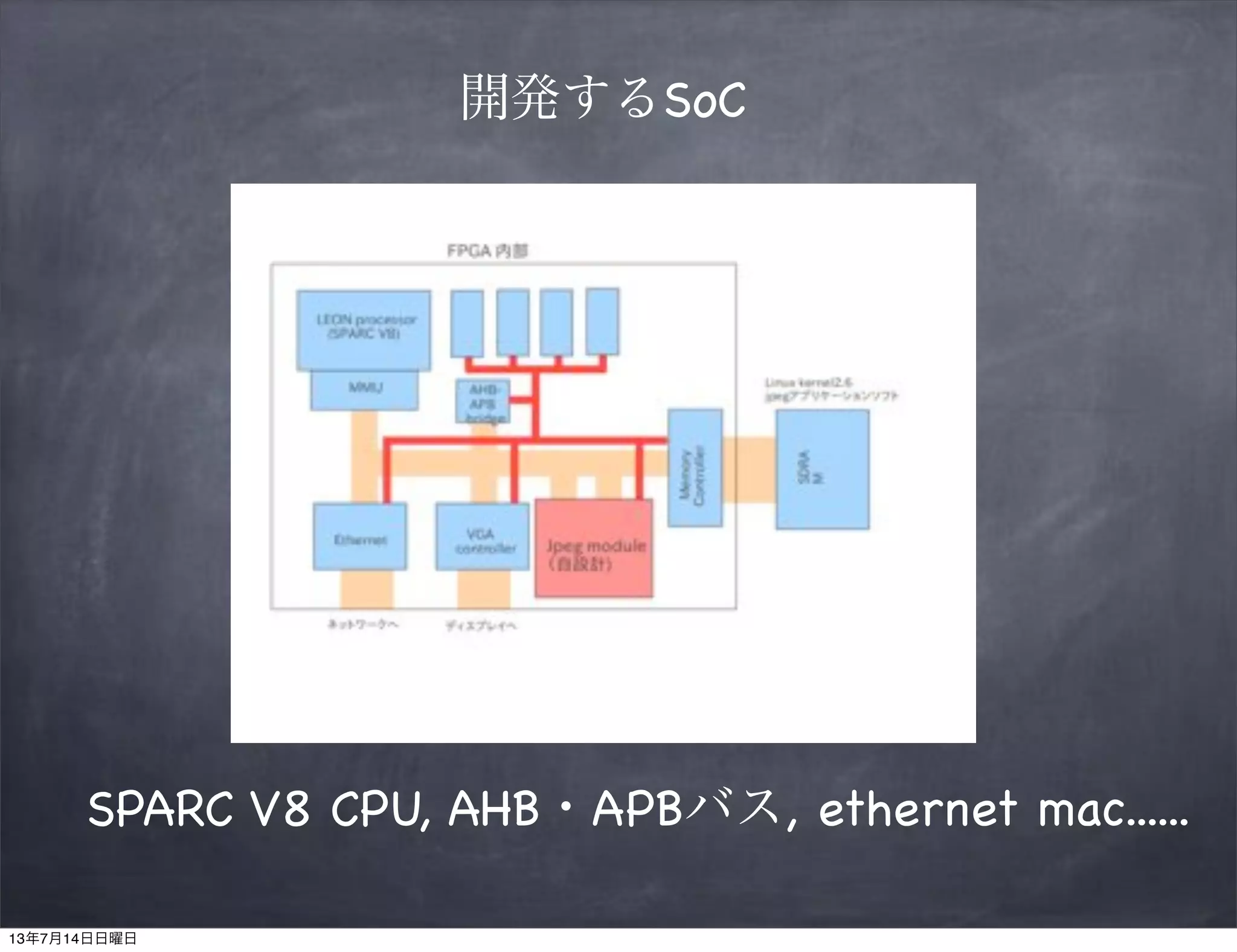

Open Design Computer Project - Tsukuba.pm

PDF

PPTX

PPTX

PPTX

研究者のための Python による FPGA 入門

PDF

高位合成ツールVivado hlsのopen cv対応

PPT

PPTX

PDF

PPTX

PDF

Xilinx SDSoC(2016.2)解体新書ソフトウェア編

PPTX

PDF

Halide, Darkroom - 並列化のためのソフトウェア・研究

PDF

Vivado hlsのシミュレーションとhlsストリーム

PPTX

画像処理ライブラリ OpenCV で 出来ること・出来ないこと

PPTX

PDF

PDF

PDF

PDF

PDF

OpenCV4Androidで画像処理アプリのススメ

PDF

PDF

More Related Content

PDF

FPGA エクストリーム・コンピューティング第3回

PDF

Pynqでカメラ画像をリアルタイムfastx コーナー検出

PPTX

PDF

PDF

PDF

PPTX

ODP

Open Design Computer Project - Tsukuba.pm

What's hot

PDF

PPTX

PPTX

PPTX

研究者のための Python による FPGA 入門

PDF

高位合成ツールVivado hlsのopen cv対応

PPT

PPTX

PDF

PPTX

PDF

Xilinx SDSoC(2016.2)解体新書ソフトウェア編

PPTX

PDF

Halide, Darkroom - 並列化のためのソフトウェア・研究

PDF

Vivado hlsのシミュレーションとhlsストリーム

PPTX

画像処理ライブラリ OpenCV で 出来ること・出来ないこと

PPTX

PDF

PDF

PDF

PDF

PDF

OpenCV4Androidで画像処理アプリのススメ

Similar to オープンハードセミナー

PDF

PDF

PPTX

Microsemi FPGA はいいぞ,FPGAの紹介とおさそい

PDF

PDF

PDF

PPTX

動き検出勉強会リメイク。過去の発表のリメイク版です。動き検出のアルゴリズムとOpencvのオプションについてまとめました

PDF

Fpga online seminar by fixstars (1st)

PDF

PDF

PDF

FPGAをロボット(ROS)で「やわらかく」使うには

PDF

PDF

PDF

PDF

IEICE technical report (RECONF), January 2015.

PPTX

Abstracts of FPGA2017 papers (Temporary Version)

PDF

SDSoC勉強会_170128_スライド「SDx 2016.3のプラグマによるハードウェアと性能」

PDF

Aws xilinx webinar20200729_ibex

PDF

Synthesijer.Scala (PROSYM 2015)

PDF

More from Kenichi Kurimoto

ZIP

Abc2012spring robot sammit - Kurimoto

ZIP

PDF

Blockchain - Future Sync Vol5 Slide

PDF

KEY

Earthquake visualization - ABC2012 Tohuku

PDF

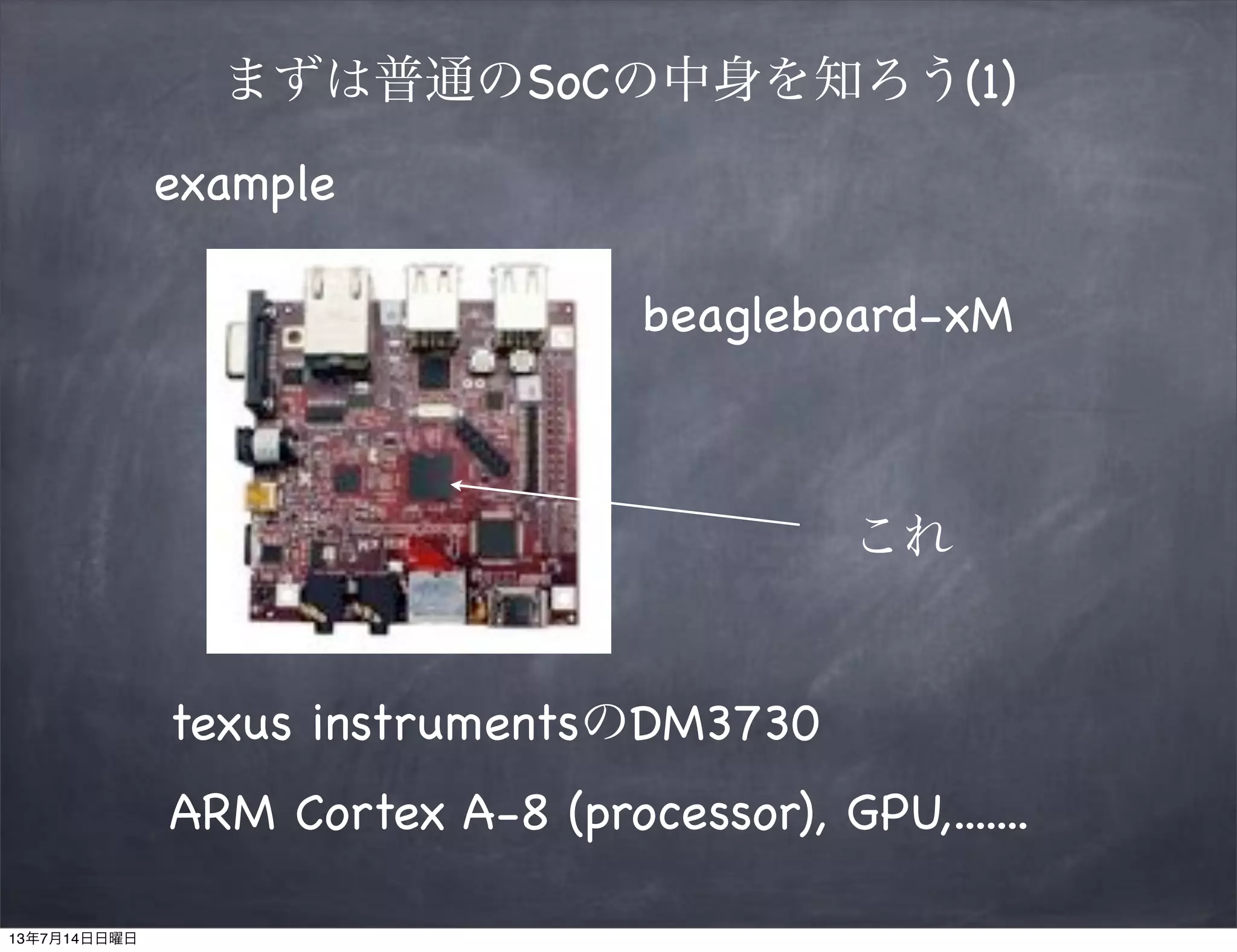

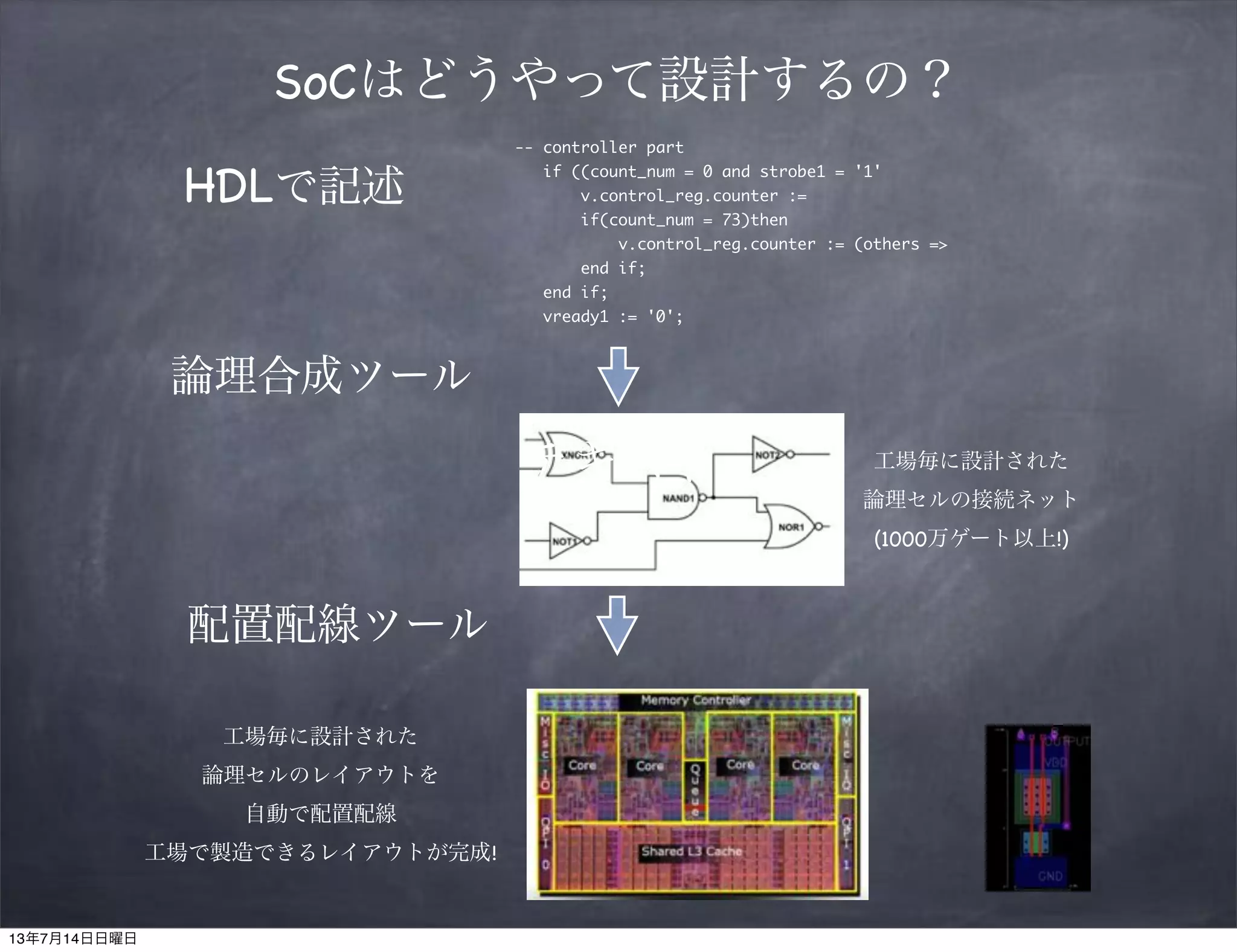

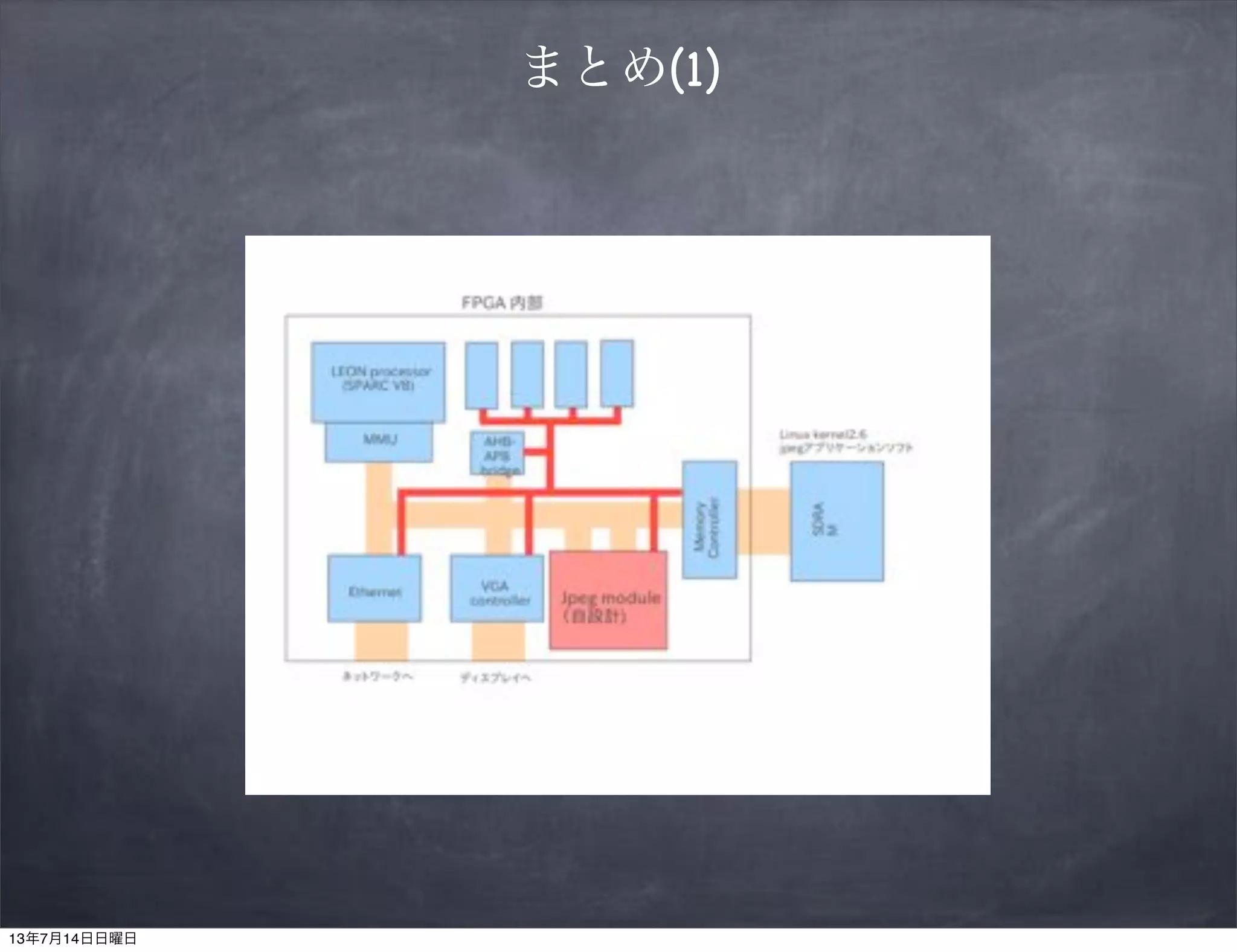

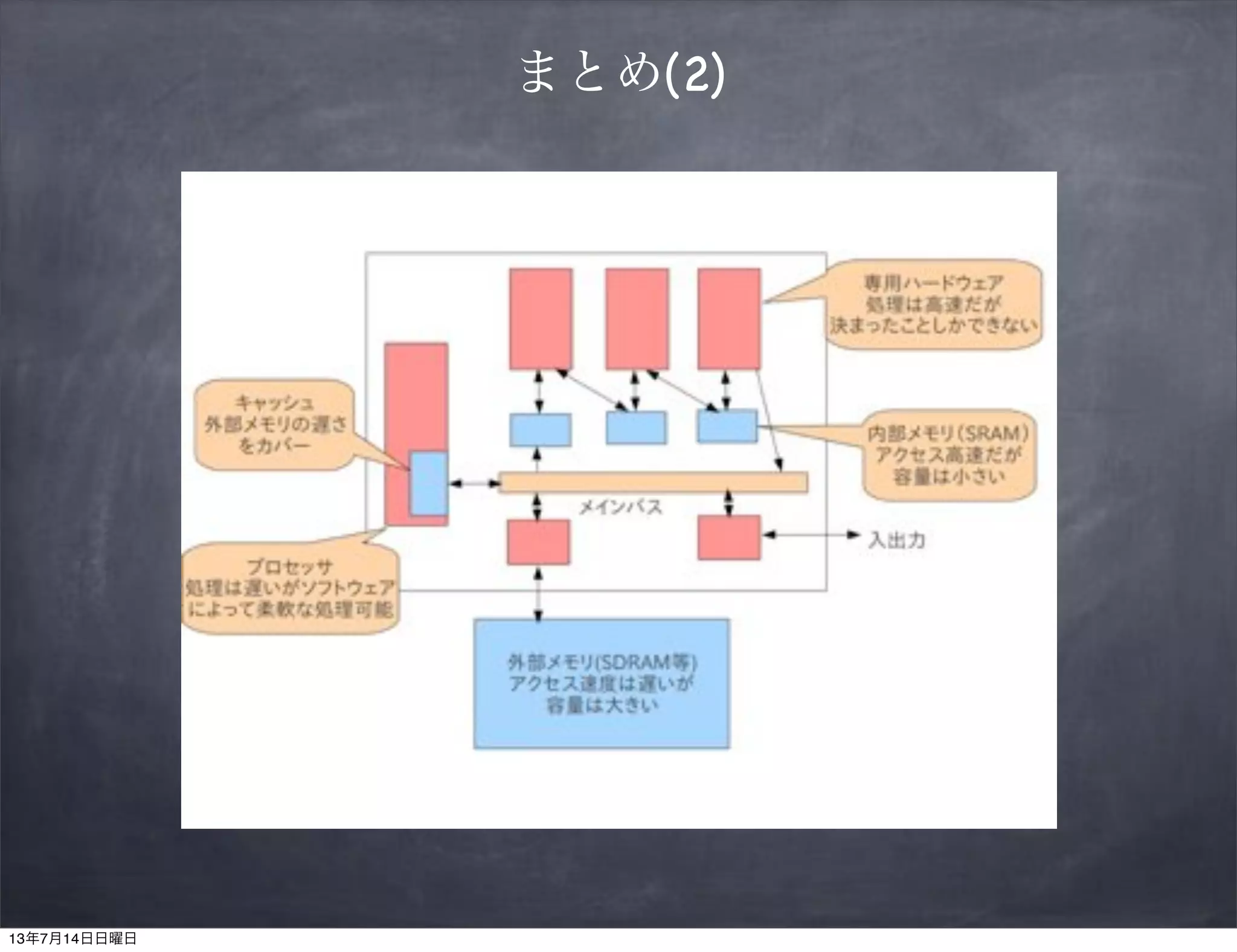

オープンハードセミナー 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. SoCはどうやって設計するの?

HDLで記述

-- controller part

if ((count_num = 0 and strobe1 = '1'

v.control_reg.counter :=

if(count_num = 73)then

v.control_reg.counter := (others =>

end if;

end if;

vready1 := '0';

論理合成ツール

テキスト 工場毎に設計された

論理セルの接続ネット

(1000万ゲート以上!)

配置配線ツール

工場毎に設計された

論理セルのレイアウトを

自動で配置配線

工場で製造できるレイアウトが完成!

13年7月14日日曜日

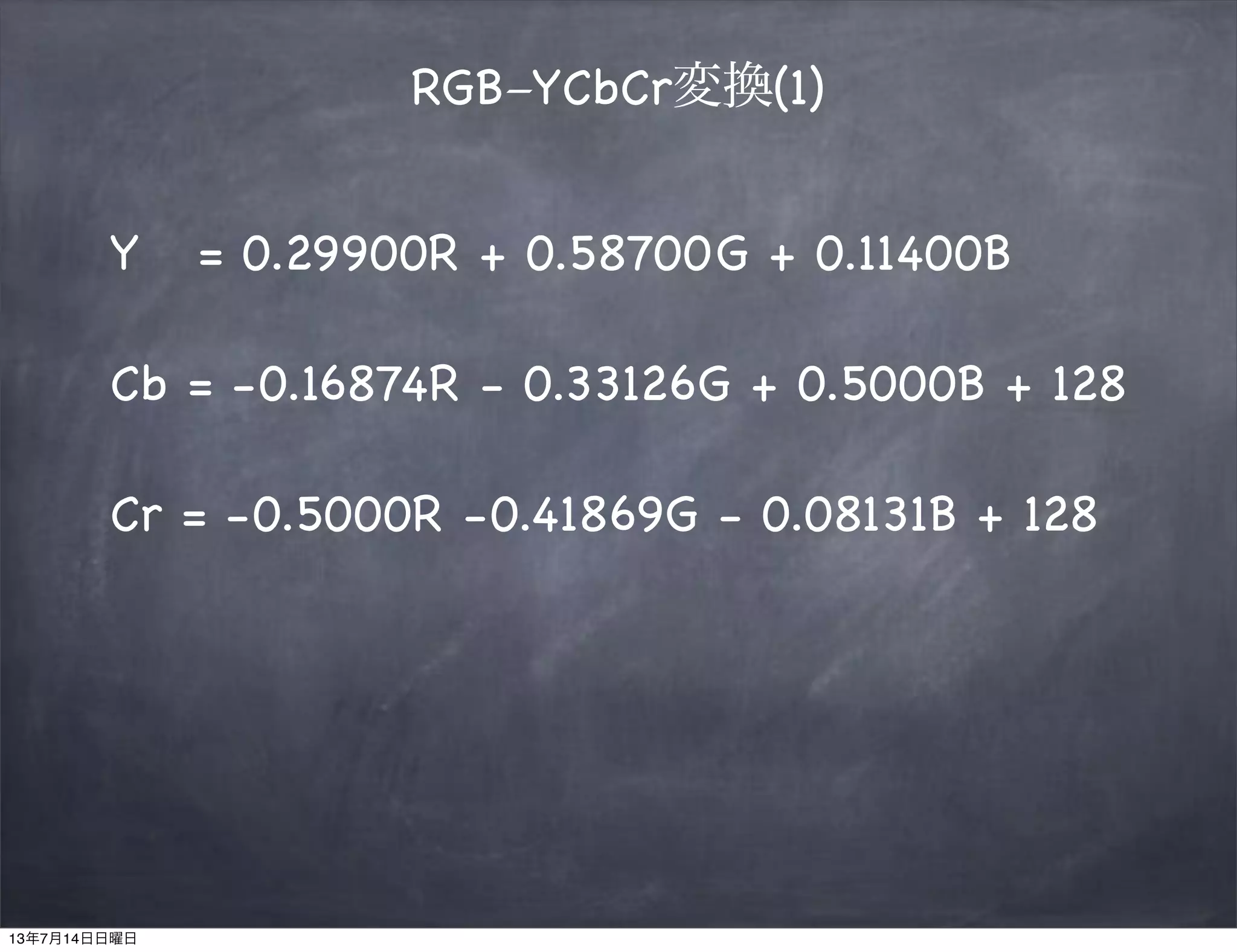

13. 14. 15. 16. 17. 18. RGB−YCbCr変換(1)

Y = 0.29900R + 0.58700G + 0.11400B

Cb = -0.16874R - 0.33126G + 0.5000B + 128

Cr = -0.5000R -0.41869G - 0.08131B + 128

13年7月14日日曜日

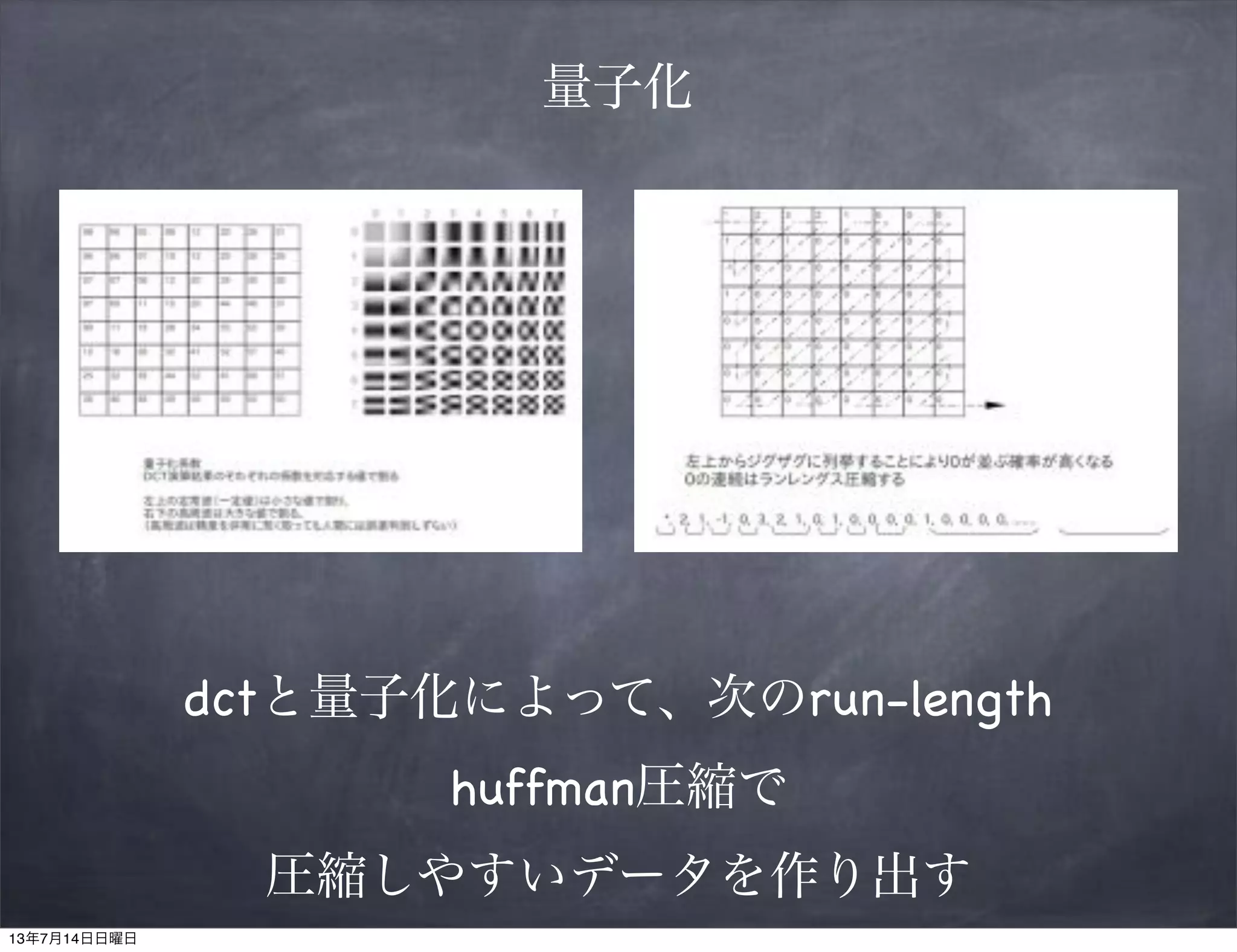

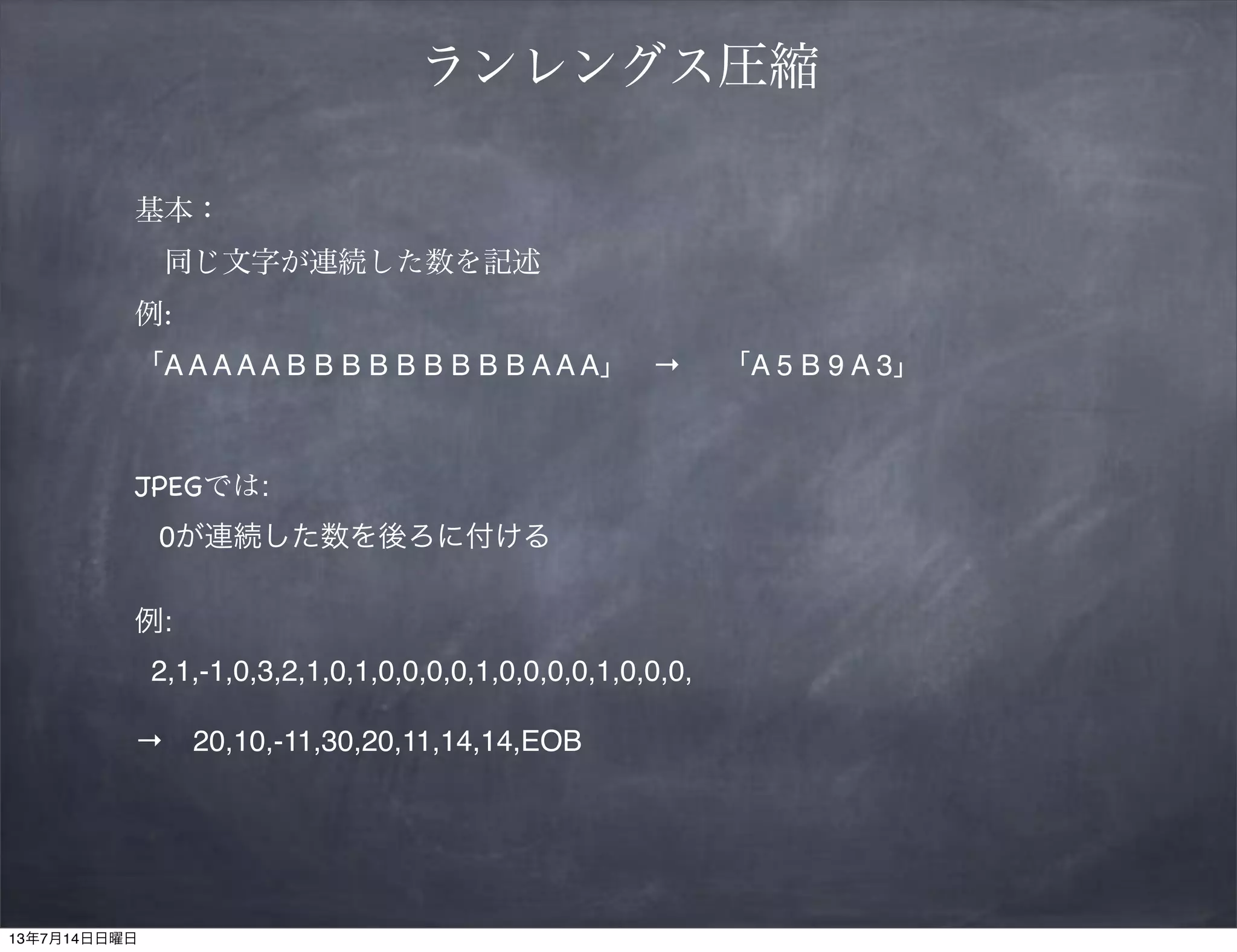

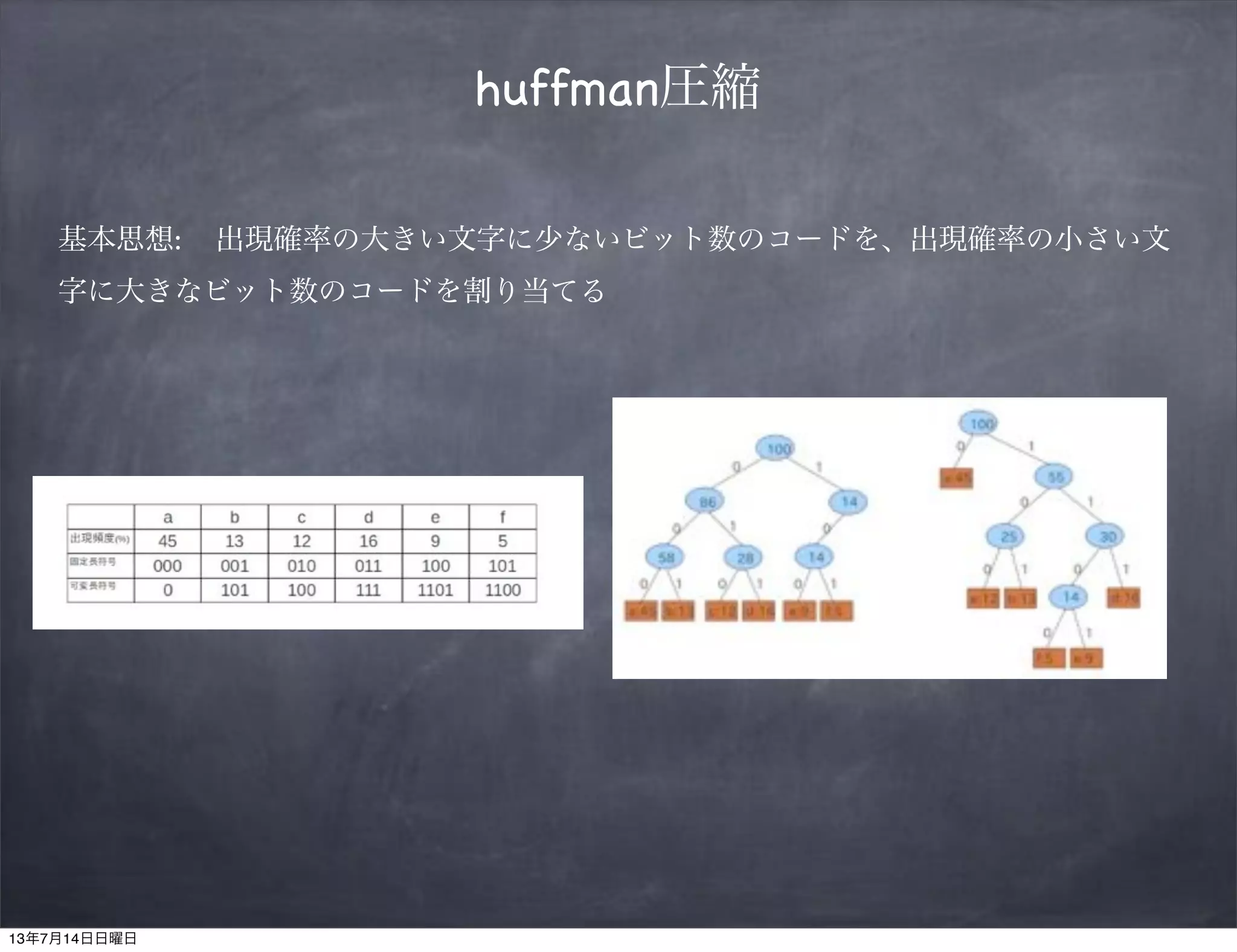

19. 20. 21. 22. 23. ランレングス圧縮

基本:

同じ文字が連続した数を記述

例:

「A A A A A B B B B B B B B B A A A」 → 「A 5 B 9 A 3」

JPEGでは:

0が連続した数を後ろに付ける

例:

2,1,-1,0,3,2,1,0,1,0,0,0,0,1,0,0,0,0,1,0,0,0,

→ 20,10,-11,30,20,11,14,14,EOB

13年7月14日日曜日

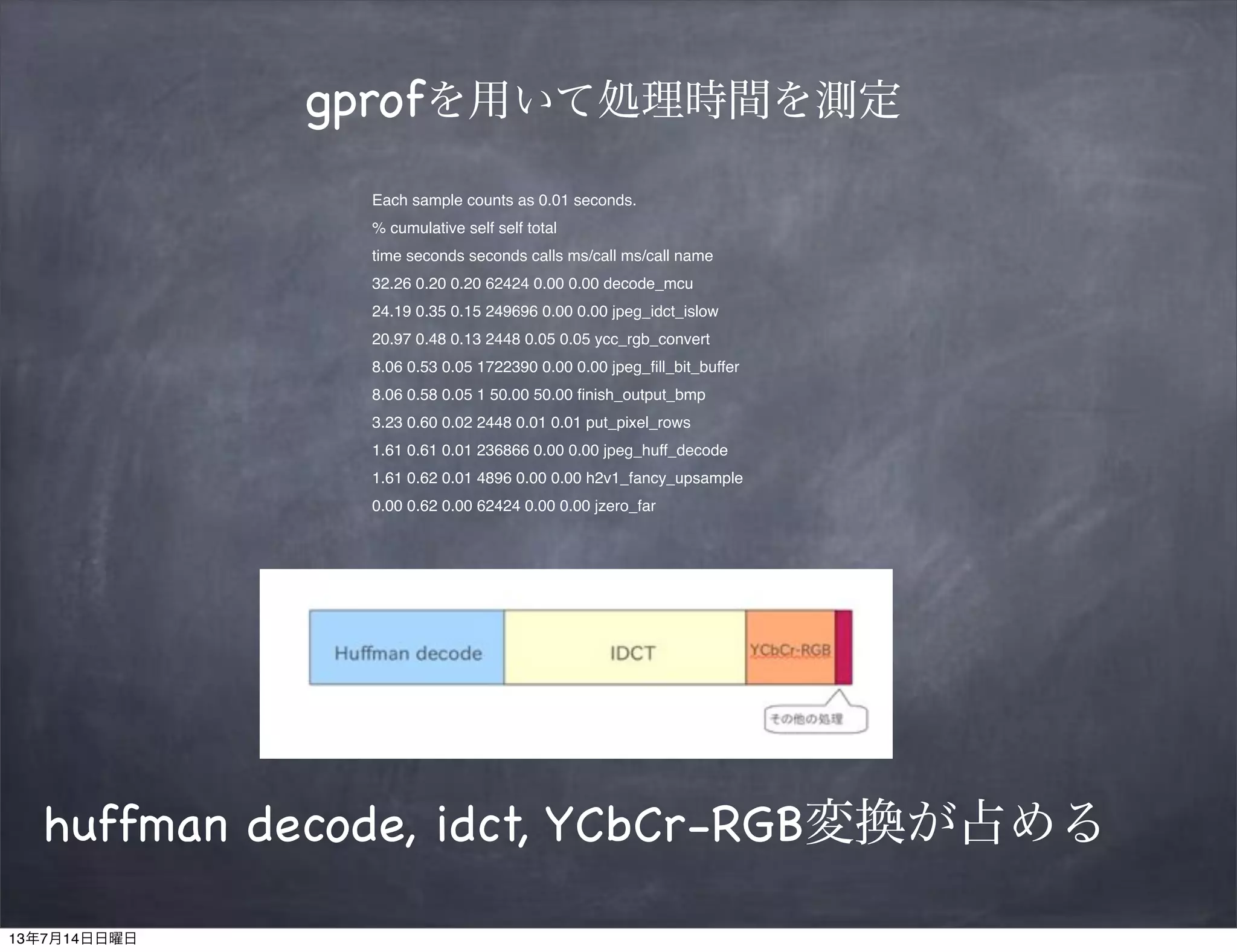

24. 25. 26. 27. 28. 29. 30. 31. 32. 33. 34. 35. 36. 37. 38. gprofを用いて処理時間を測定

Each sample counts as 0.01 seconds.

% cumulative self self total

time seconds seconds calls ms/call ms/call name

32.26 0.20 0.20 62424 0.00 0.00 decode_mcu

24.19 0.35 0.15 249696 0.00 0.00 jpeg_idct_islow

20.97 0.48 0.13 2448 0.05 0.05 ycc_rgb_convert

8.06 0.53 0.05 1722390 0.00 0.00 jpeg_fill_bit_buffer

8.06 0.58 0.05 1 50.00 50.00 finish_output_bmp

3.23 0.60 0.02 2448 0.01 0.01 put_pixel_rows

1.61 0.61 0.01 236866 0.00 0.00 jpeg_huff_decode

1.61 0.62 0.01 4896 0.00 0.00 h2v1_fancy_upsample

0.00 0.62 0.00 62424 0.00 0.00 jzero_far

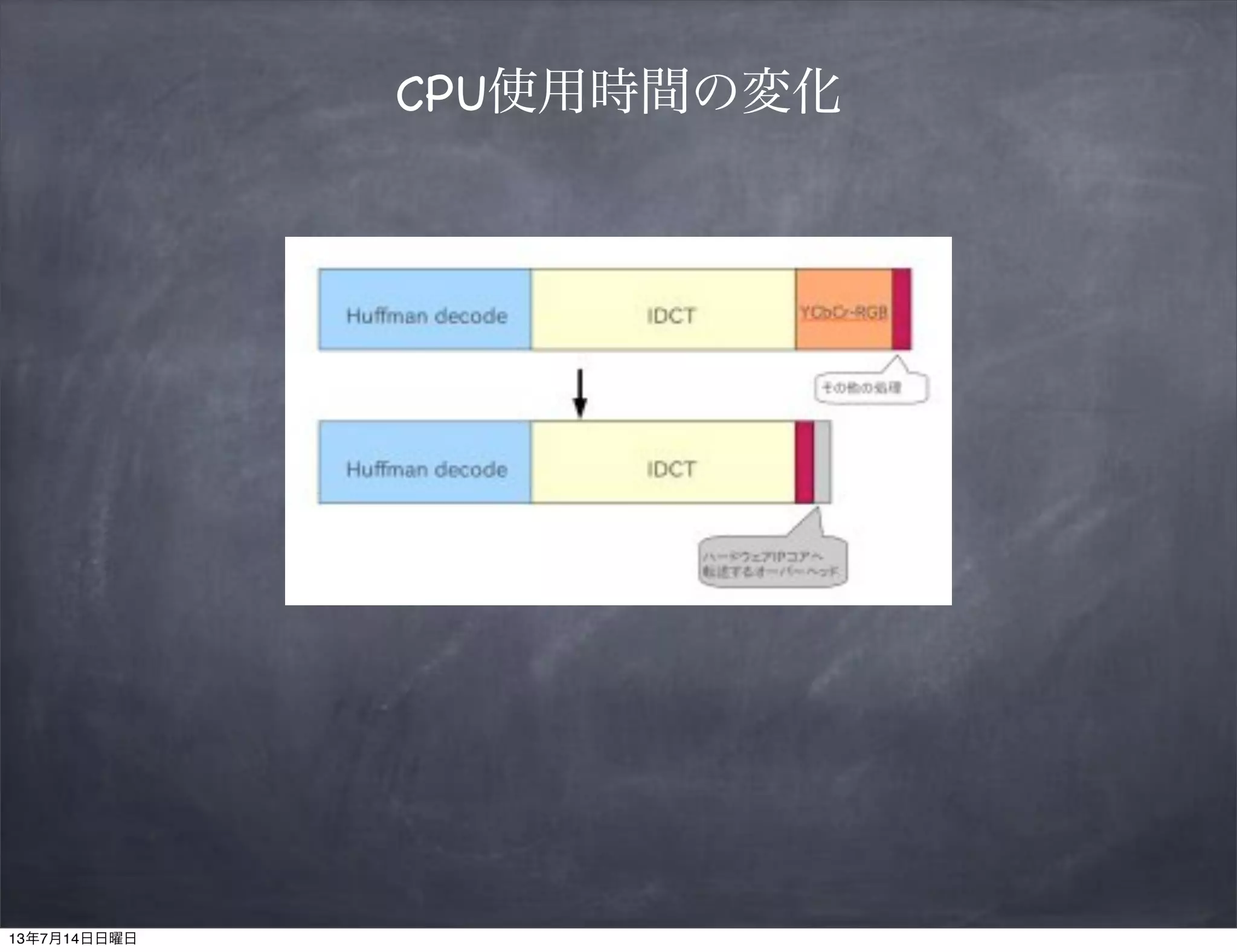

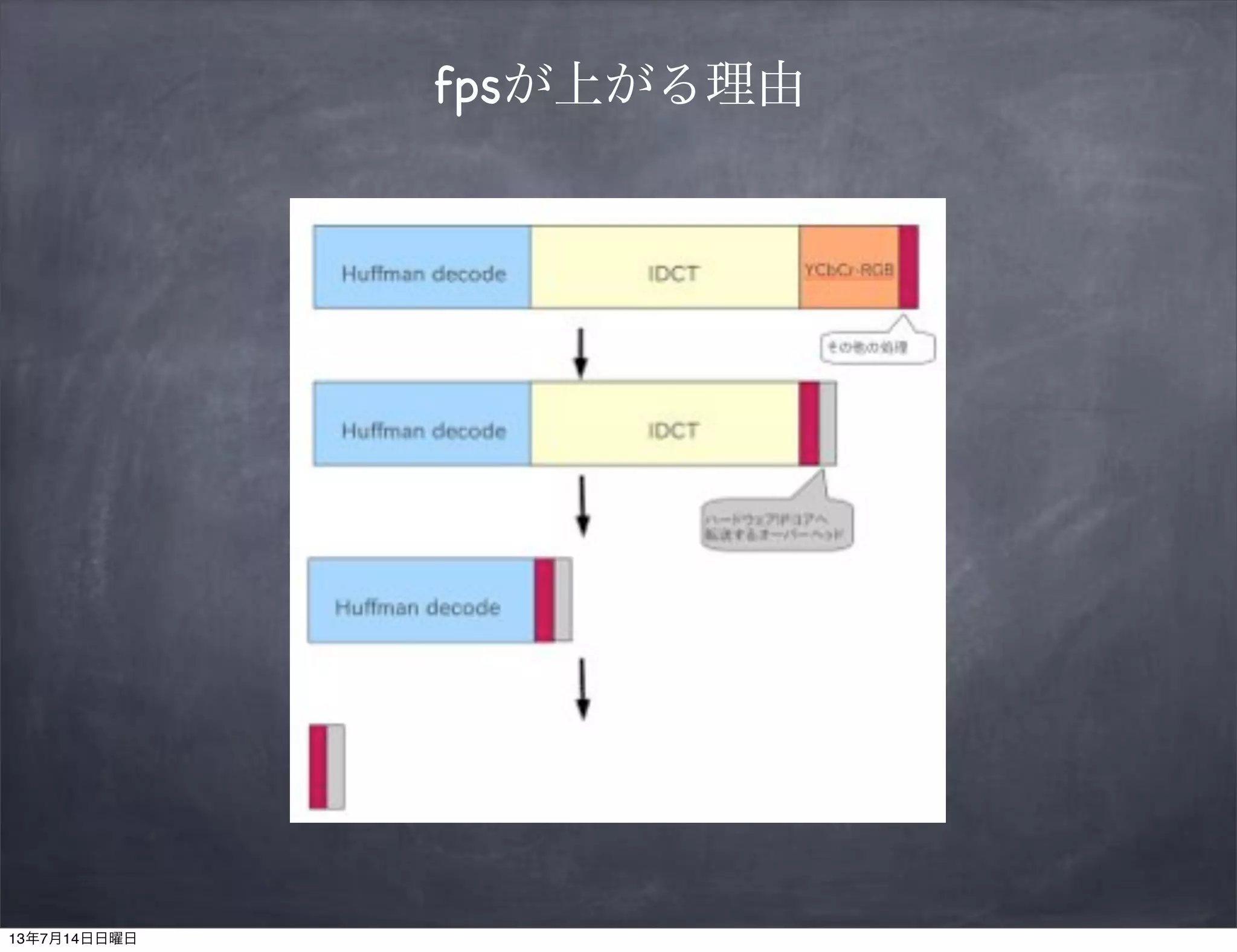

huffman decode, idct, YCbCr-RGB変換が占める

13年7月14日日曜日

39. 40. 41. 42. 43. 44. 45. 46. 47. 48. 49. 50. 51. 52. 53. 54. 55. 56. 57. 58. 59. 60. 61. 62. 63. 64. 65. 66.