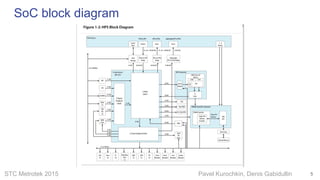

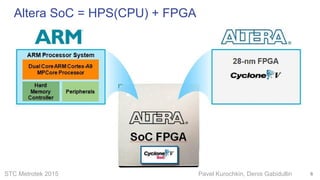

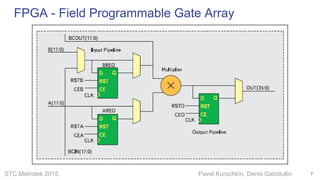

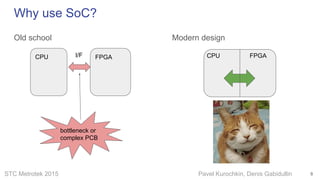

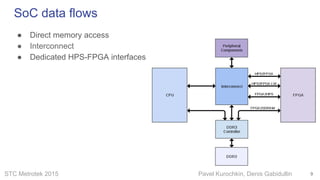

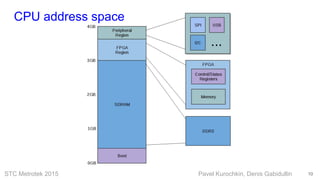

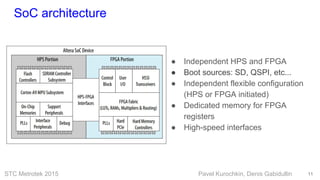

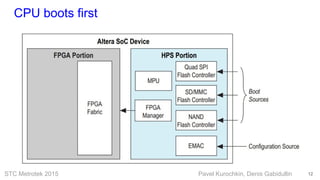

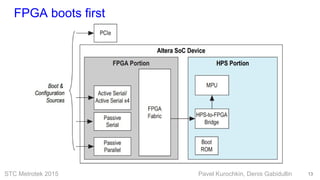

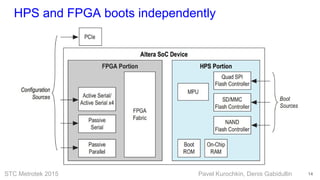

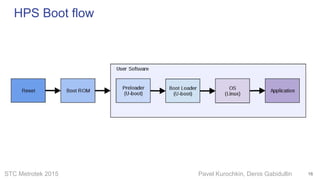

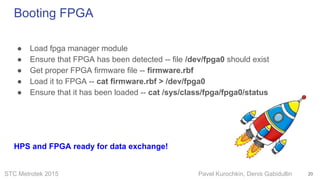

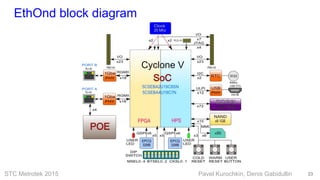

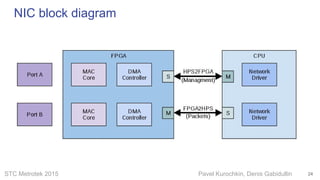

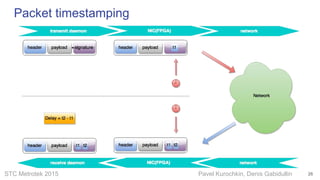

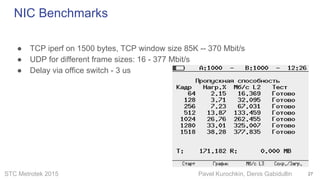

The document presents an overview of Linux-powered System-on-Chip (SoC) devices, detailing the architecture of Altera Cyclone V and the booting process of Linux on these devices. It highlights the development of NIC features, benchmarks, and various practical examples, including issues and challenges faced. Key advantages of using SoCs are discussed, alongside potential drawbacks such as limited driver support and thermal concerns.