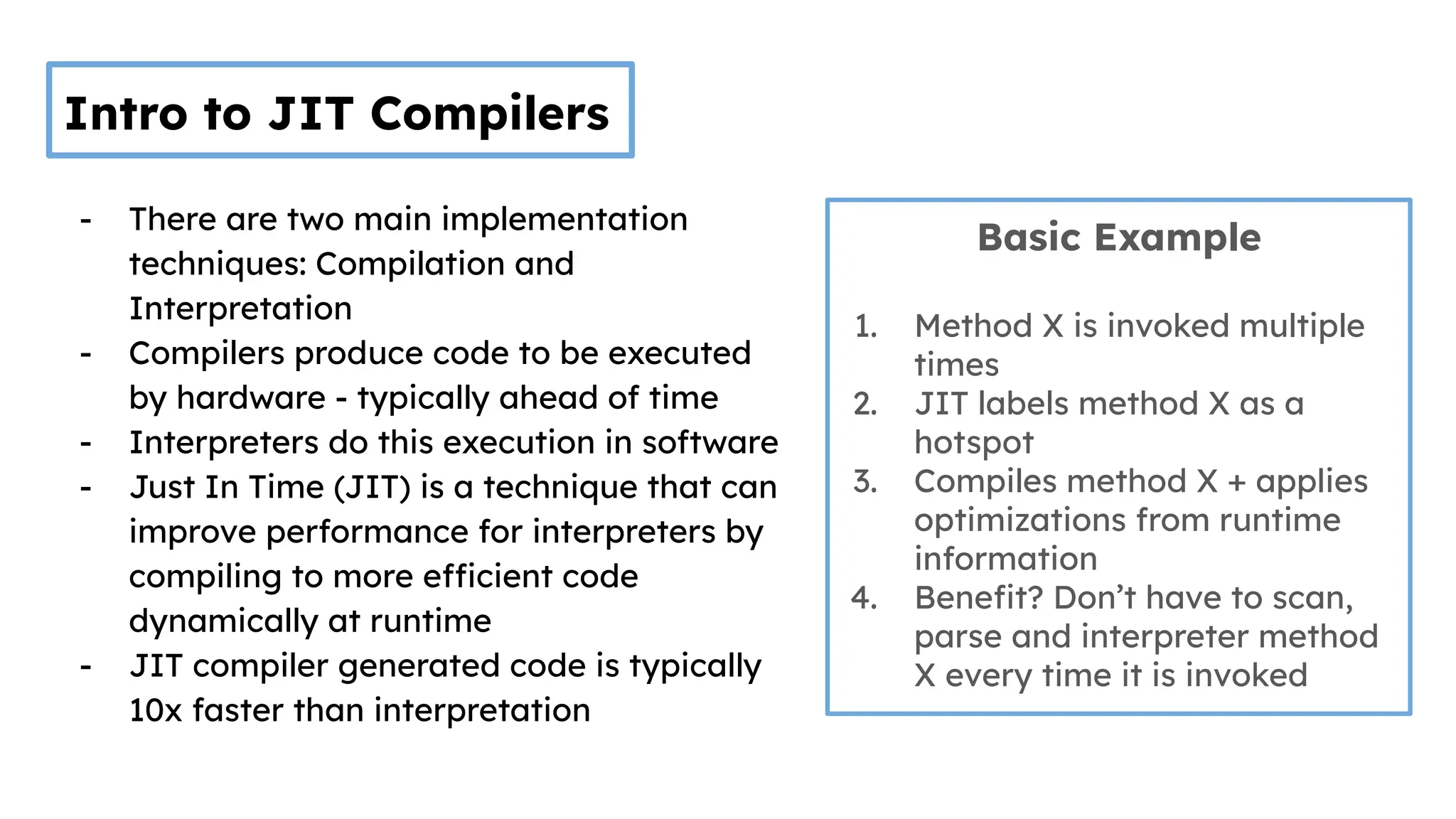

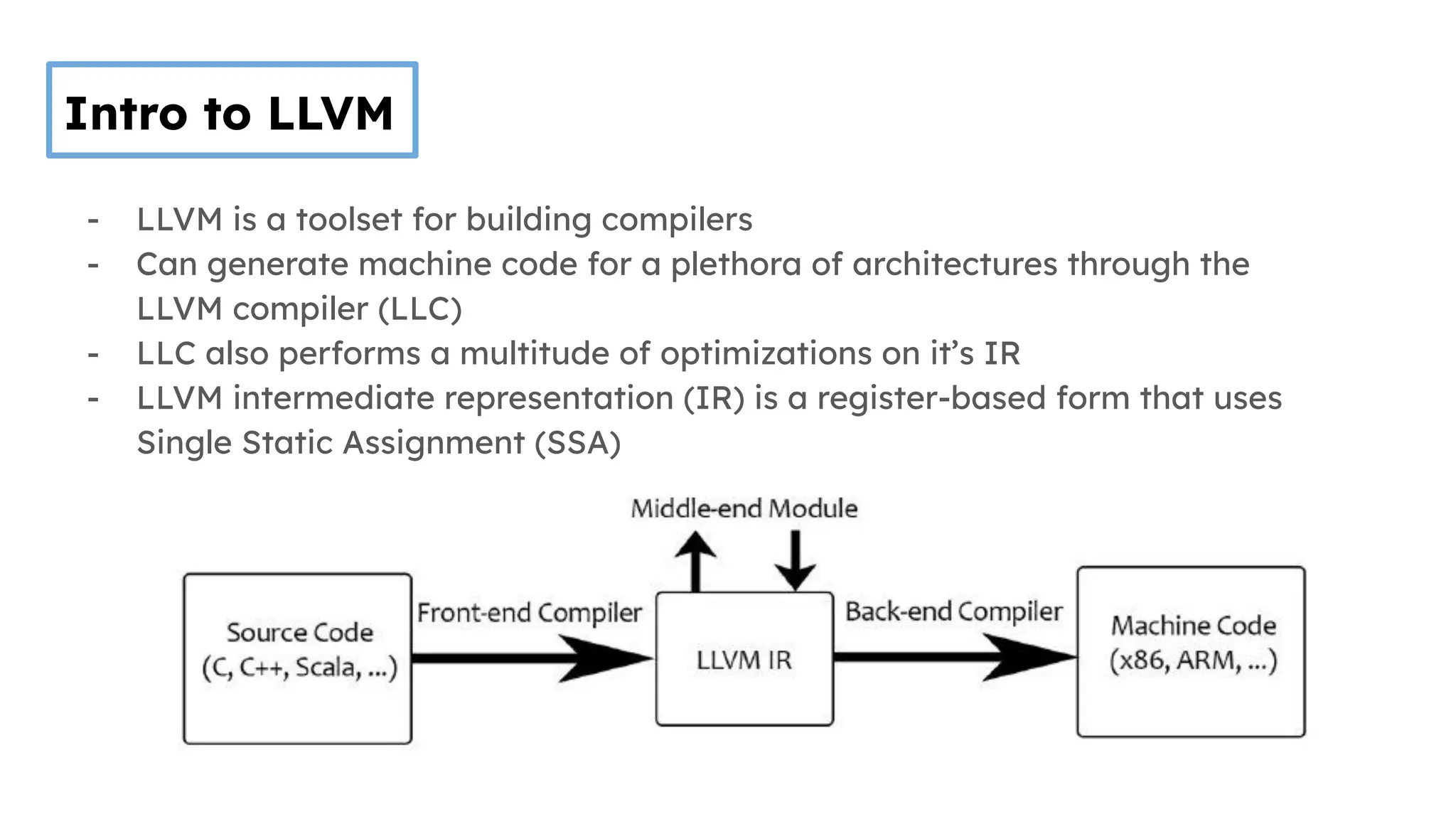

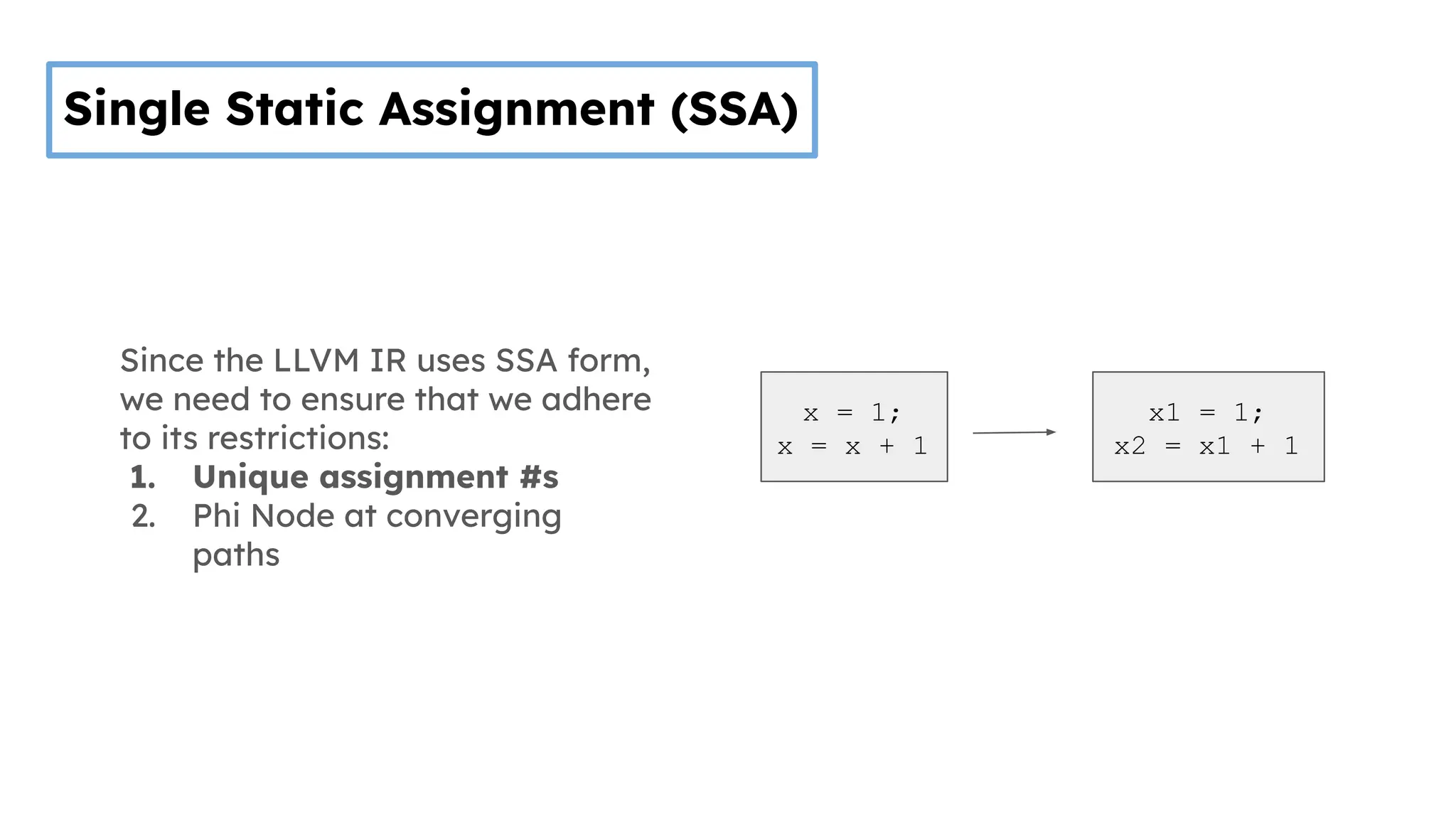

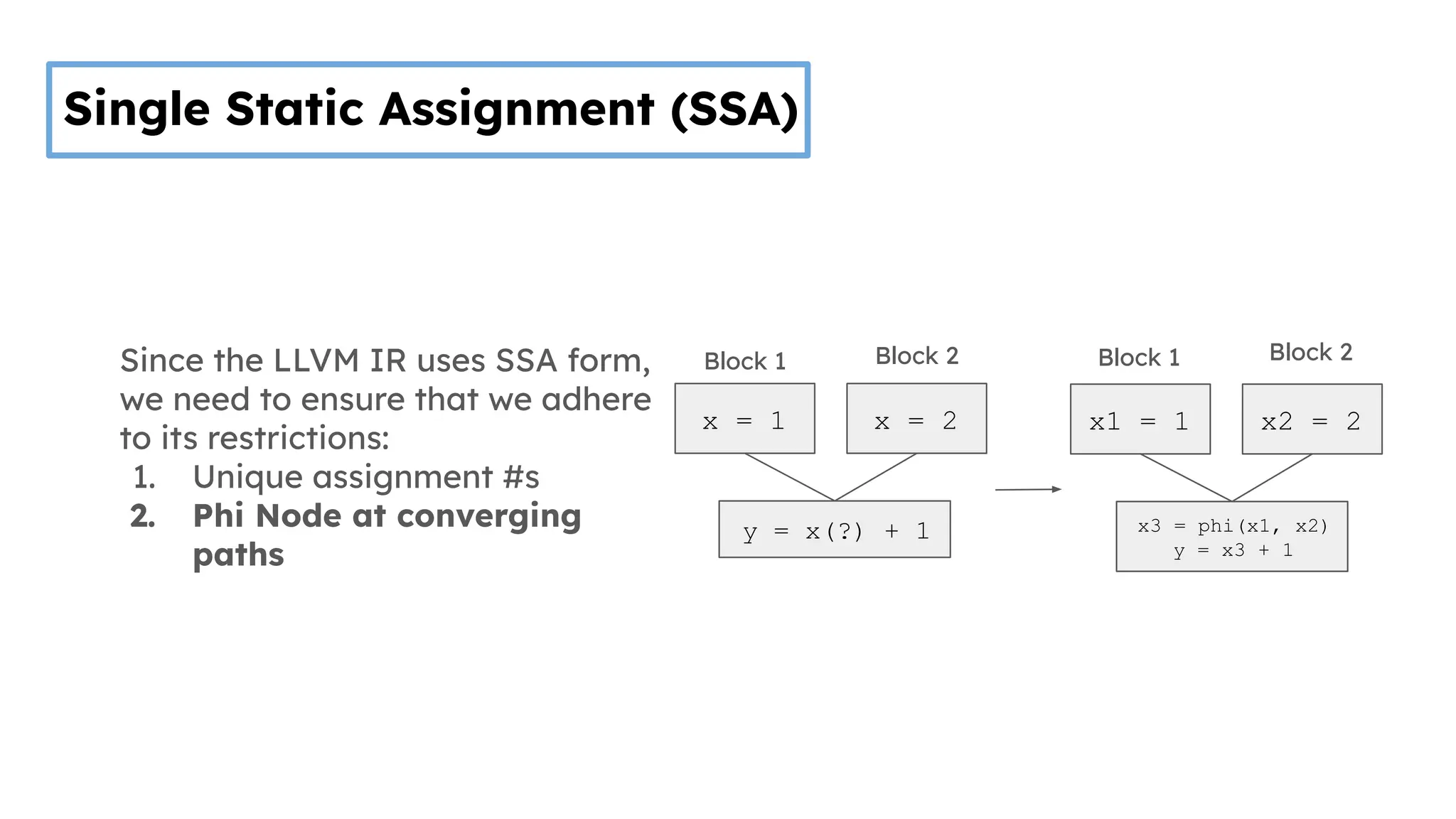

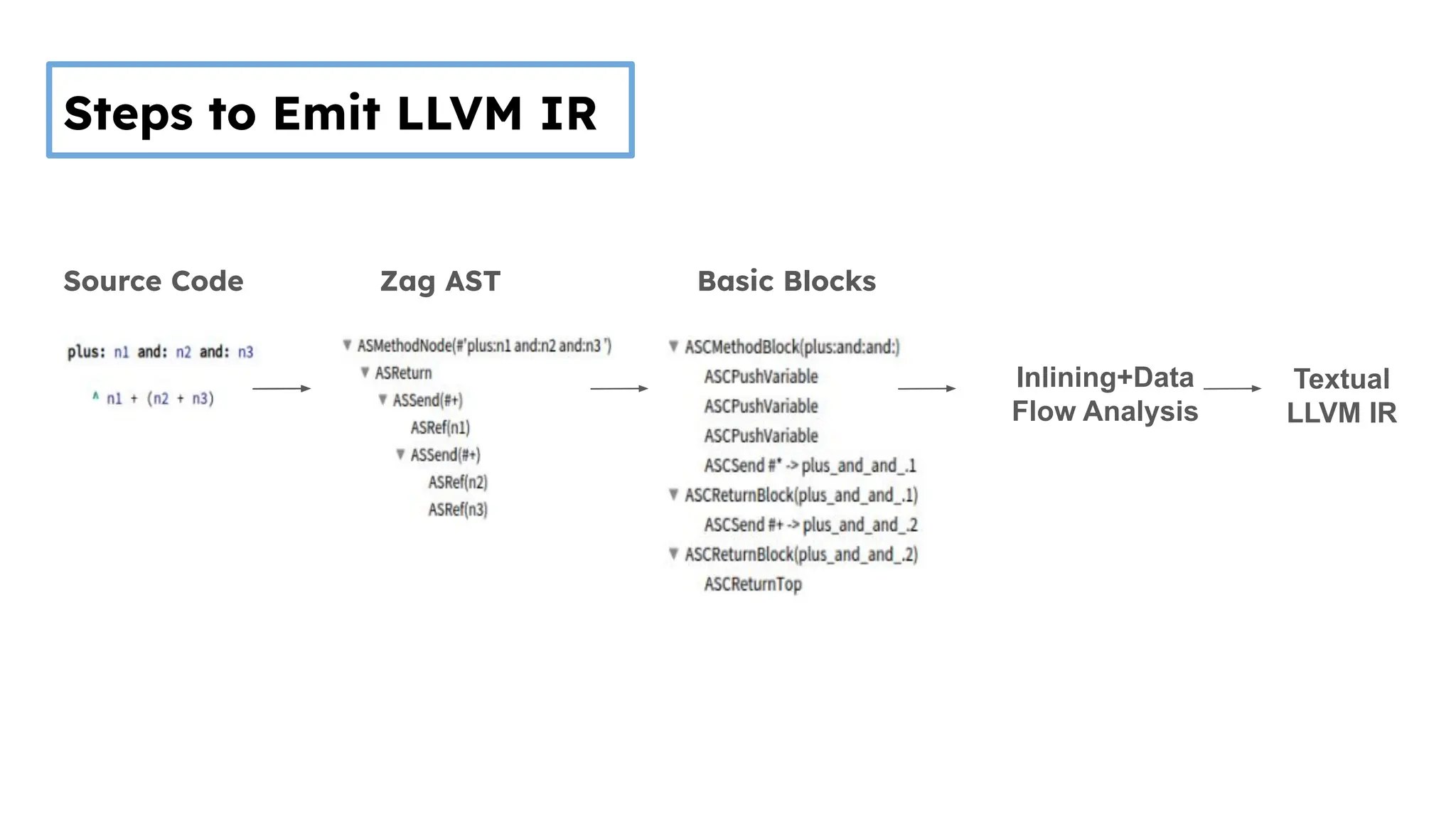

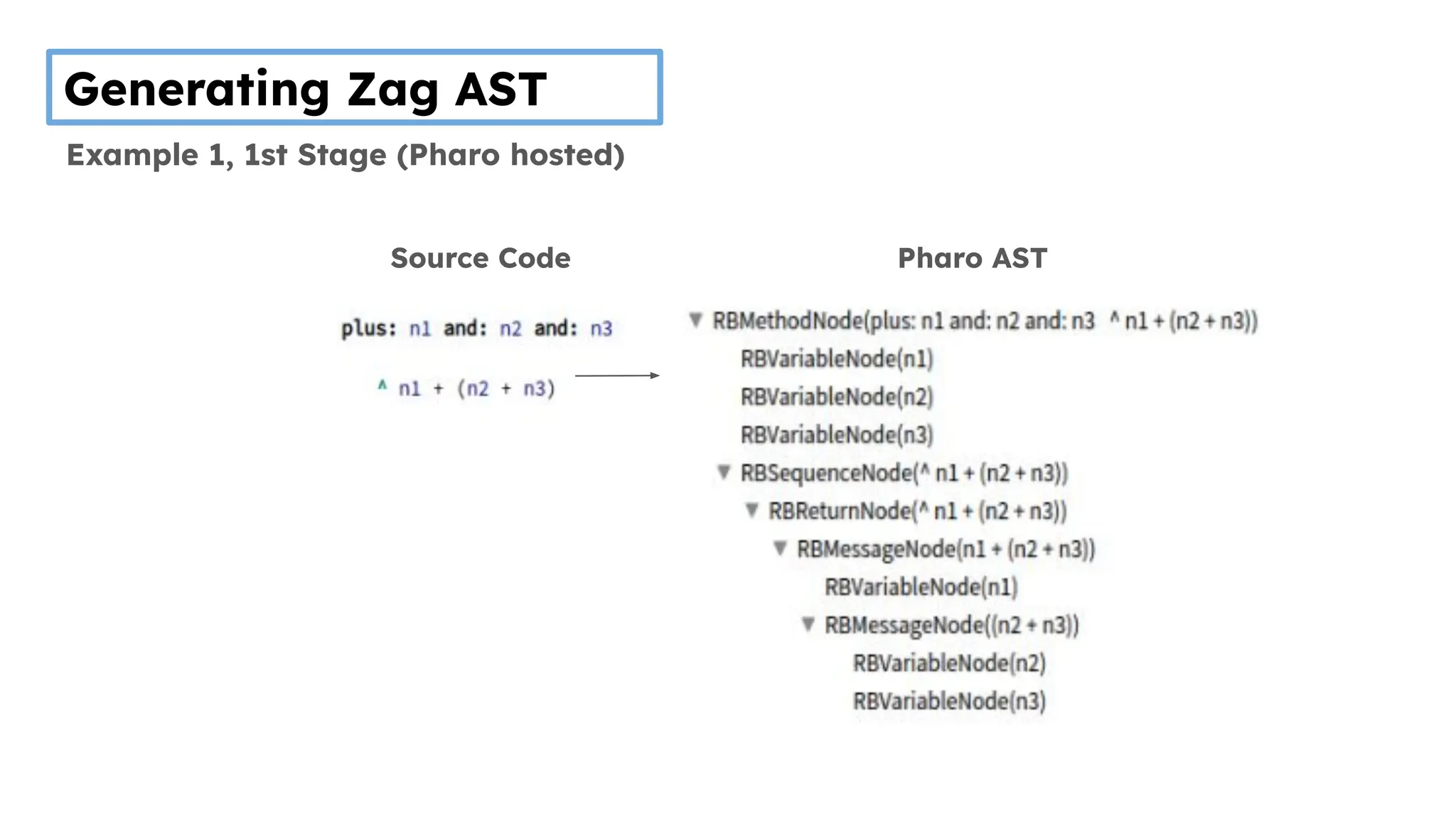

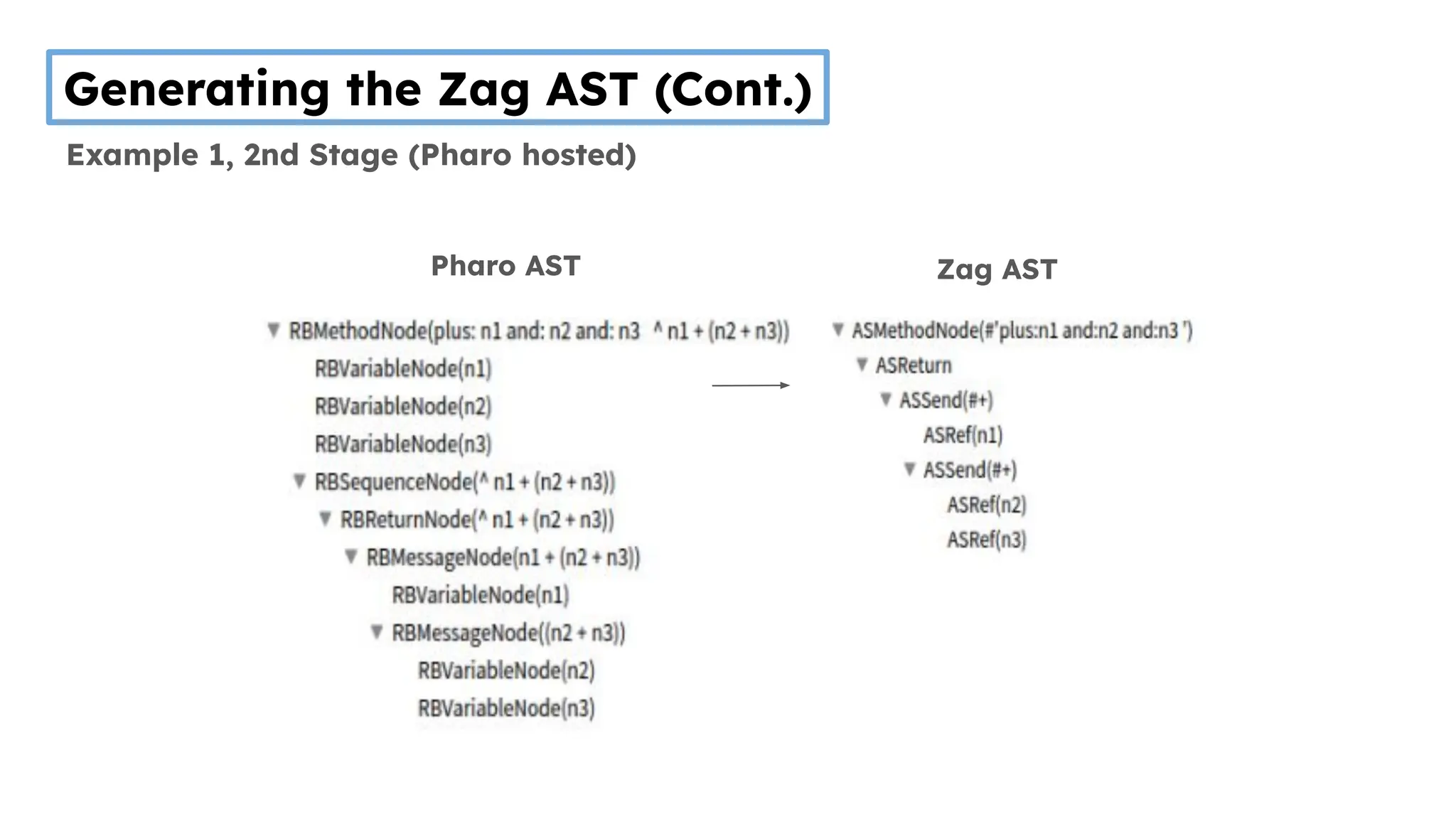

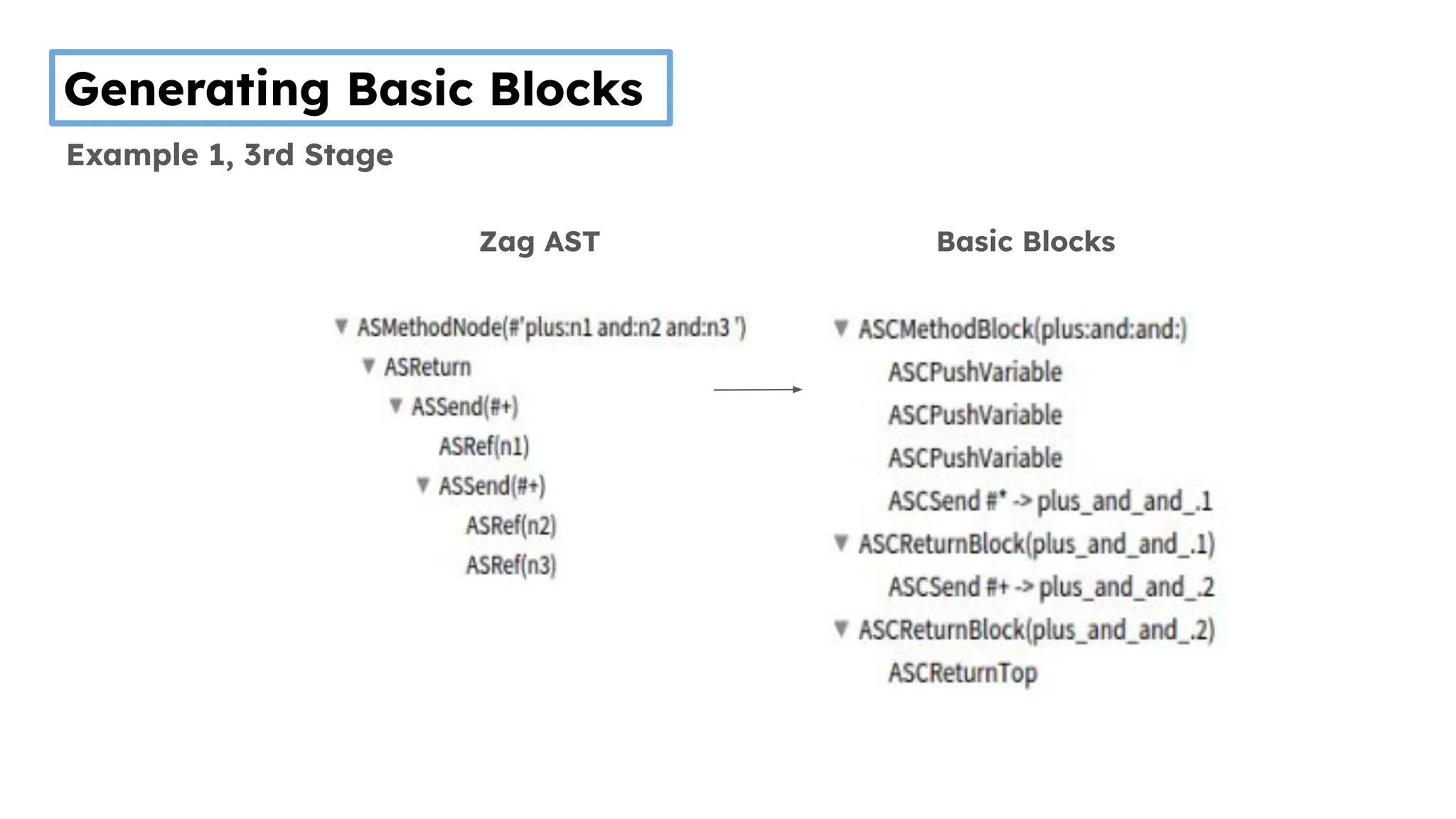

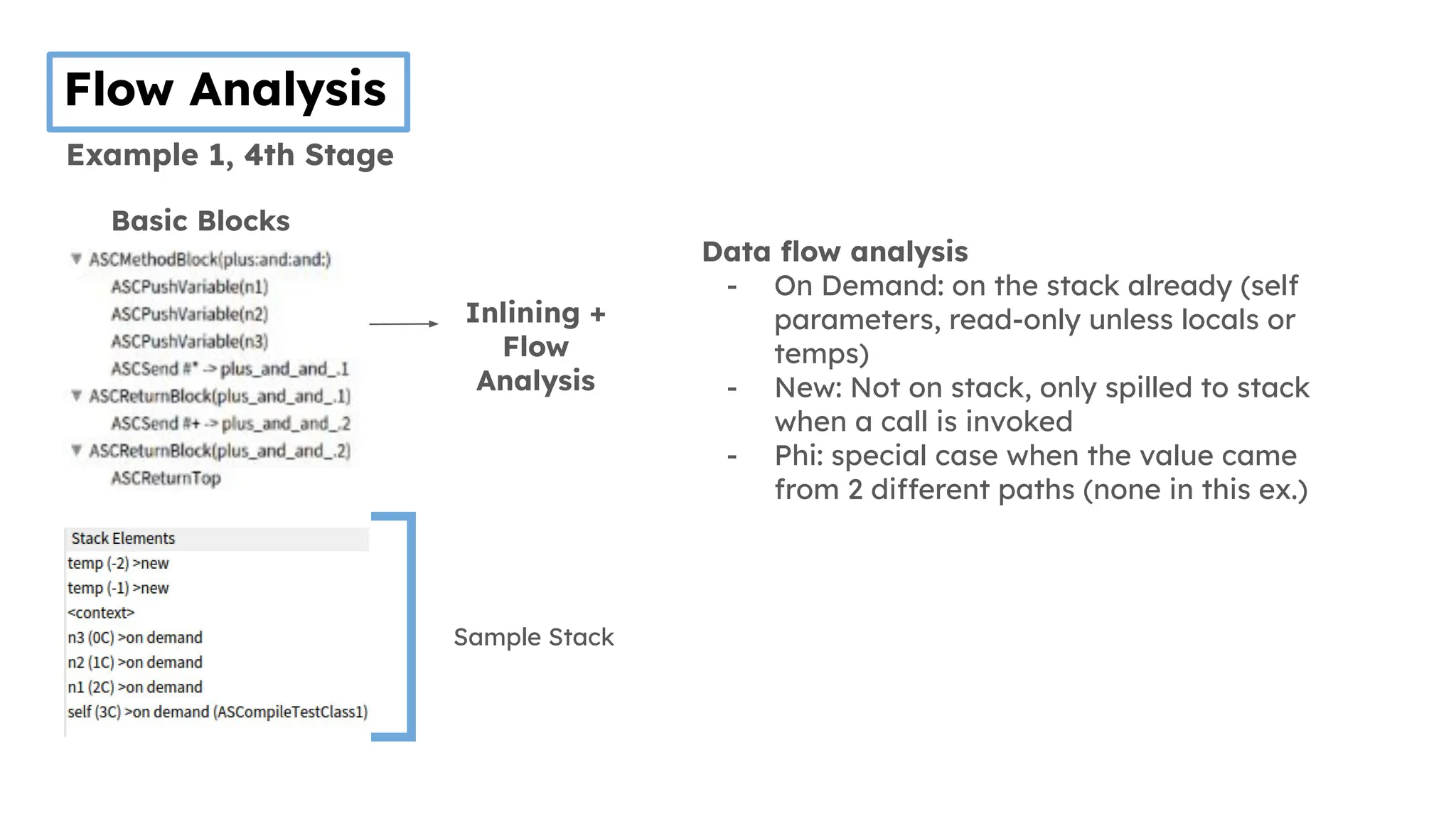

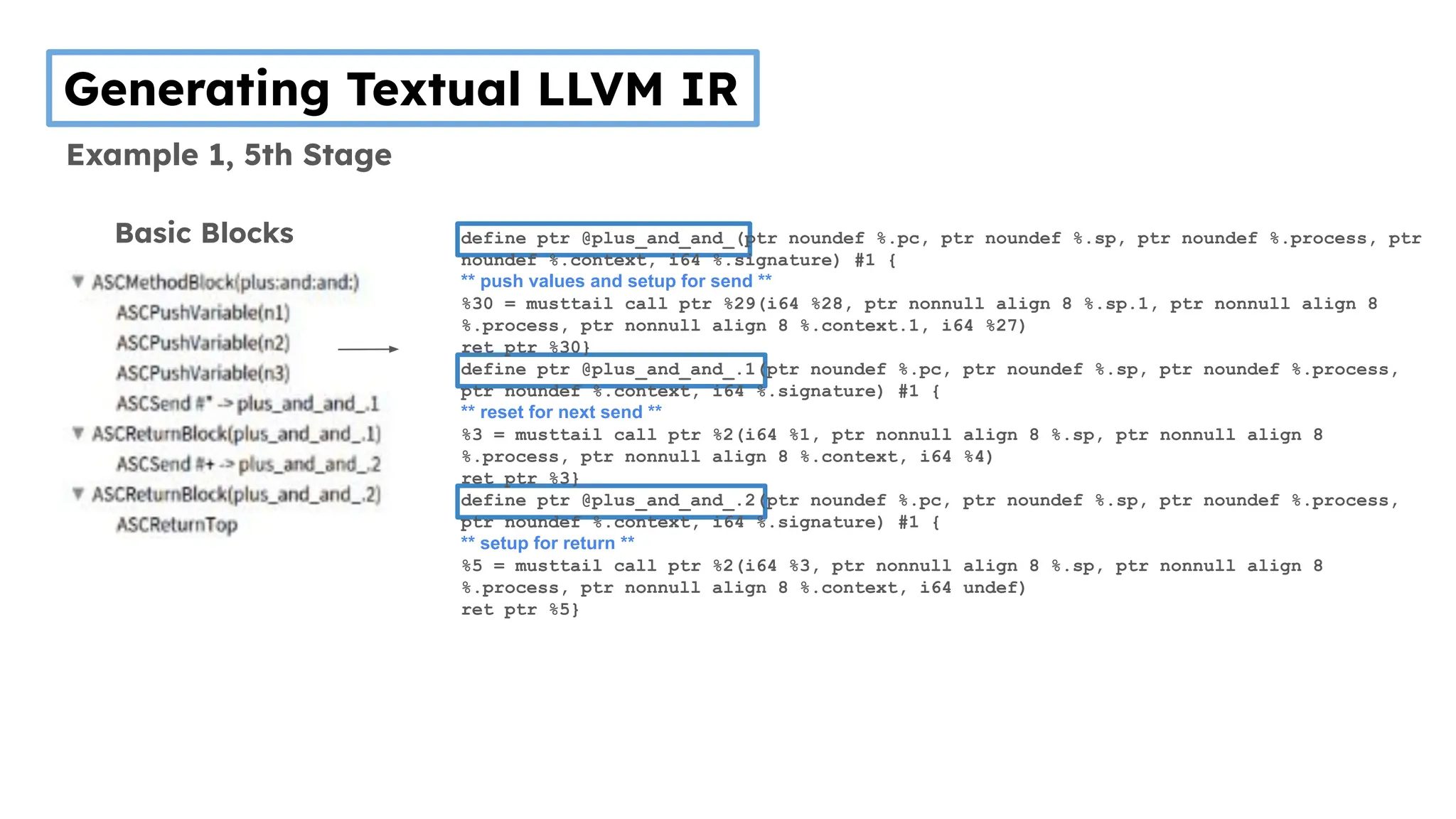

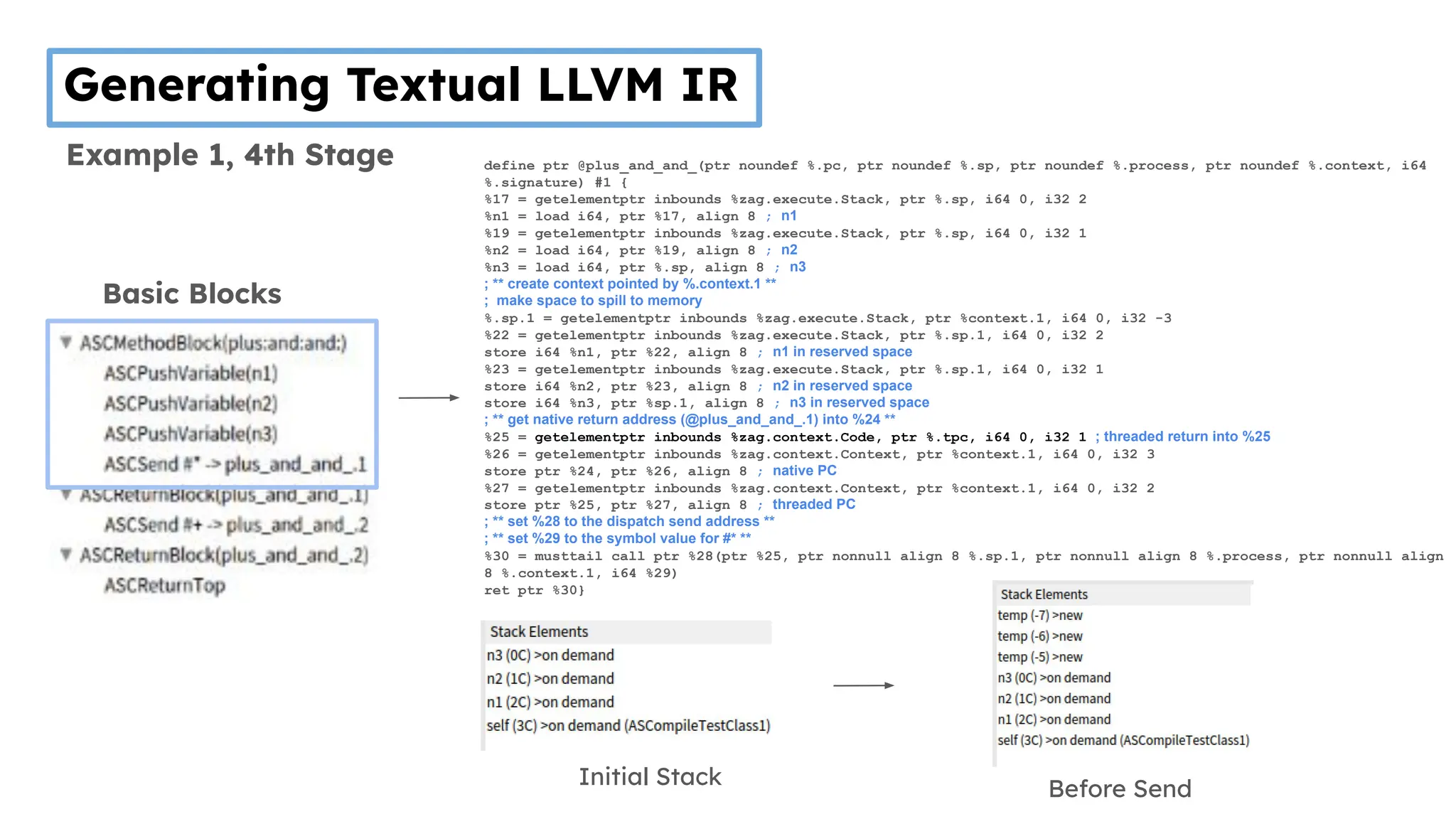

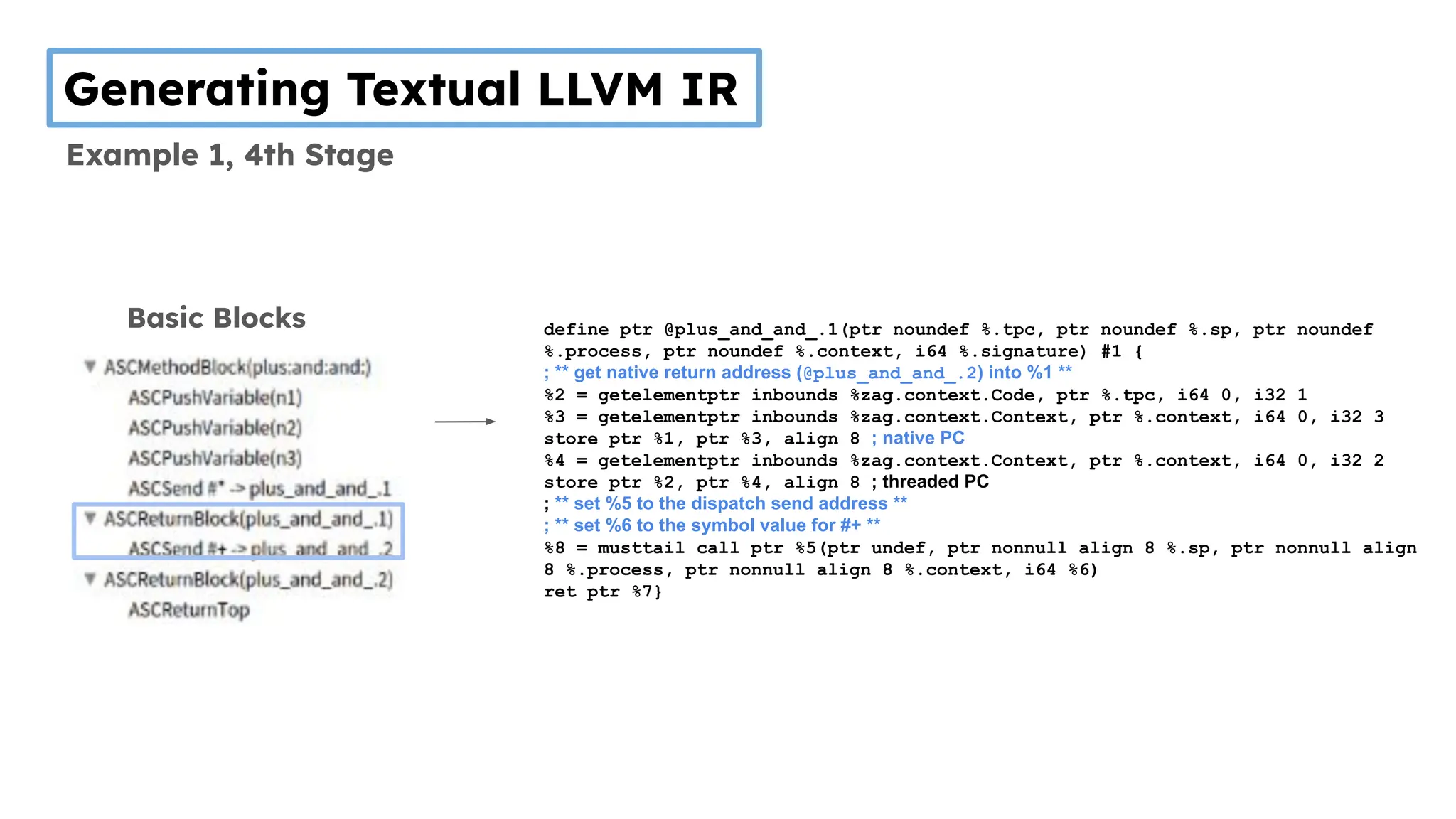

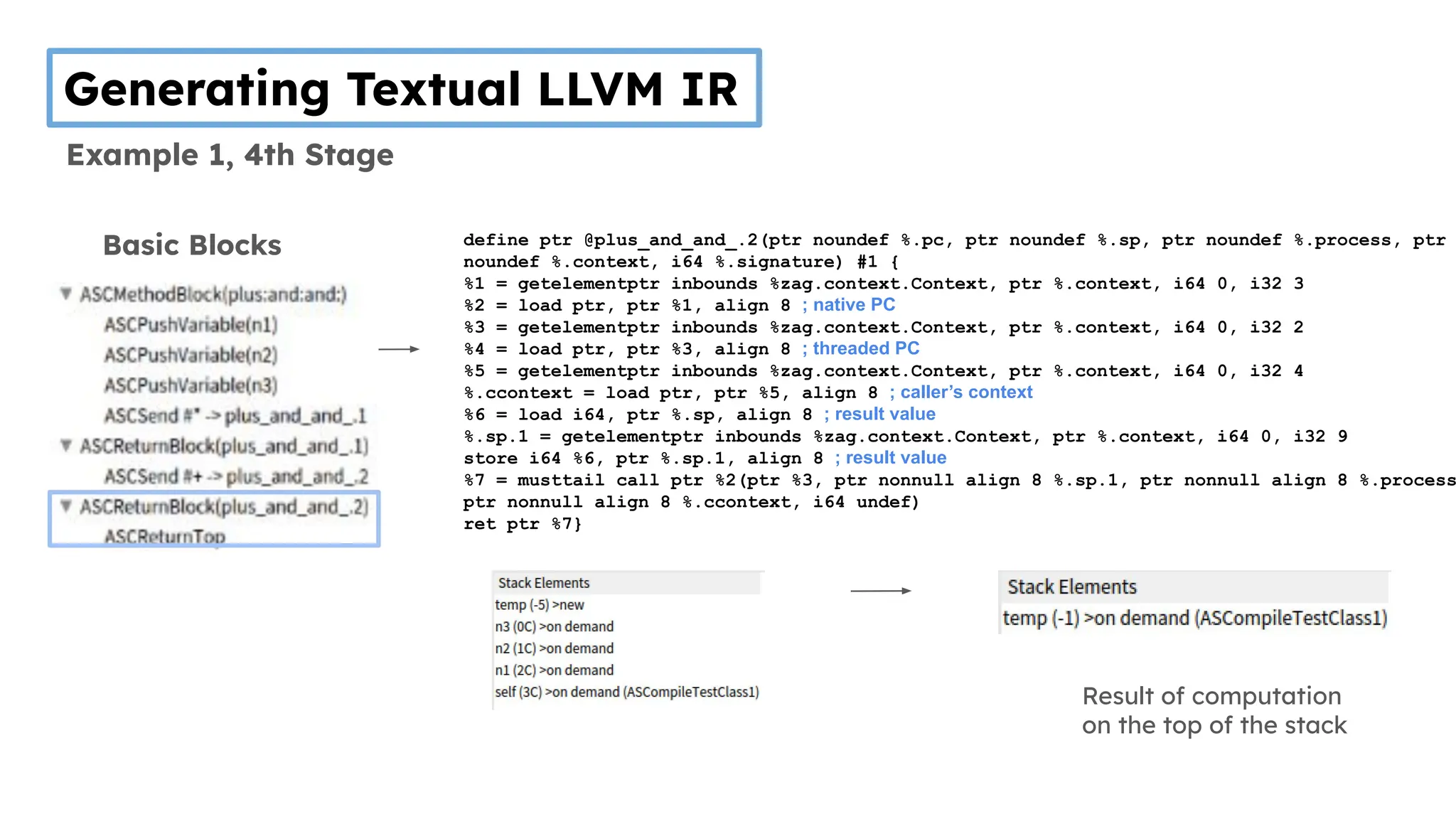

The document discusses the features and benefits of Just-In-Time (JIT) compilation and LLVM, a toolset for building compilers. It explains how JIT improves performance by compiling methods dynamically at runtime and outlines the structure of LLVM's intermediate representation (IR) using Single Static Assignment (SSA). Additionally, it covers the process of generating textual LLVM IR and the various stages involved in emitting it, including flow analysis and example code snippets.