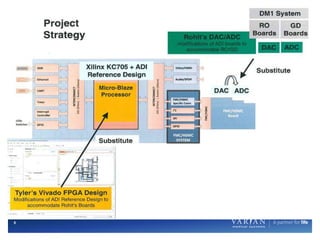

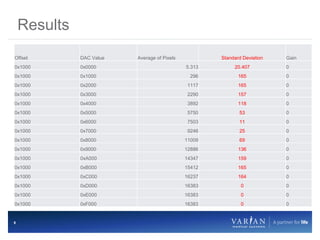

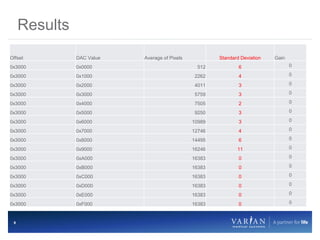

The document summarizes Rohit L. Gawali's MS project on testing Plexiglas using a Legos Full Contact Tester. The project aimed to (1) test the tester board electronics without a glass sample, (2) reduce noise to increase image quality, and (3) control signals sent to pixels to display test images. Gawali designed new tester hardware interfacing with a Kintex FPGA board to send controlled signals at different offsets and gains, obtaining pixel value results. Through this project, Gawali learned skills in FPGA and CPLD design, flat panel testing, and coordinating with a team.