Embed presentation

Download to read offline

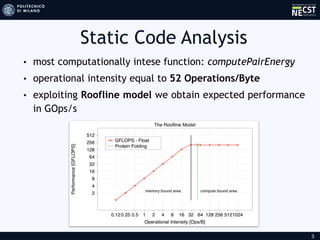

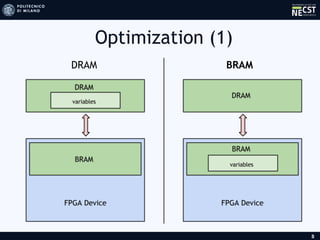

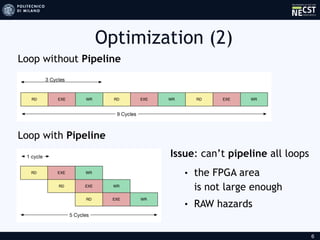

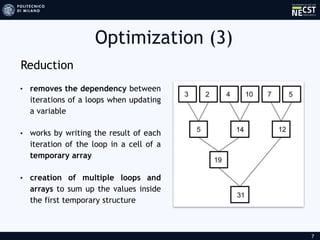

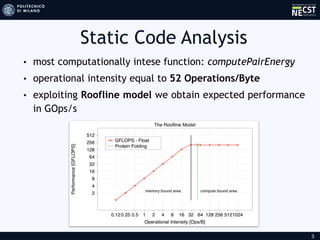

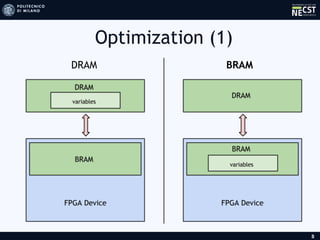

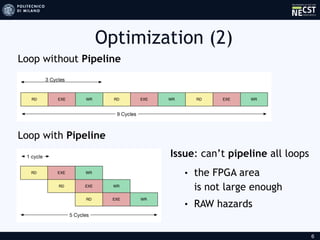

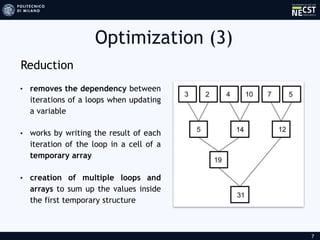

This document discusses hardware acceleration through profiling code to find bottlenecks, implementing the bottleneck function in hardware using Vivado HLS, and optimizing the implementation through loop pipelining, reduction, and memory access. The most computationally intensive function was found to be computePairEnergy. Hardware implementation and optimizations allowed for exploiting the Roofline model to achieve expected performance gains in implementing the bottleneck function in hardware.