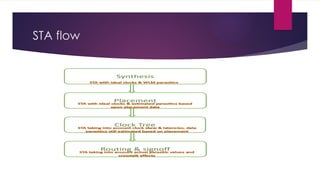

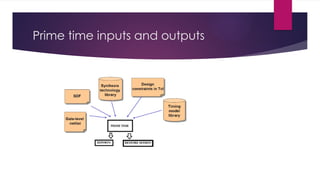

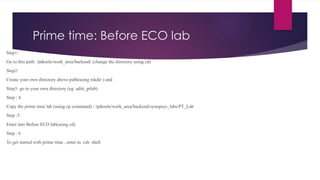

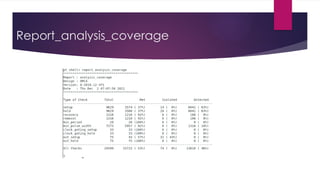

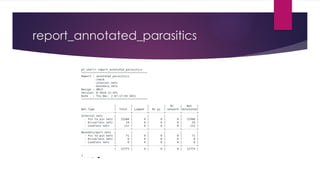

The document outlines the prime time static timing analysis (STA) flow, which is performed in two stages: pre-layout and post-layout. It details the necessary inputs, including netlists, standard cell libraries, interconnect delays, and constraints, required for accurate timing analysis. Additionally, it provides step-by-step instructions for setting up the analysis environment and executing commands to obtain timing reports.