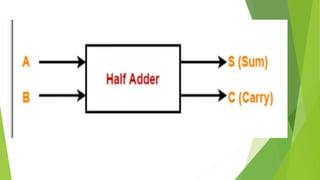

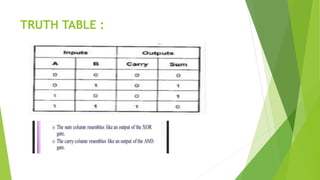

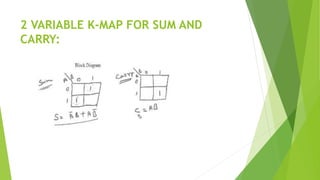

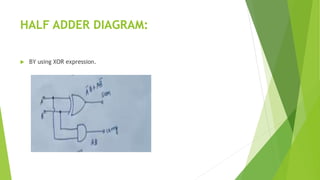

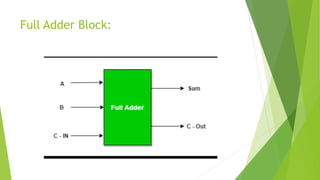

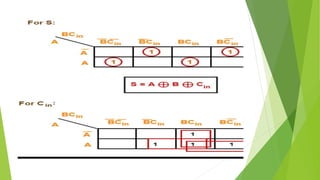

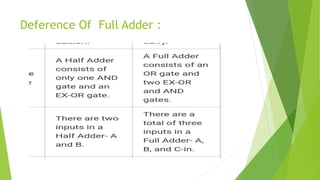

The document presents a detailed explanation of half and full adders in digital logic design. A half adder adds two input bits and produces sum and carry outputs, while a full adder adds three inputs, accounting for a carry input from a previous addition. Both digital circuits use specific logic gates, with designs including truth tables, K-maps, and Boolean expressions.