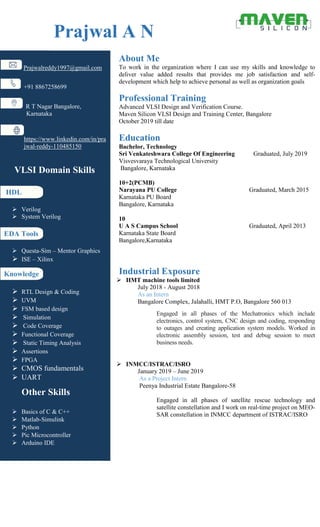

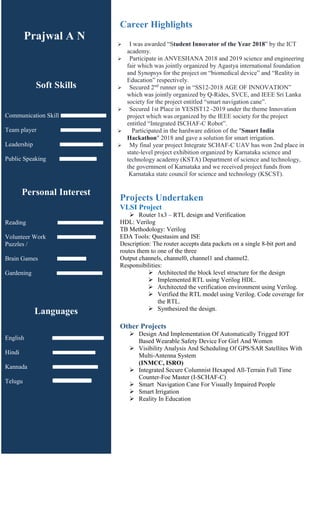

Prajwal provides a concise summary of his background and qualifications. He aims to use his skills and knowledge to deliver value and job satisfaction while achieving personal and organizational goals. He has a bachelor's degree in technology and specialized training in VLSI design and verification. His experience includes internships in mechatronics, satellite technology, and FPGA development. He has strong skills in Verilog, SystemVerilog, simulation tools, and microcontrollers. Prajwal has received awards for his innovative student projects and publications. He seeks to contribute as a team player with communication skills and leadership abilities.