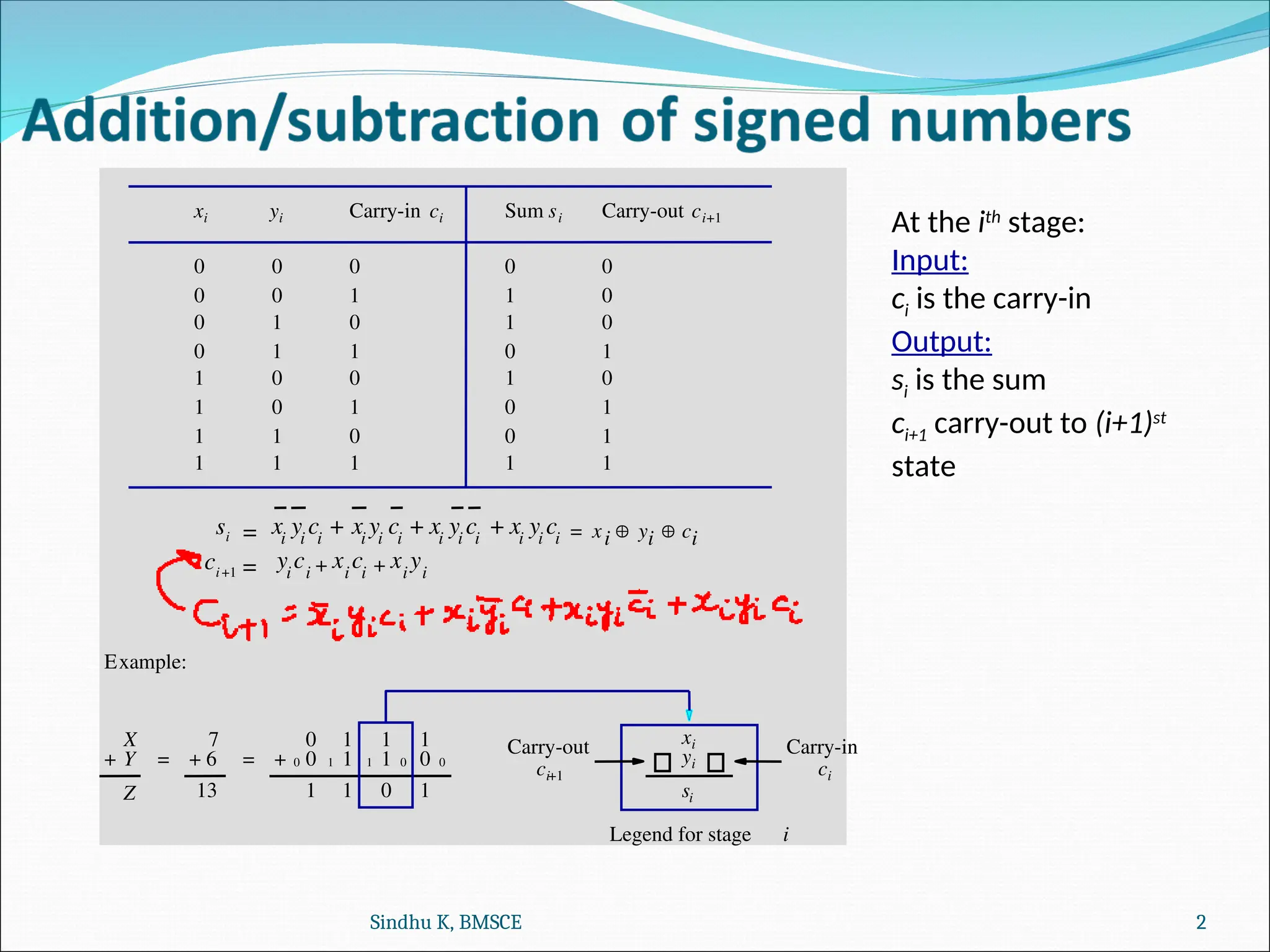

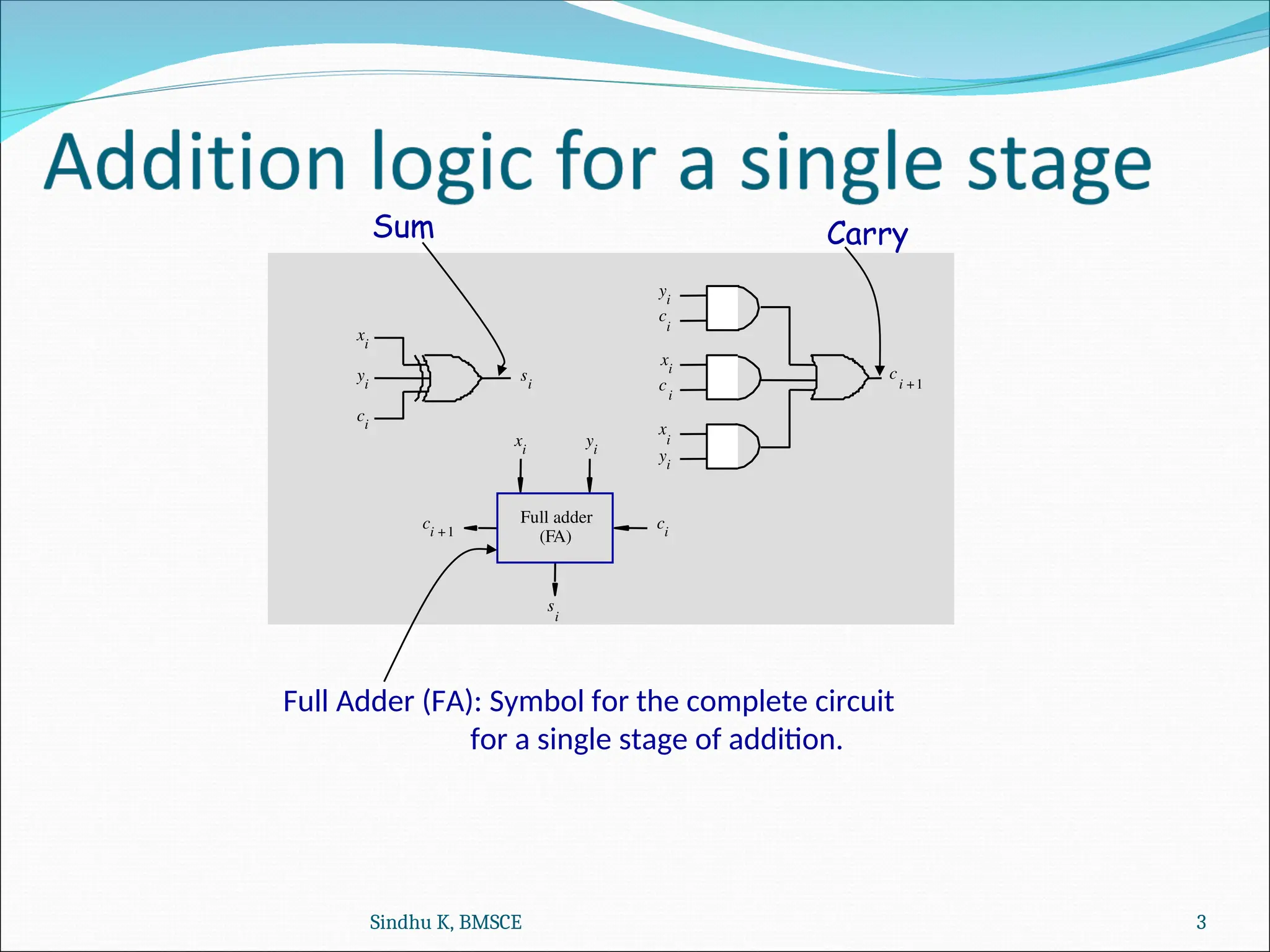

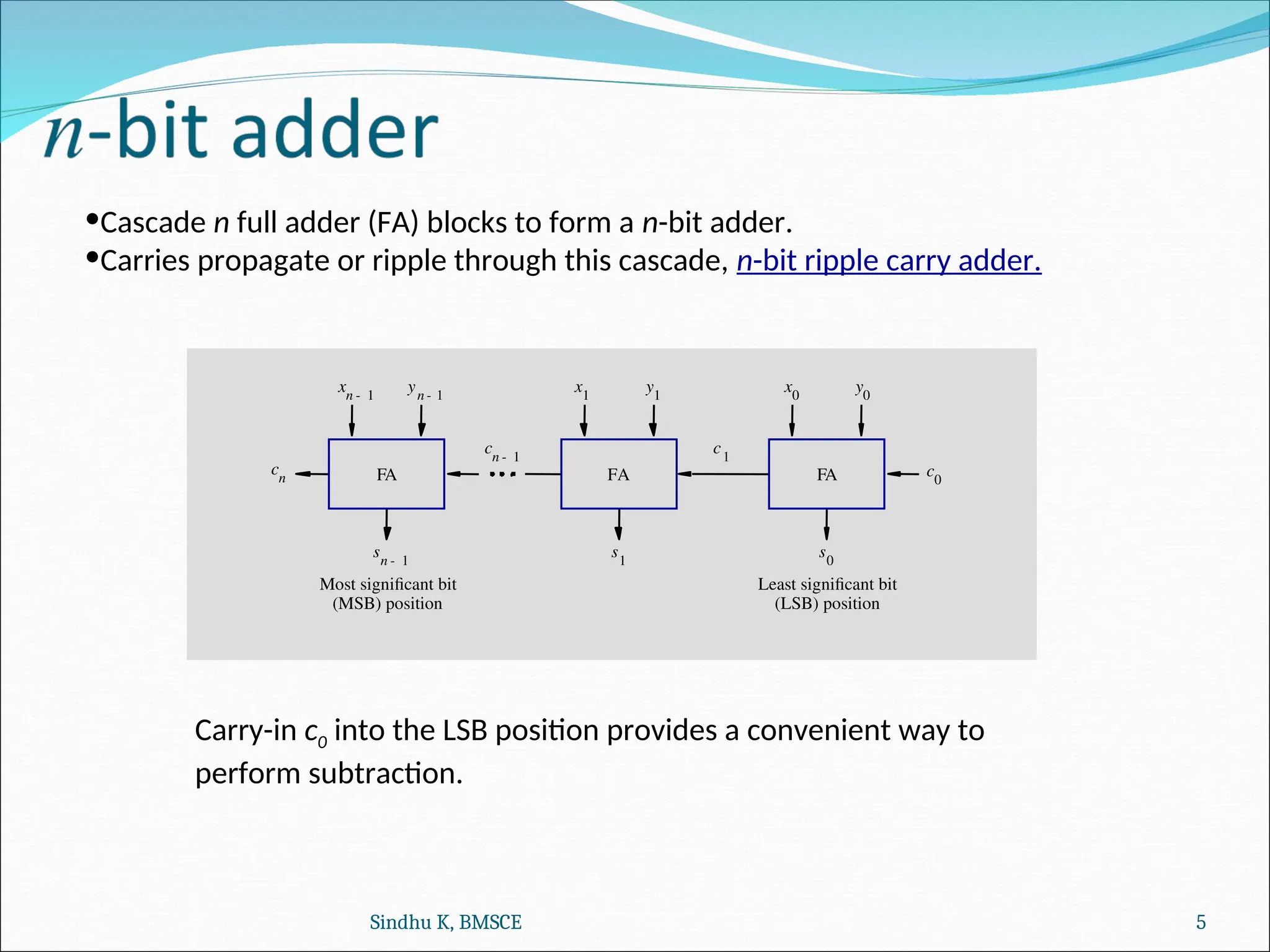

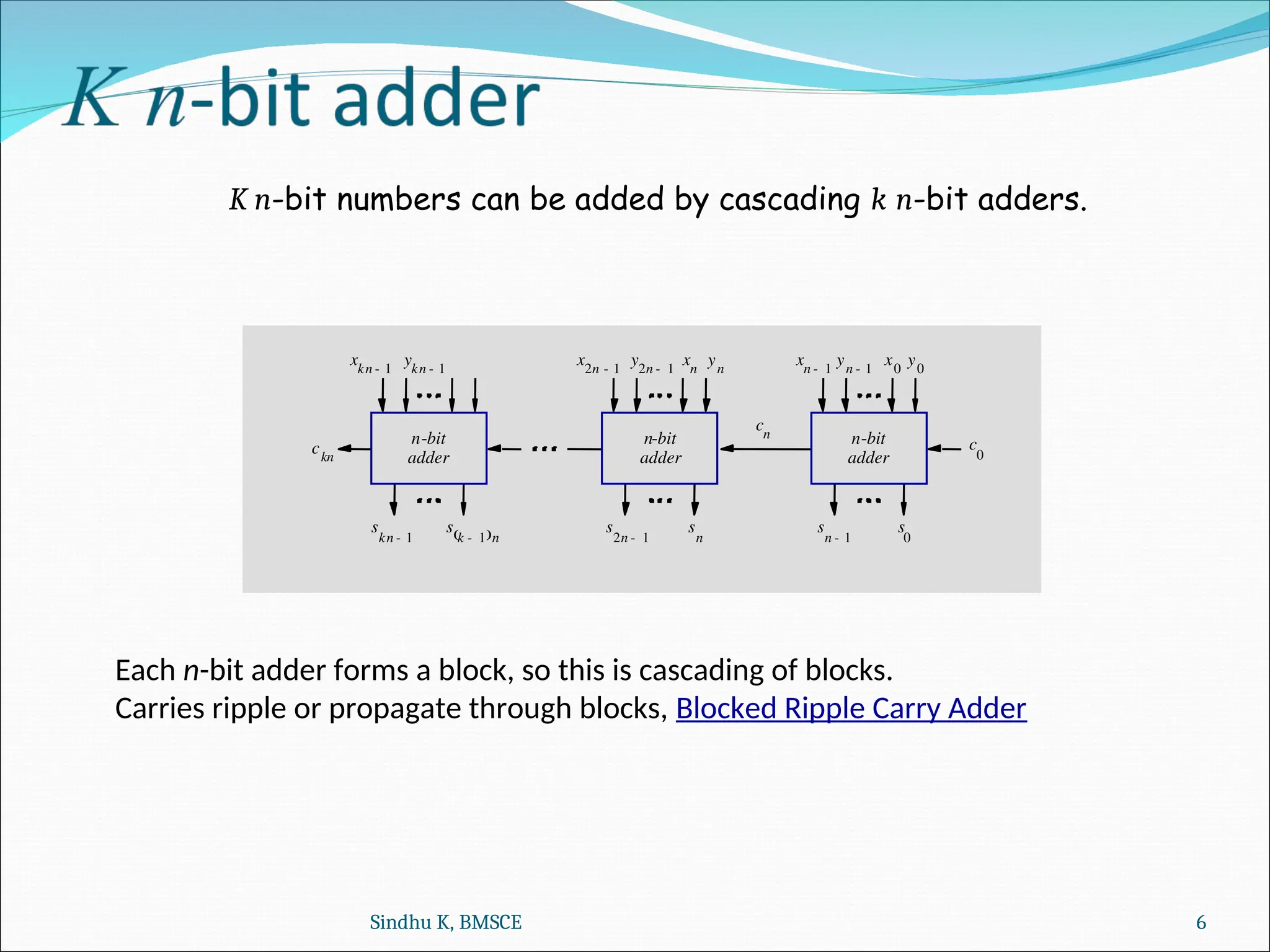

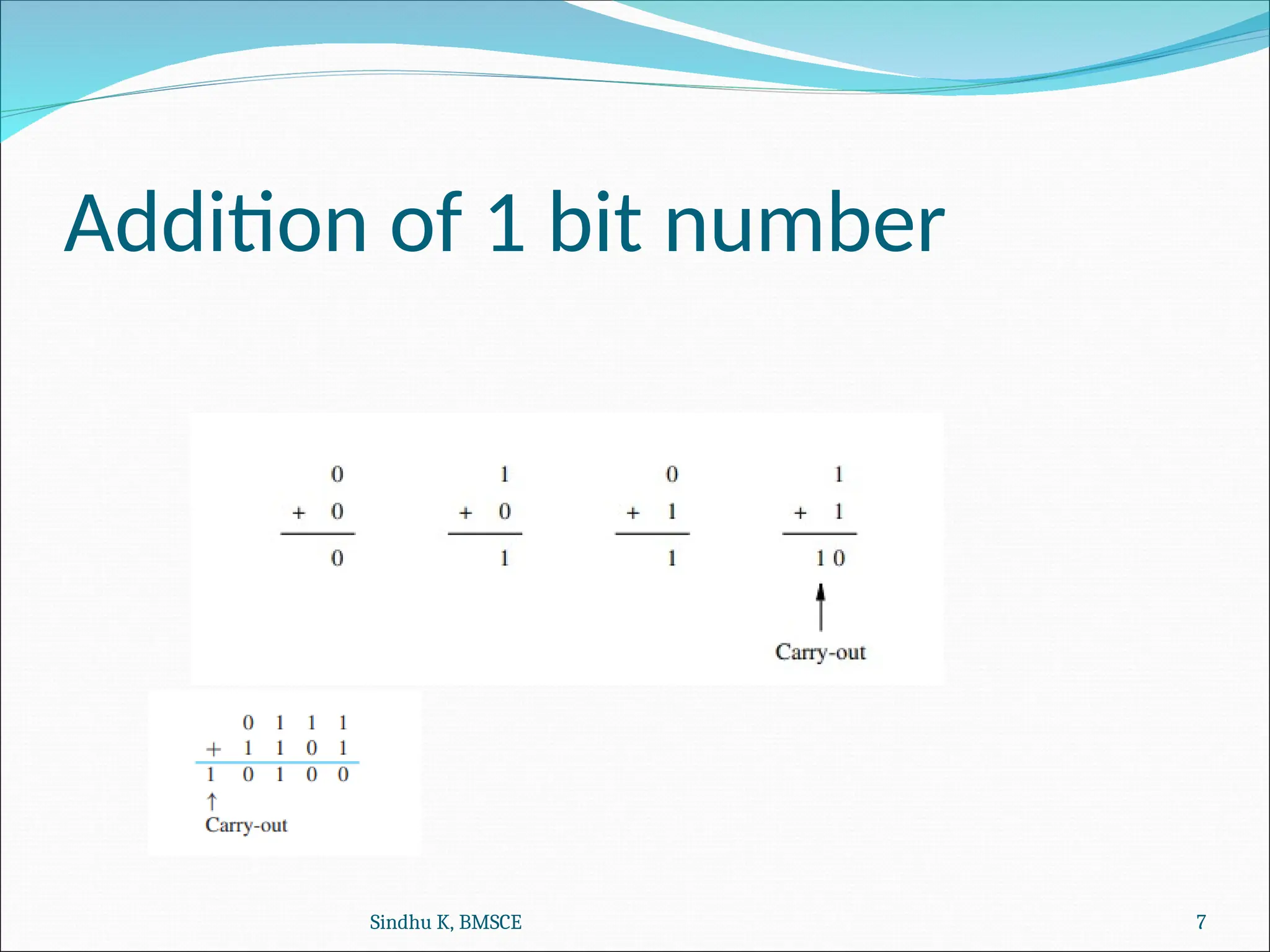

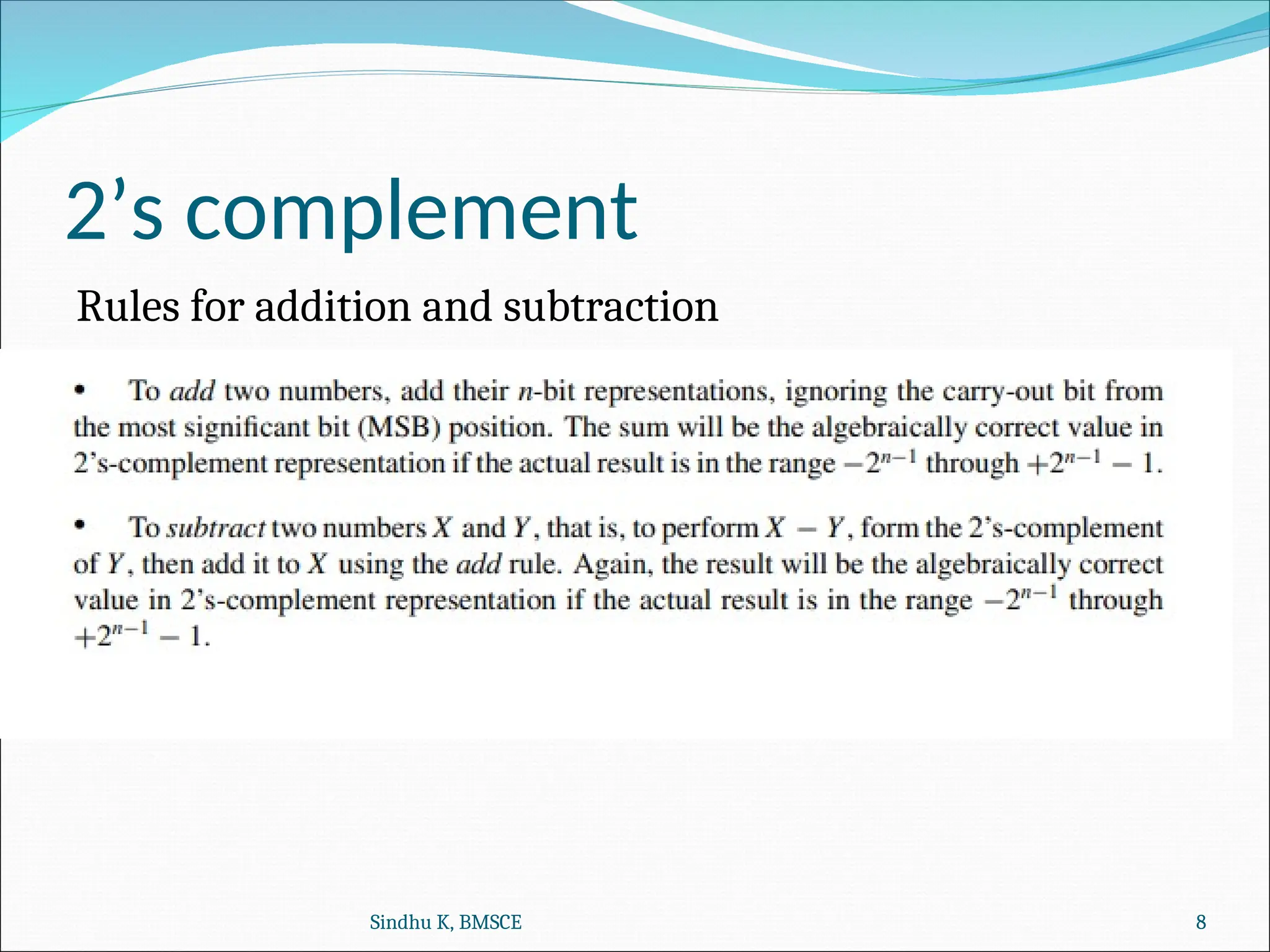

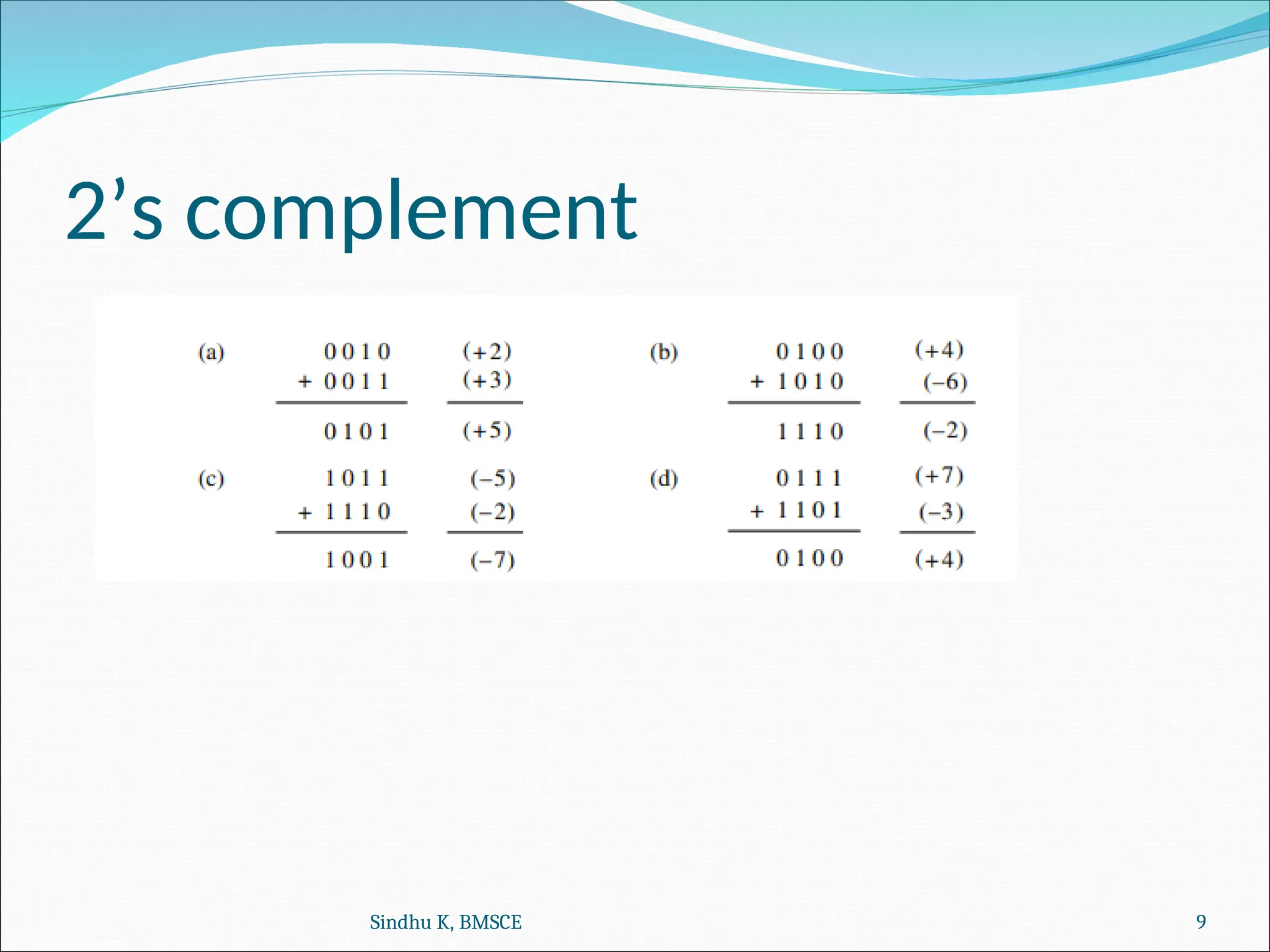

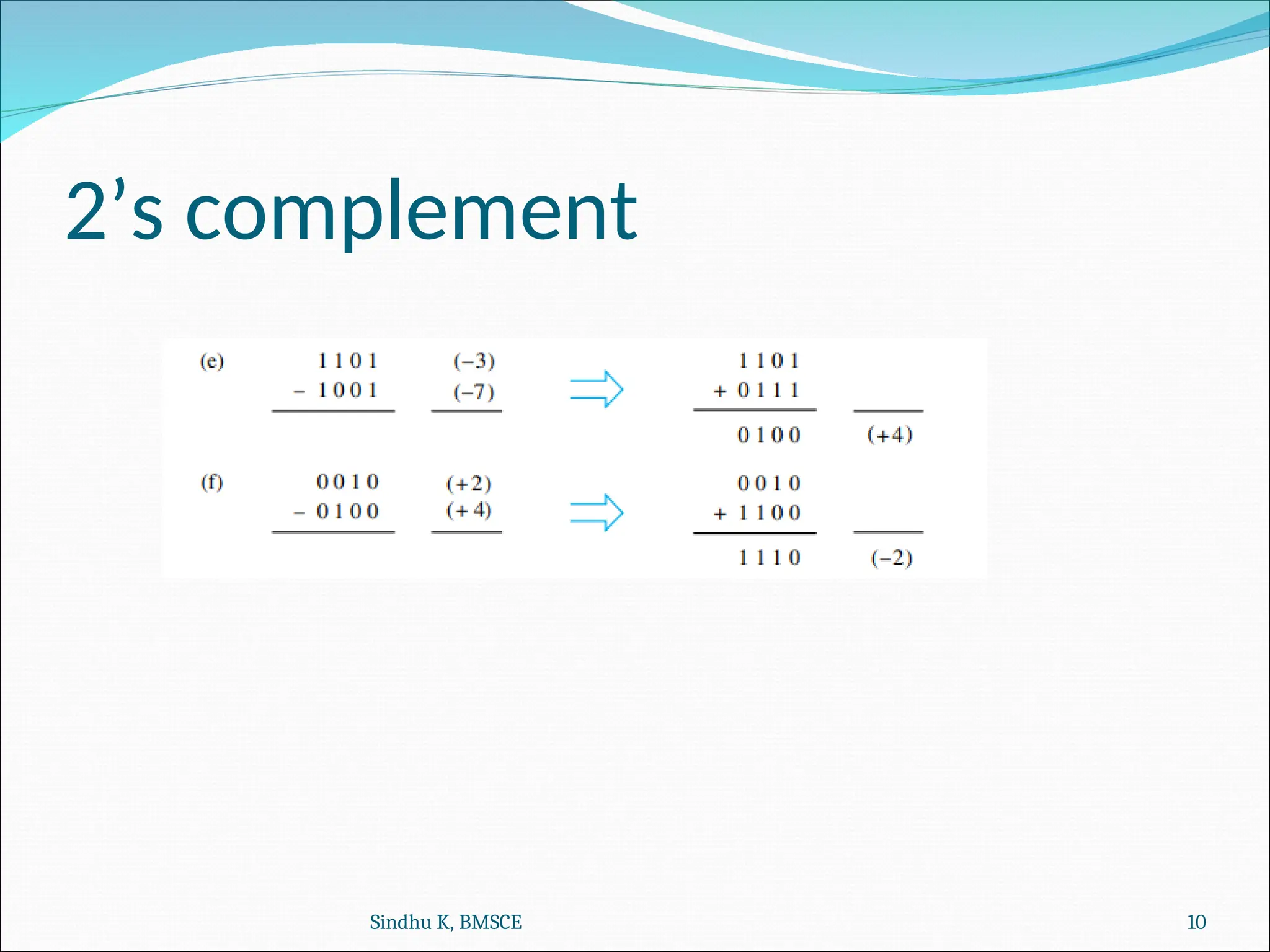

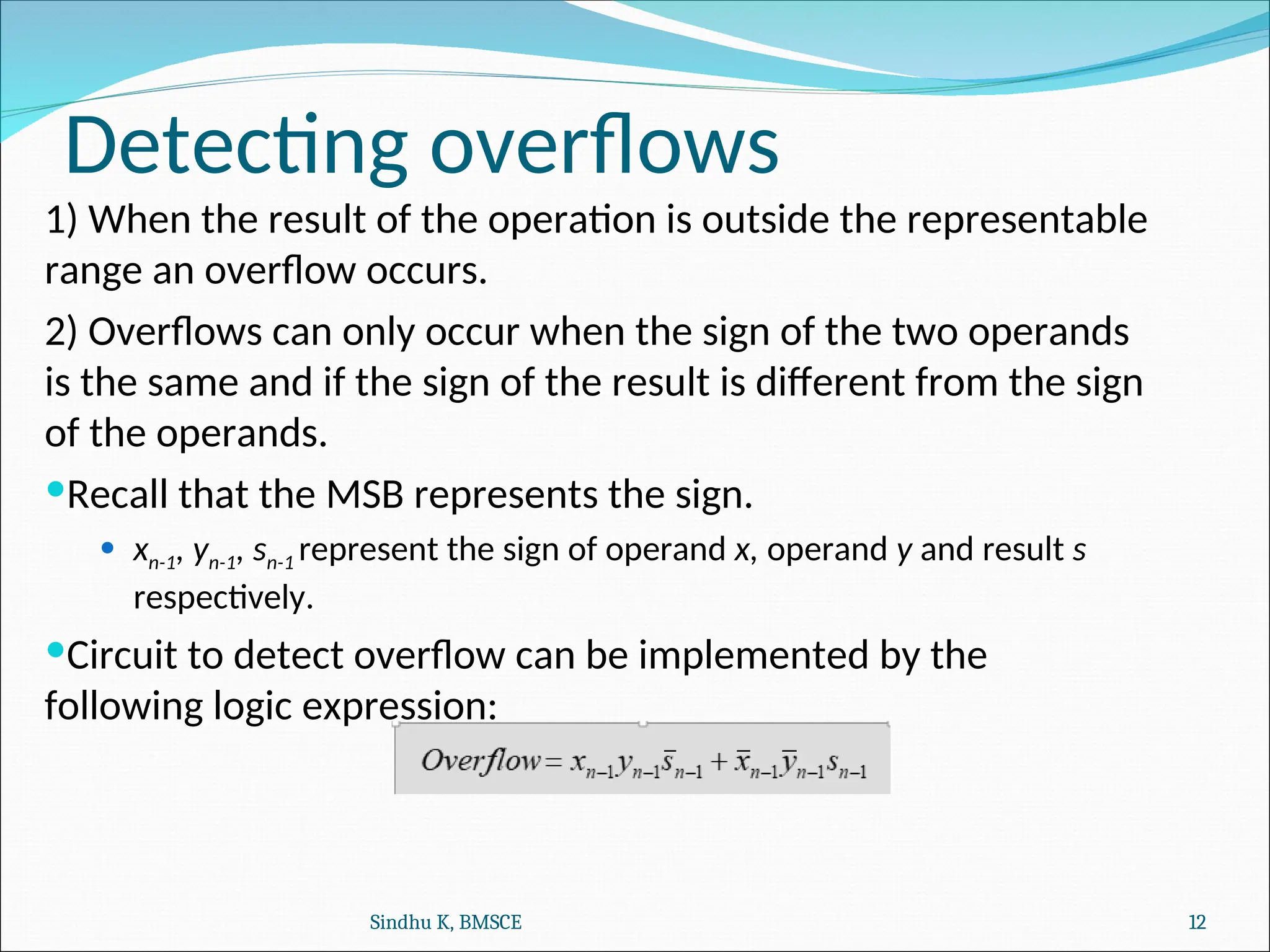

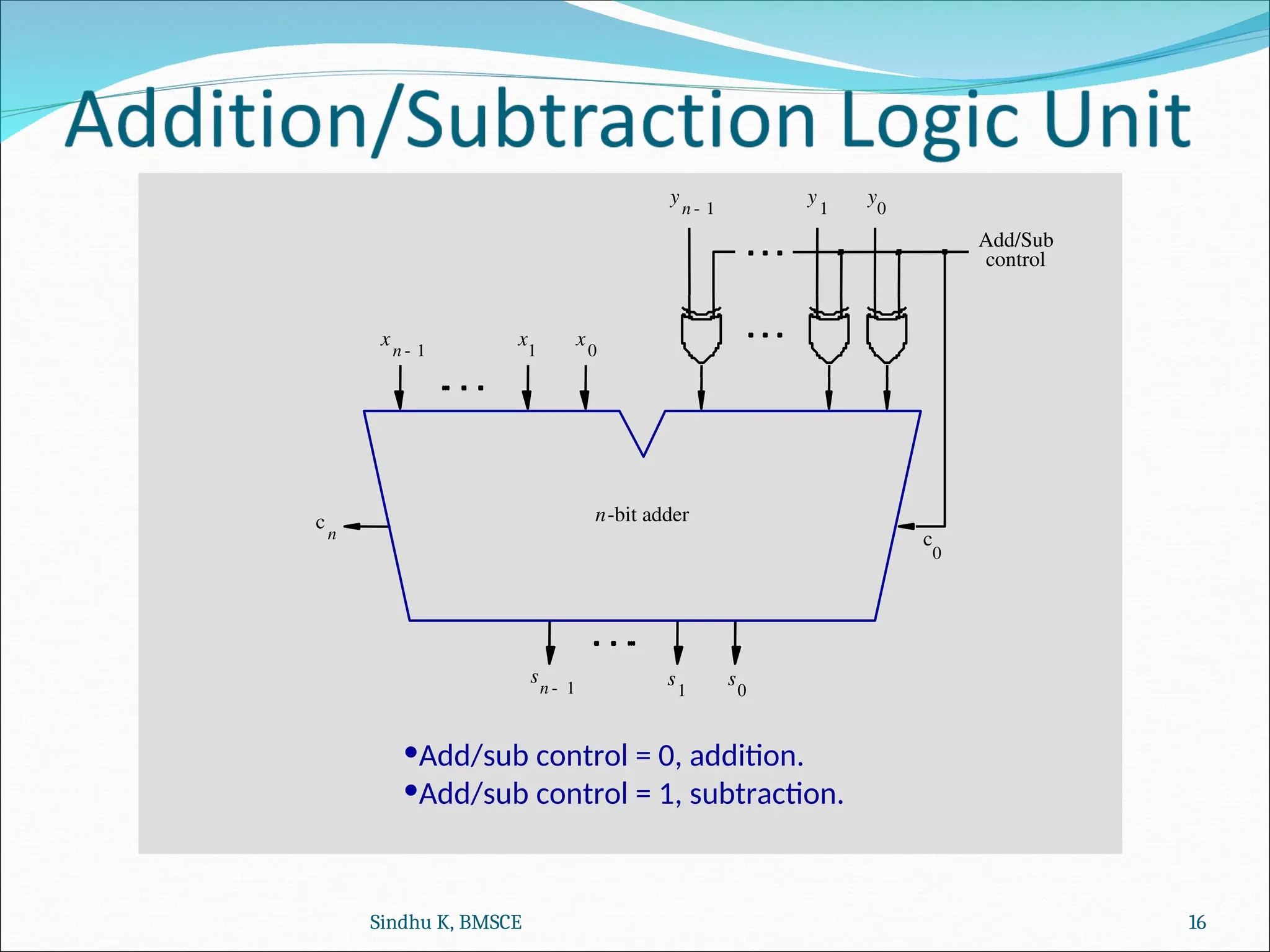

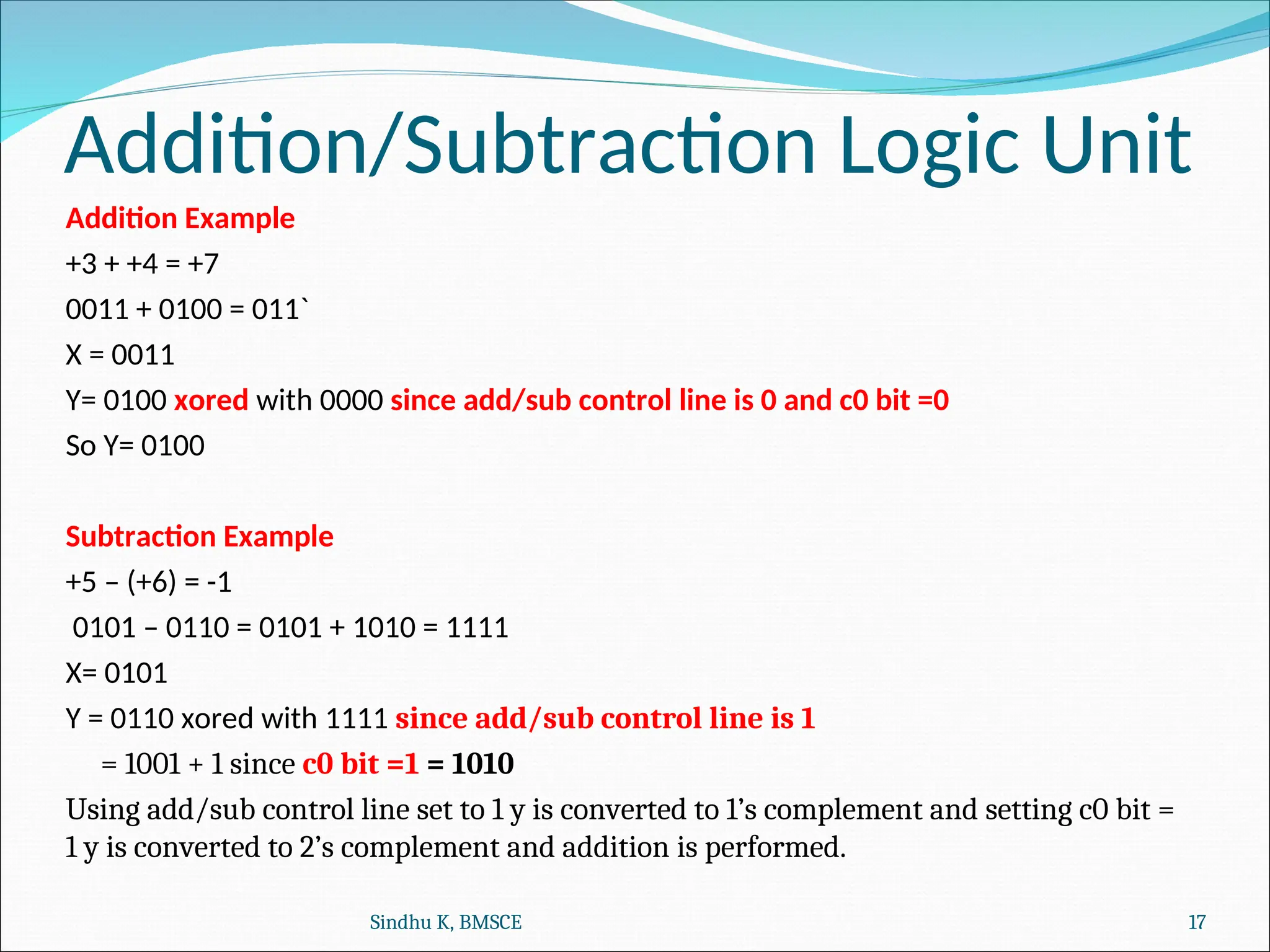

The document discusses computer organization and architecture, focusing on concepts such as full adders, n-bit adders, and operations for addition and subtraction in signed numbers. It emphasizes 2's complement rules for arithmetic, overflow detection, and the logic required for implementing addition and subtraction using circuit design. The material includes examples to illustrate the operations, including the detection of overflow conditions.