Embed presentation

Downloaded 35 times

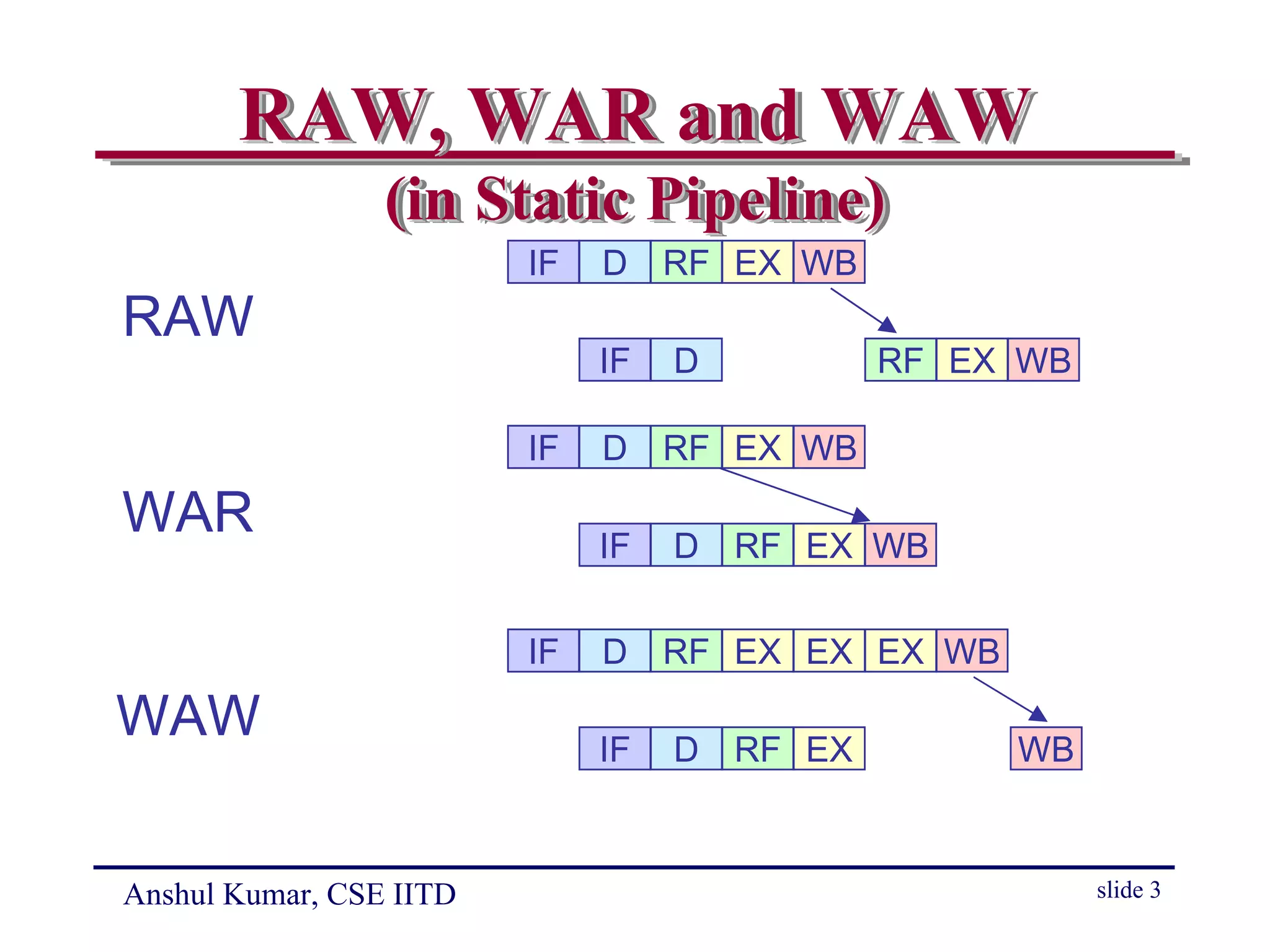

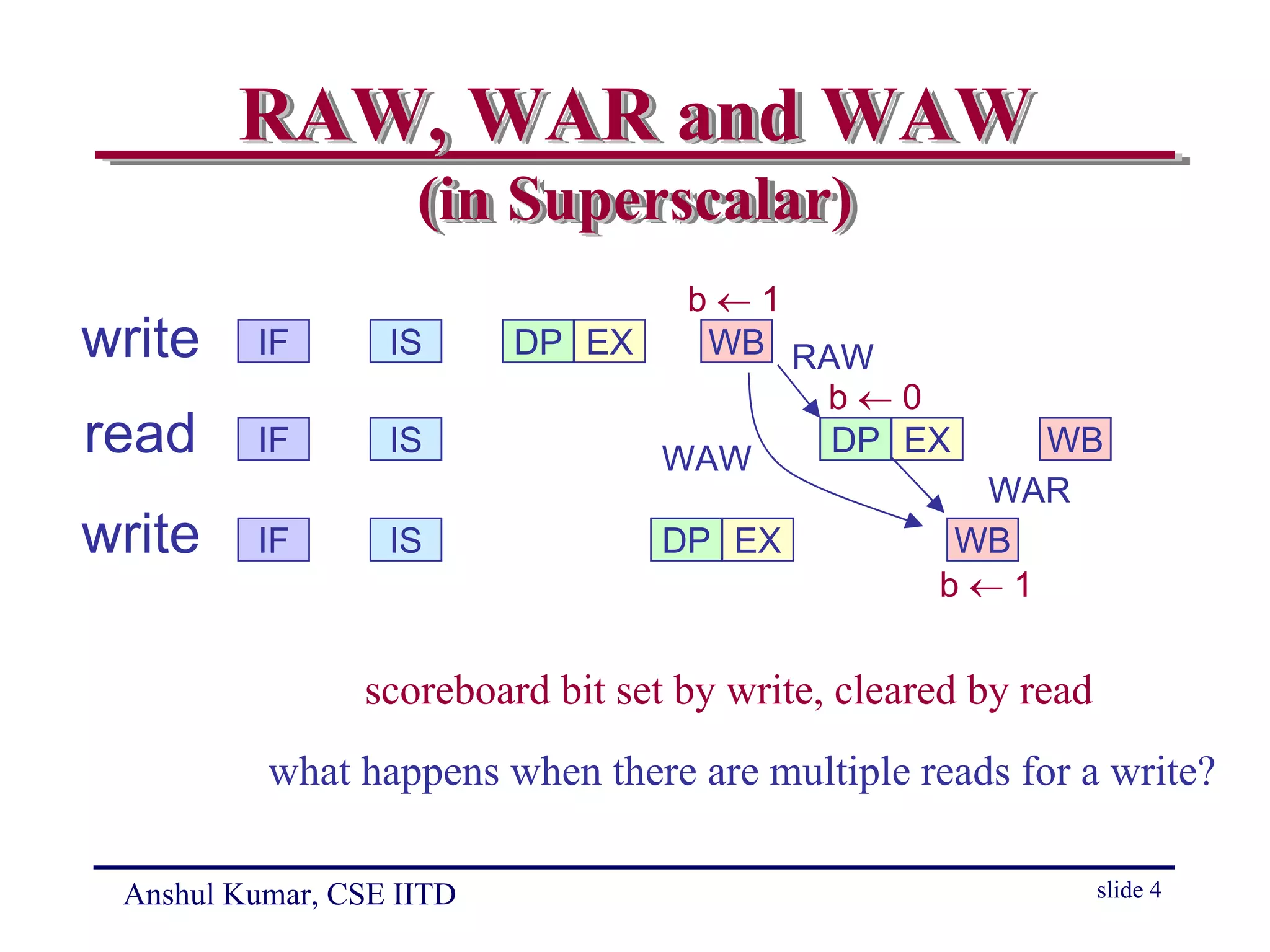

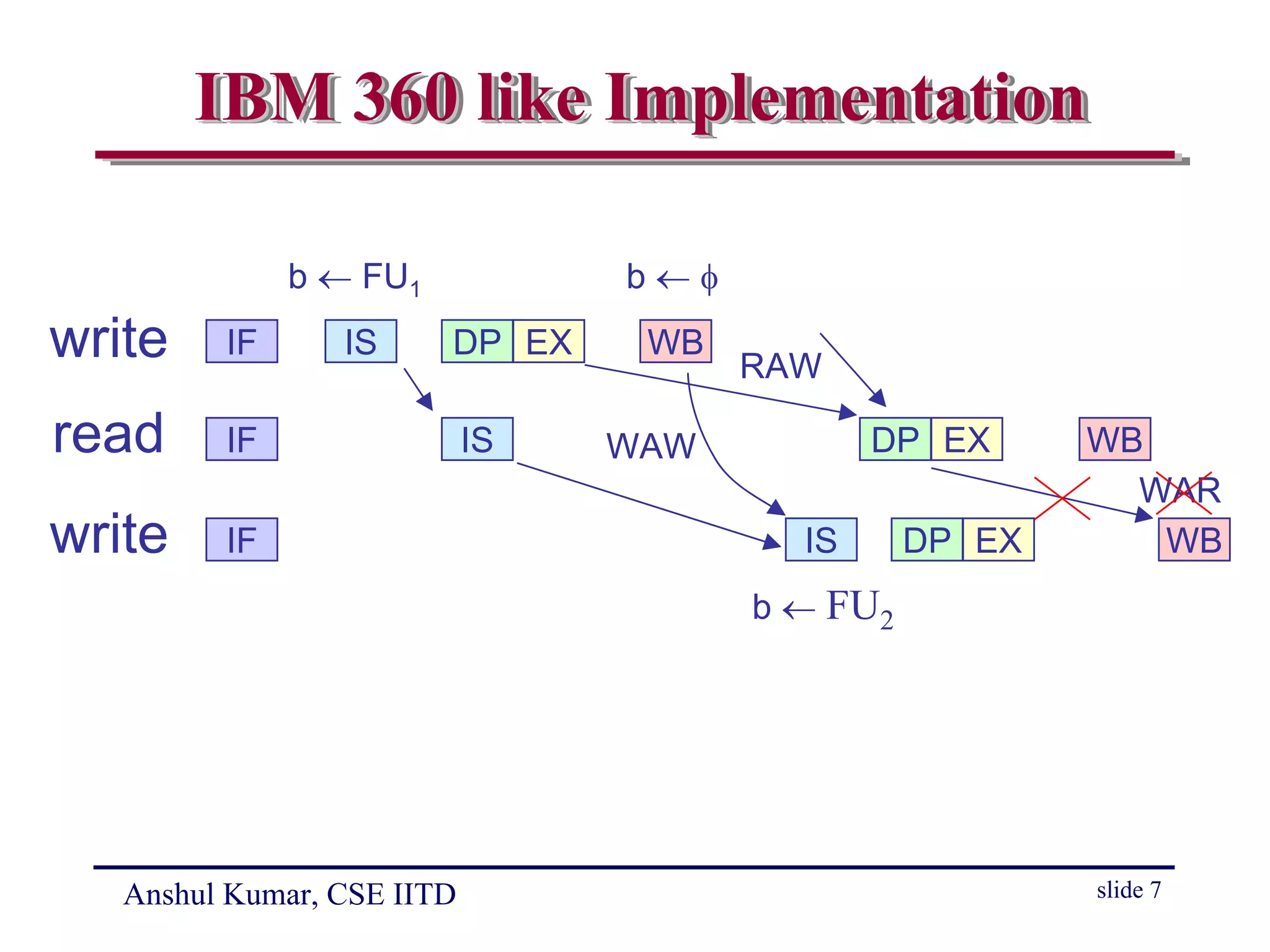

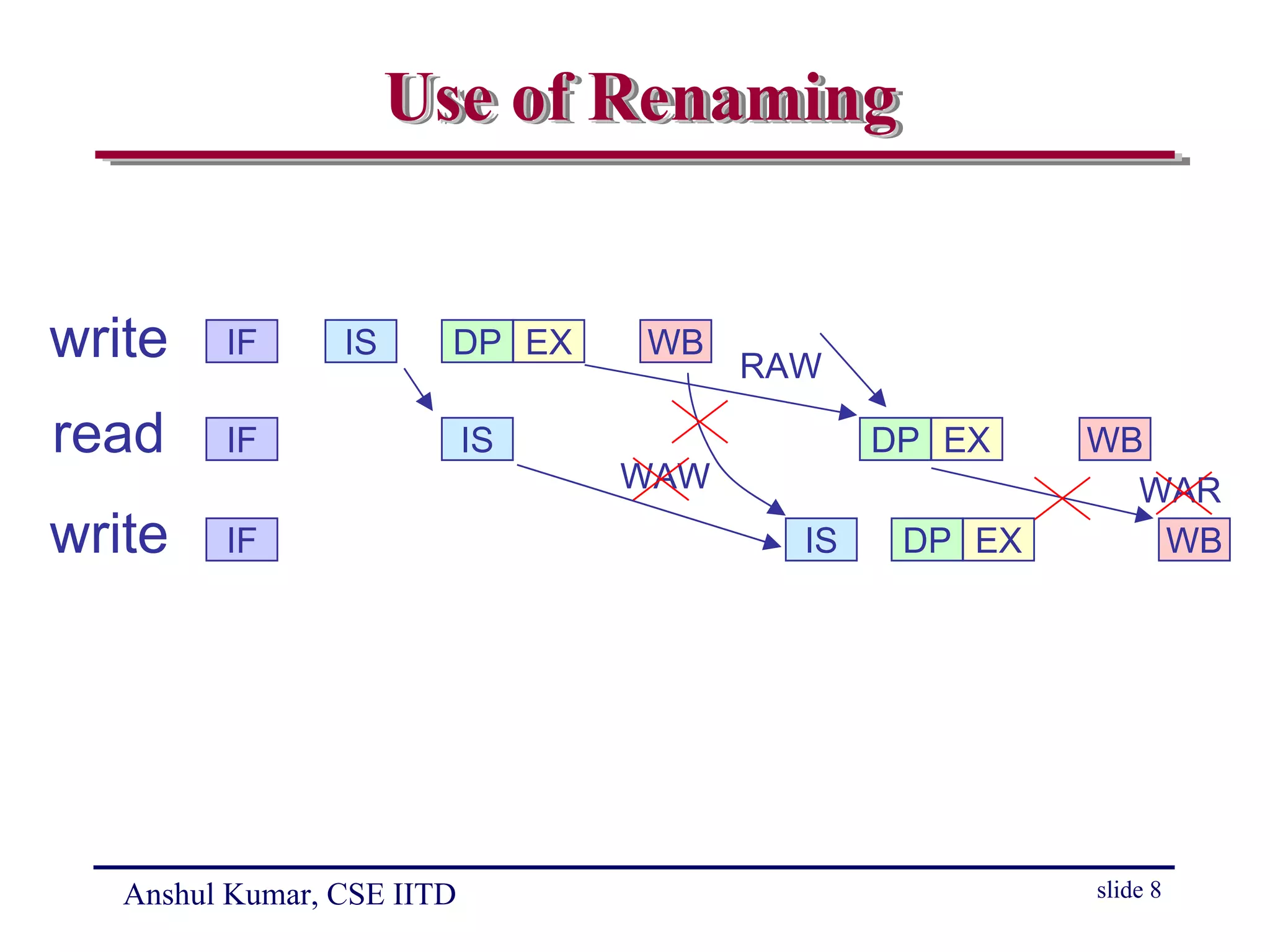

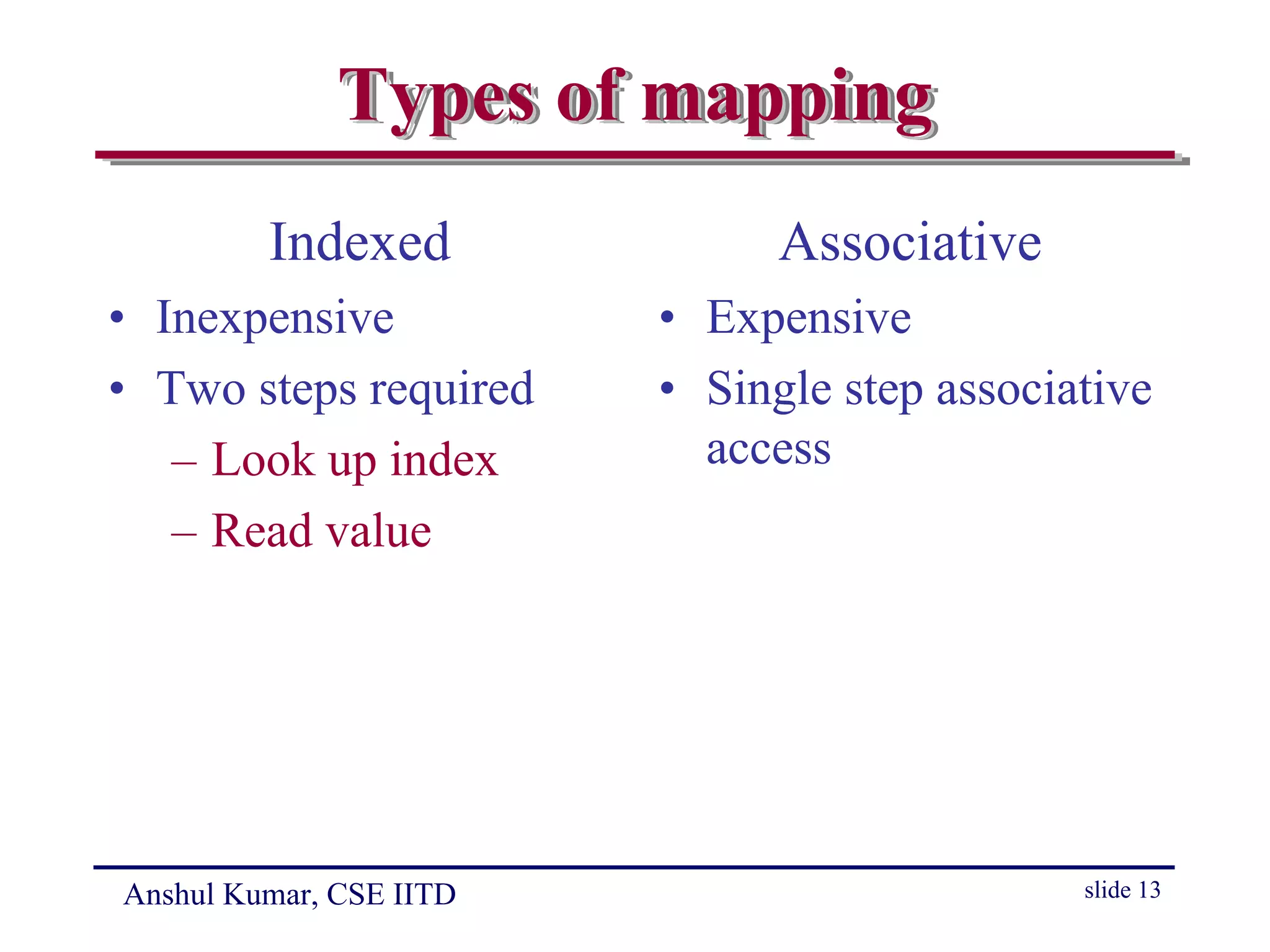

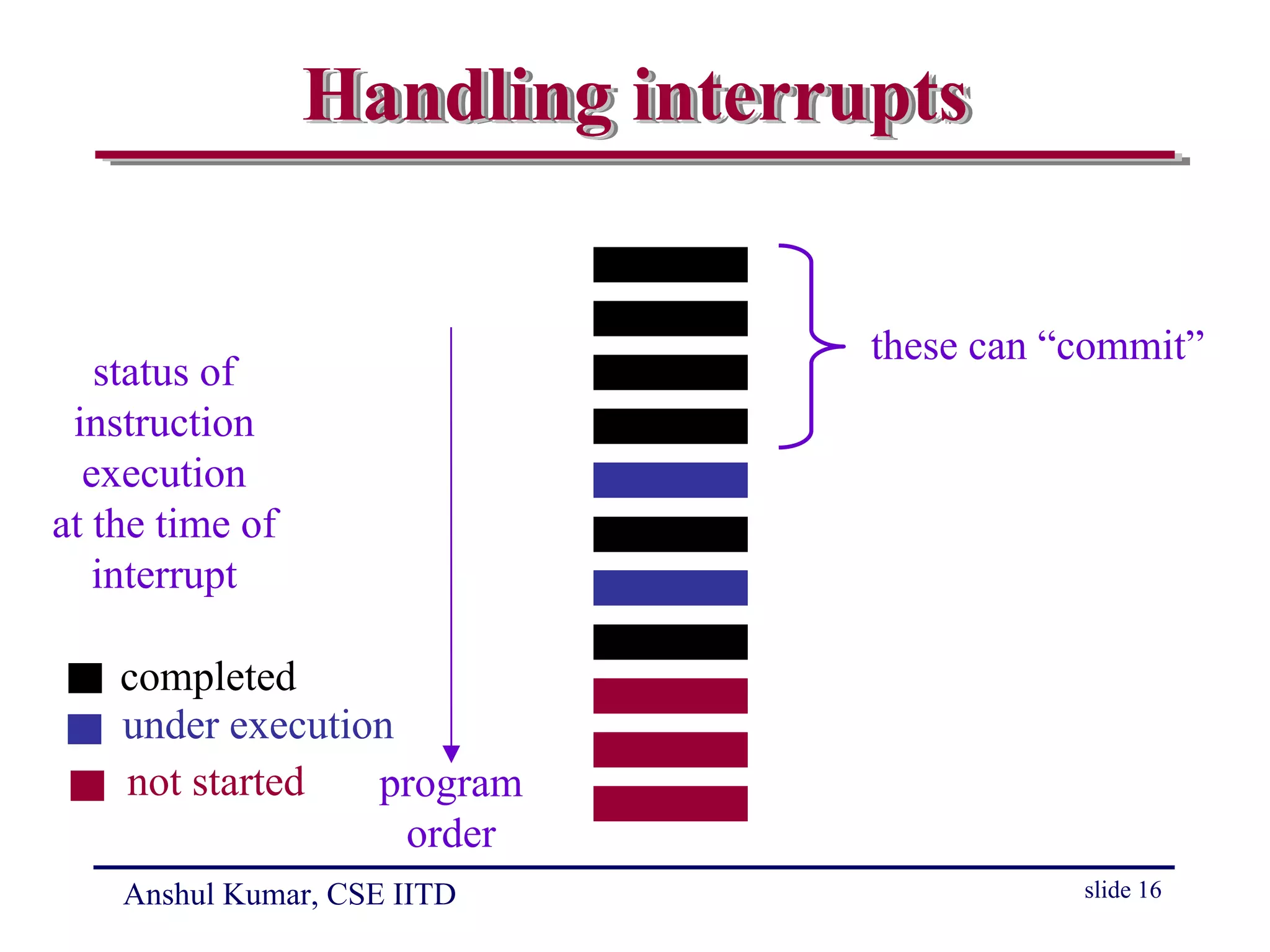

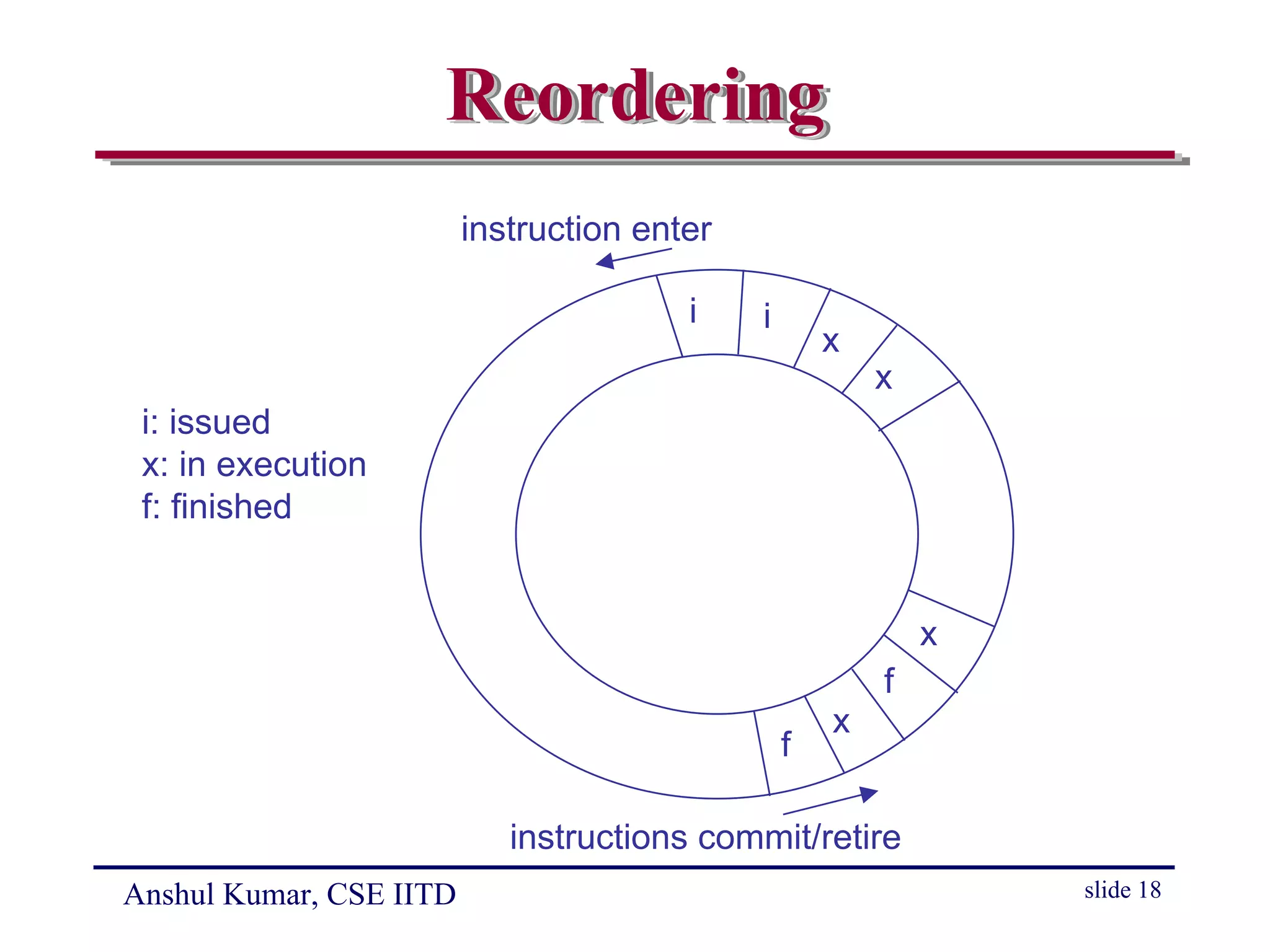

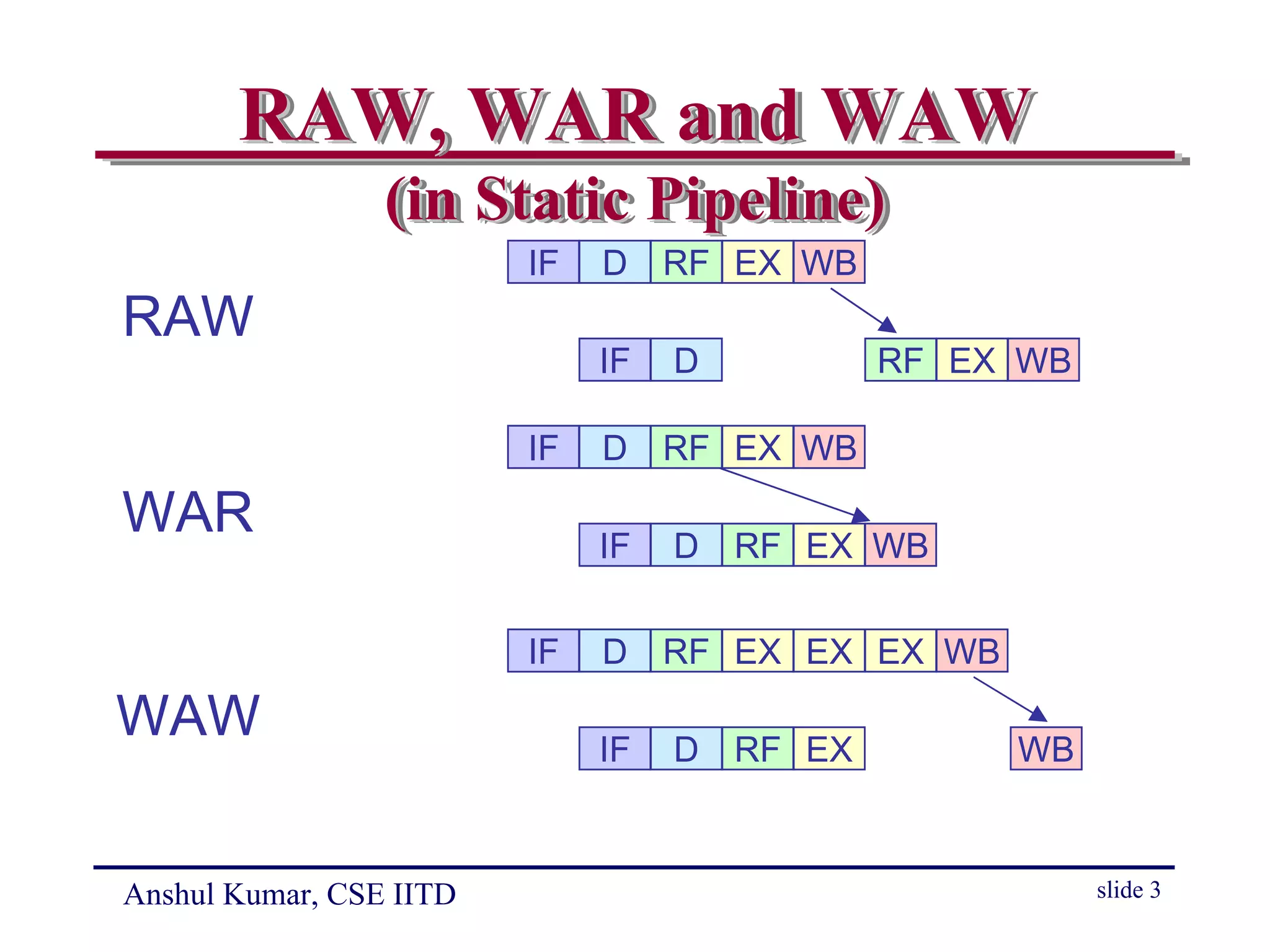

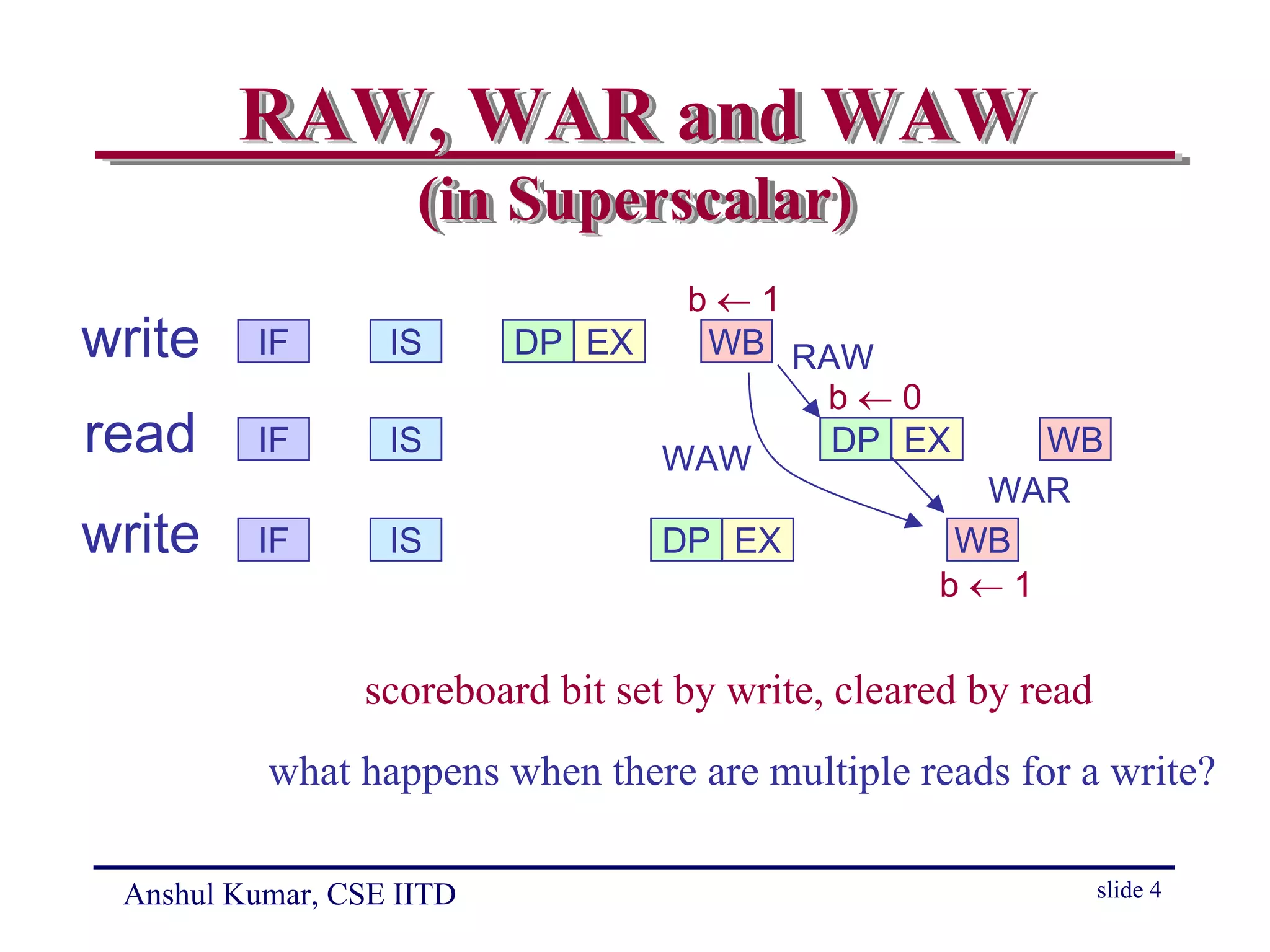

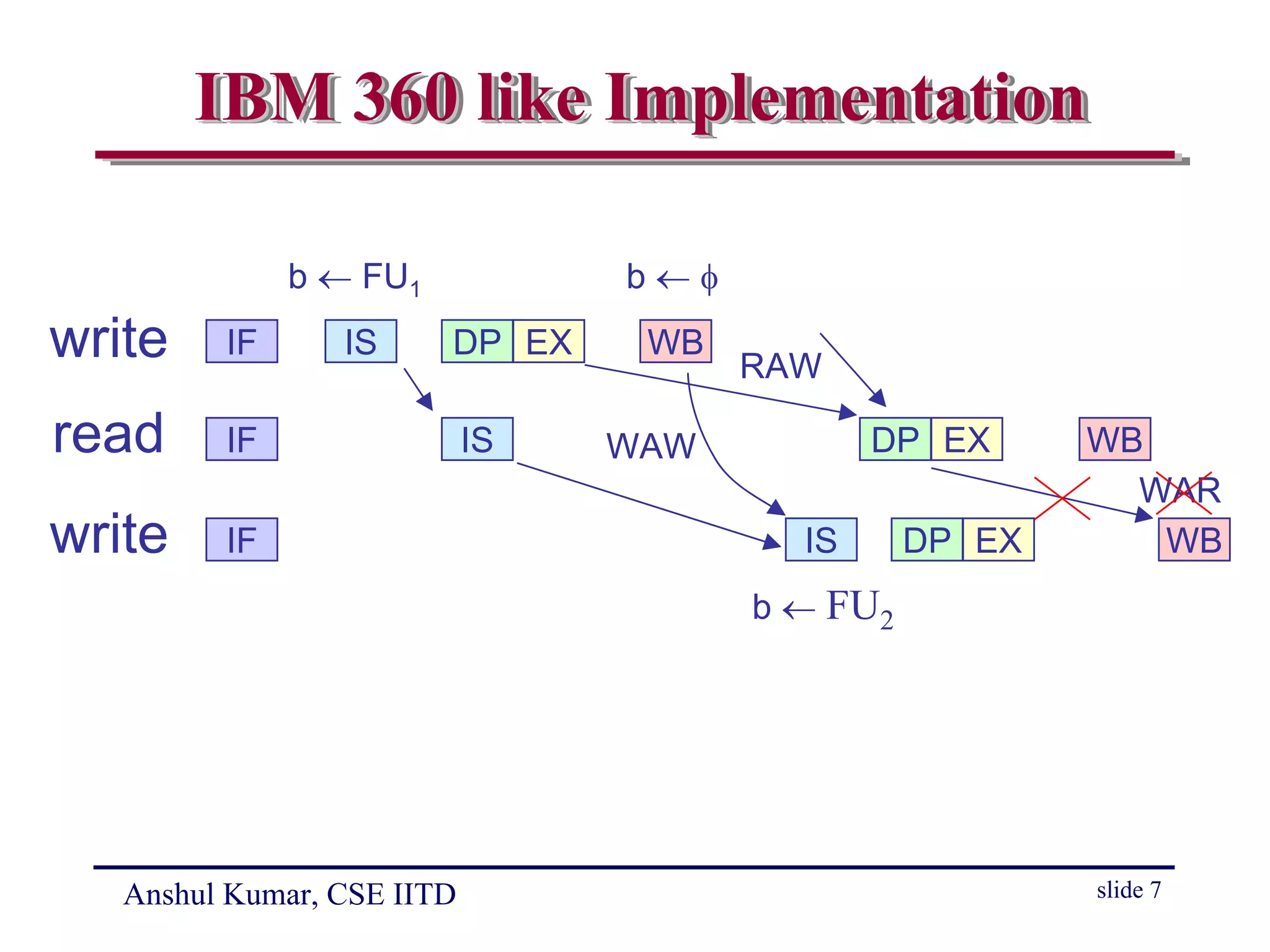

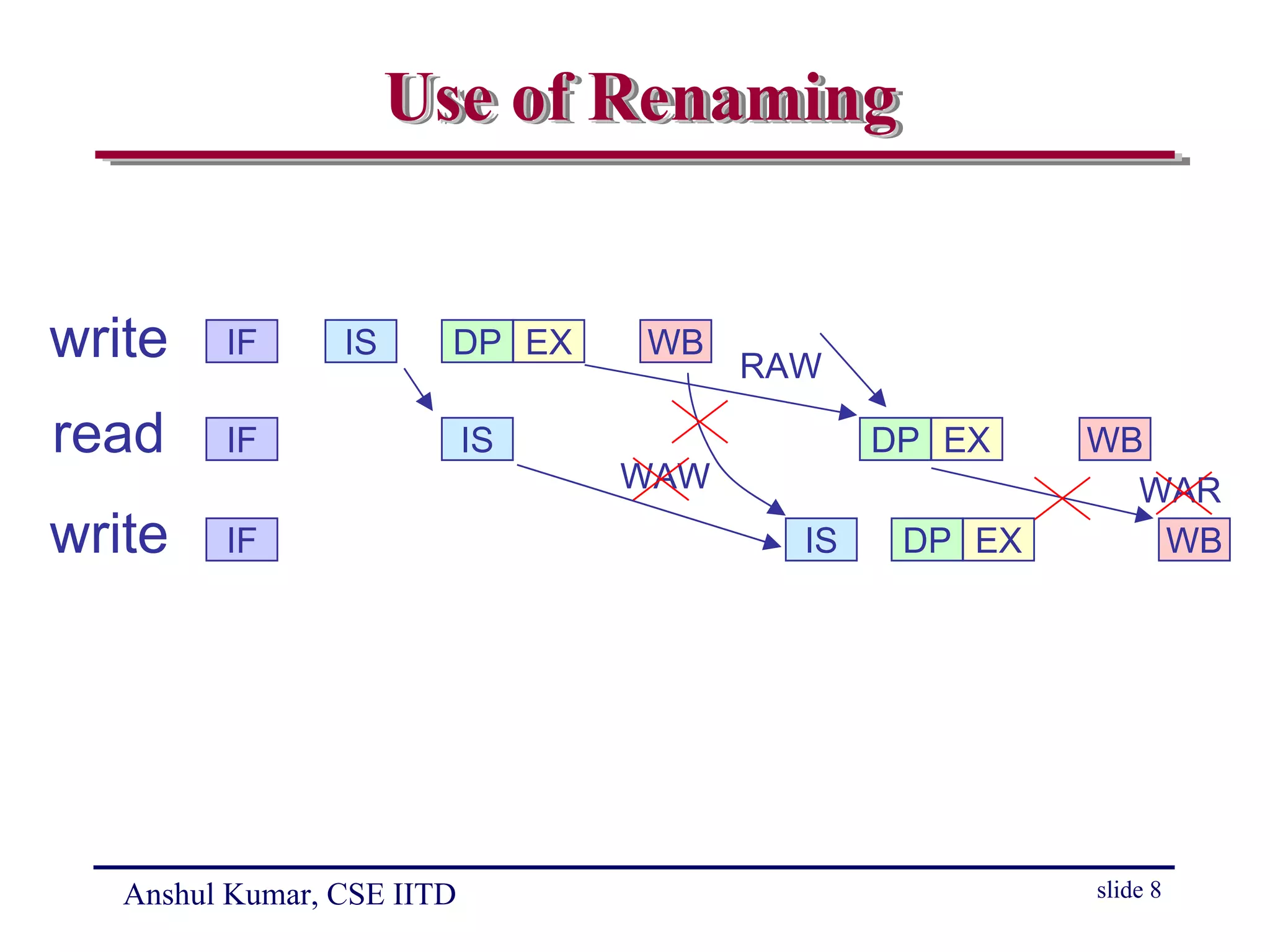

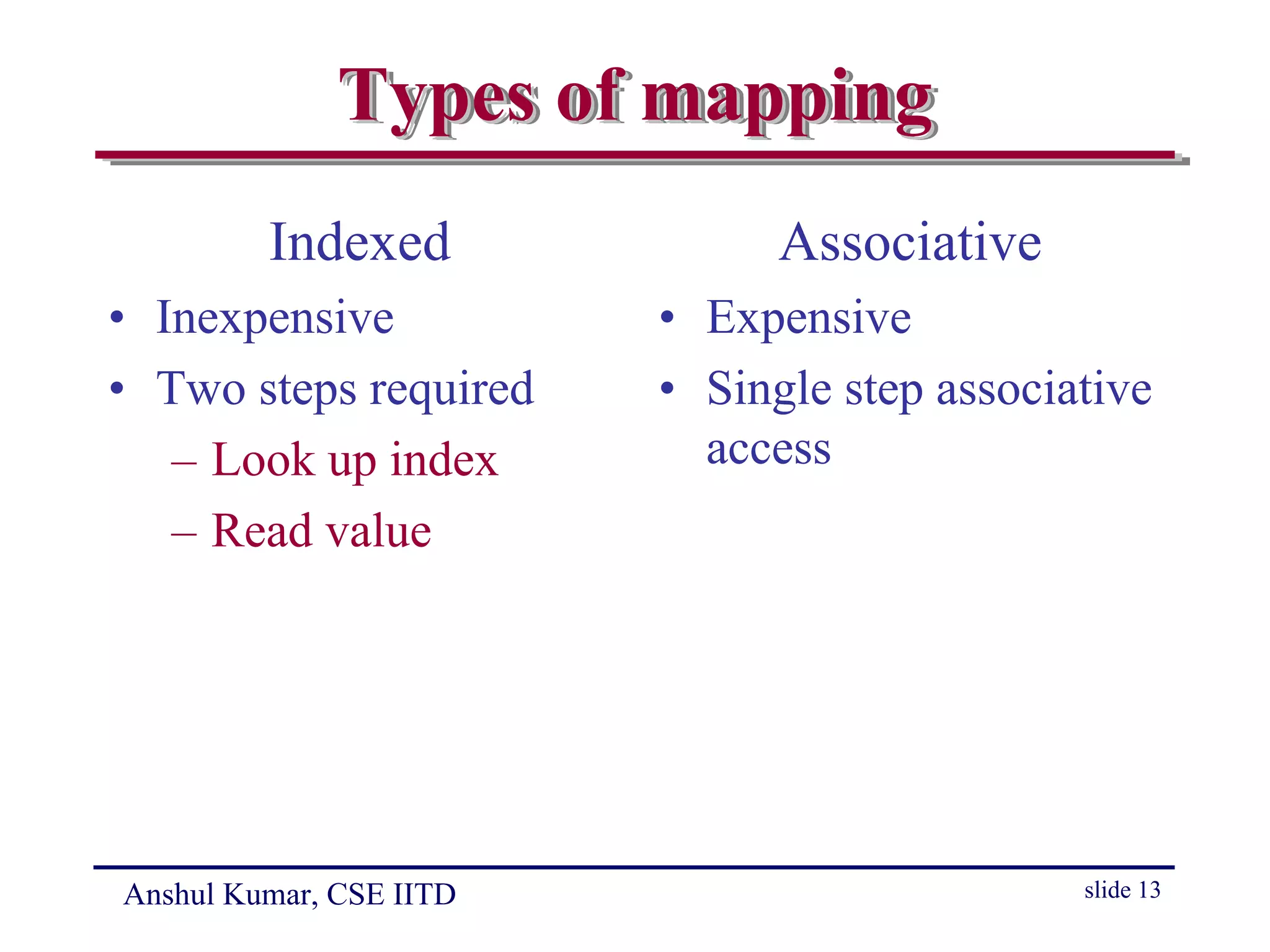

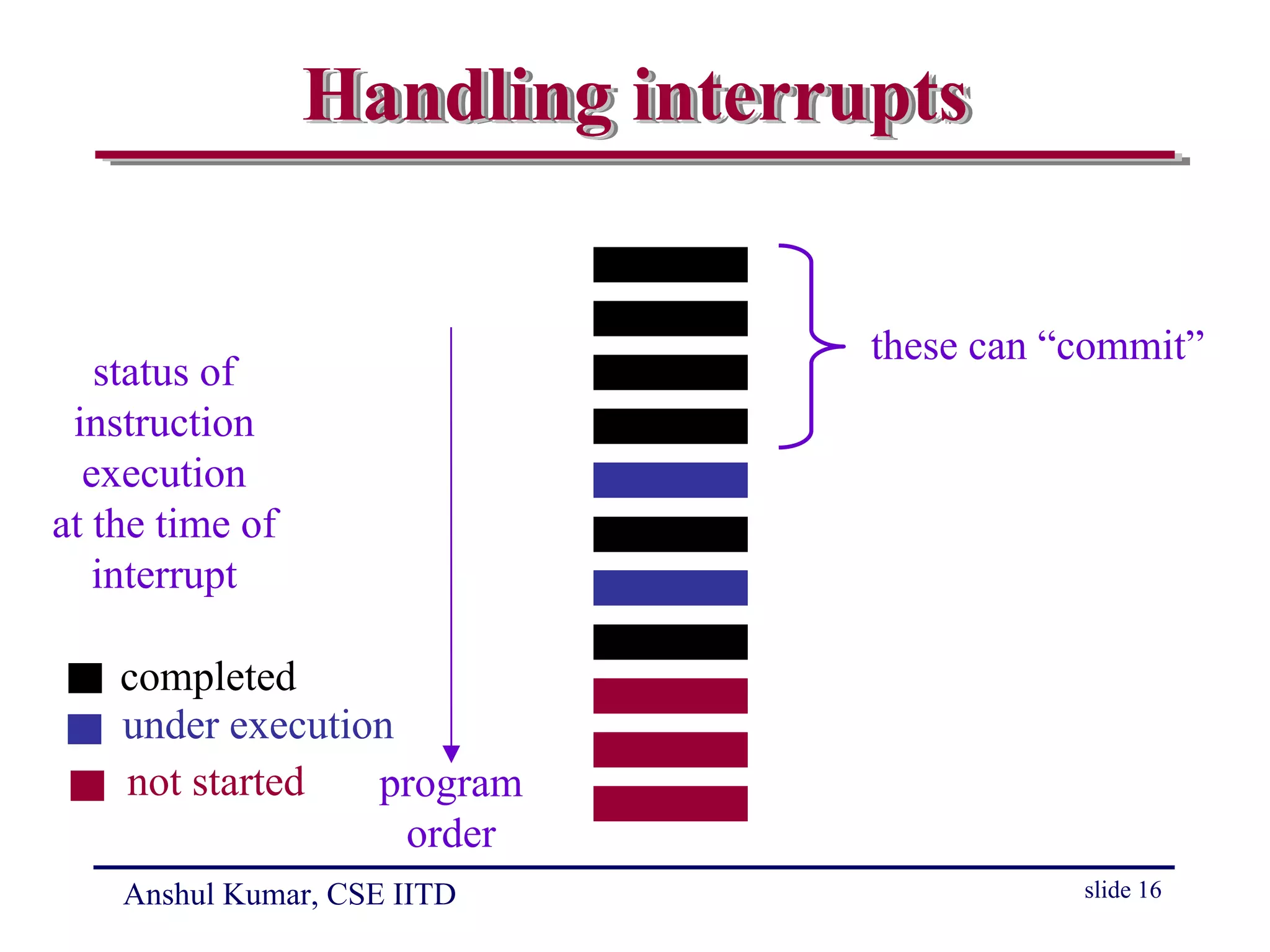

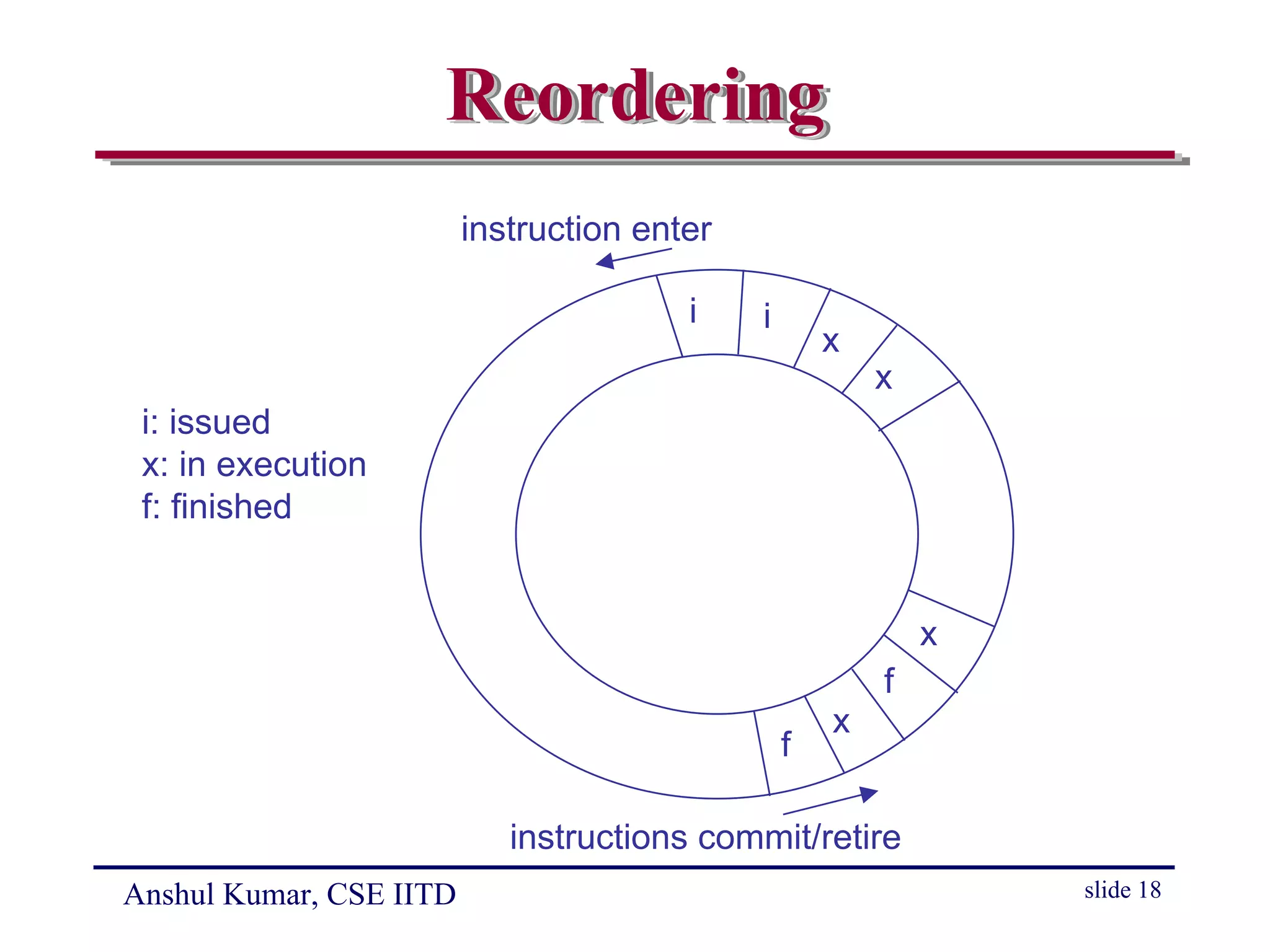

Register renaming and reordering allow superscalar processors to issue and execute instructions out of order to avoid dependencies. Register renaming removes false dependencies like write-after-read and write-after-write. A reordering buffer ensures sequential consistency for interrupts and enables speculative execution. The document discusses different techniques for register renaming using mapping tables or associative lookups, and how register renaming and reordering buffers work together to enable out-of-order execution in superscalar processors.