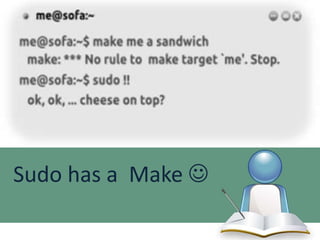

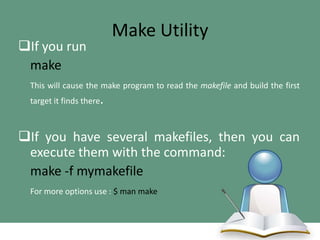

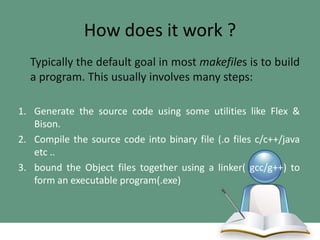

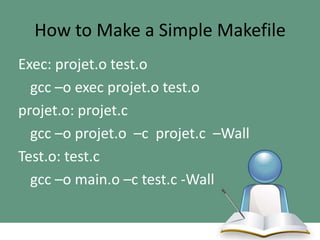

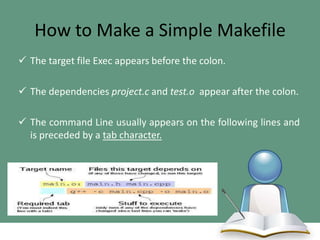

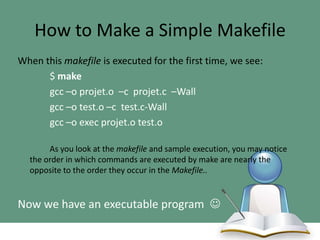

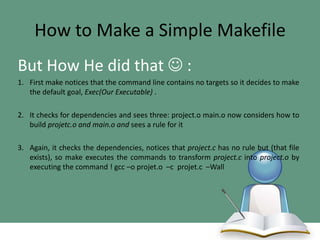

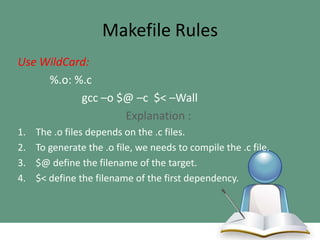

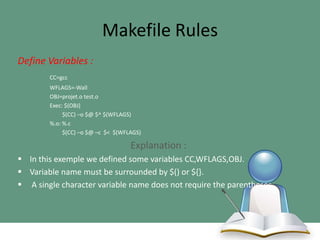

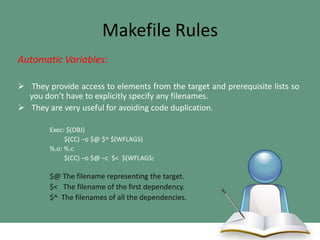

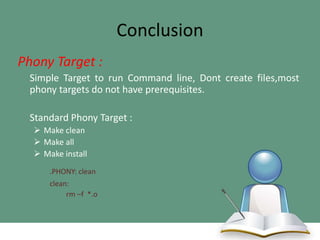

This document is a tutorial on using makefiles, explaining the utility of 'make' in managing project builds efficiently. It covers the structure of makefiles, how to write simple rules, and the use of variables and wildcards. Additionally, it highlights the importance of understanding phony targets and nuances like indentation requirements in makefiles.