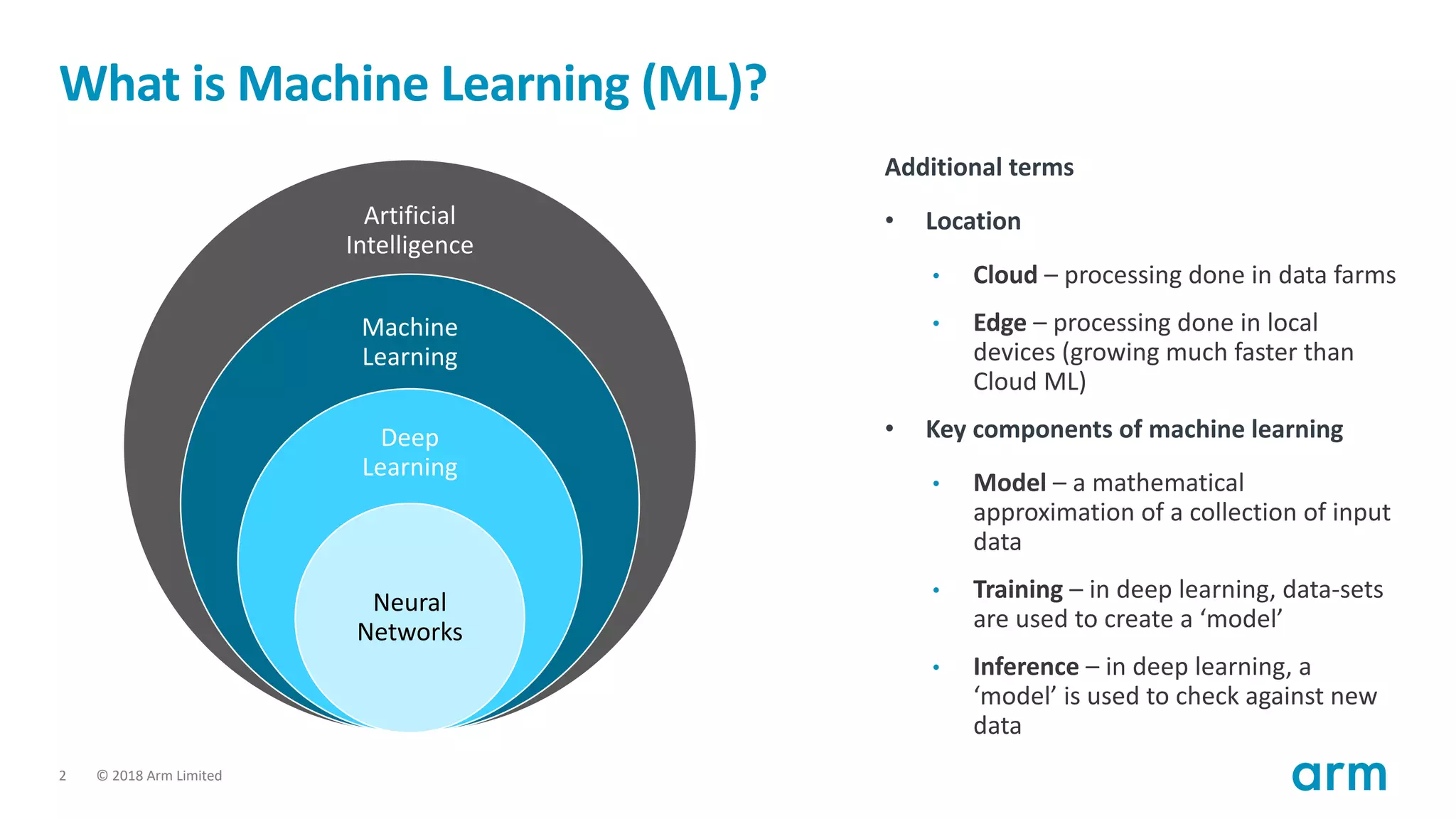

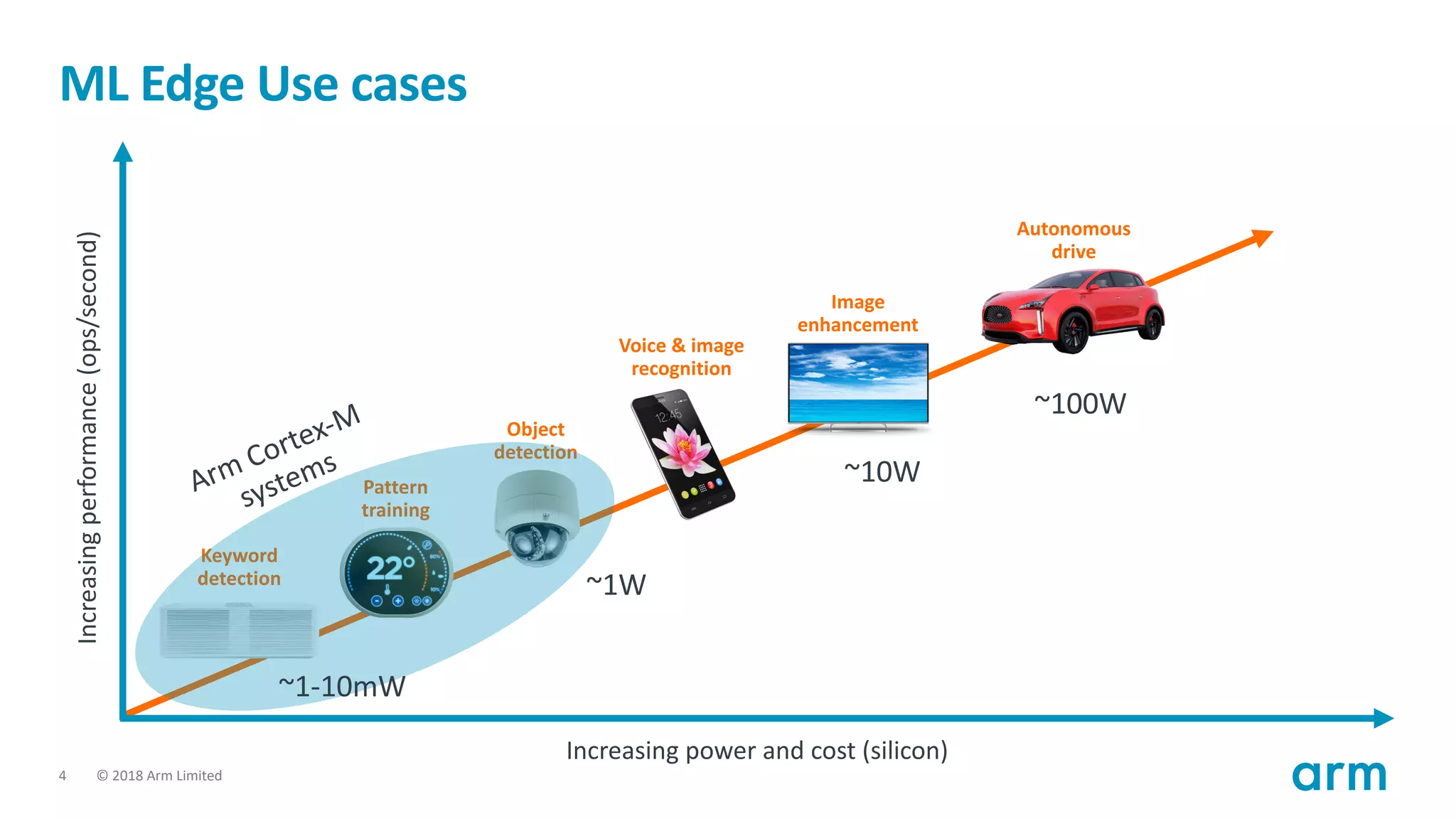

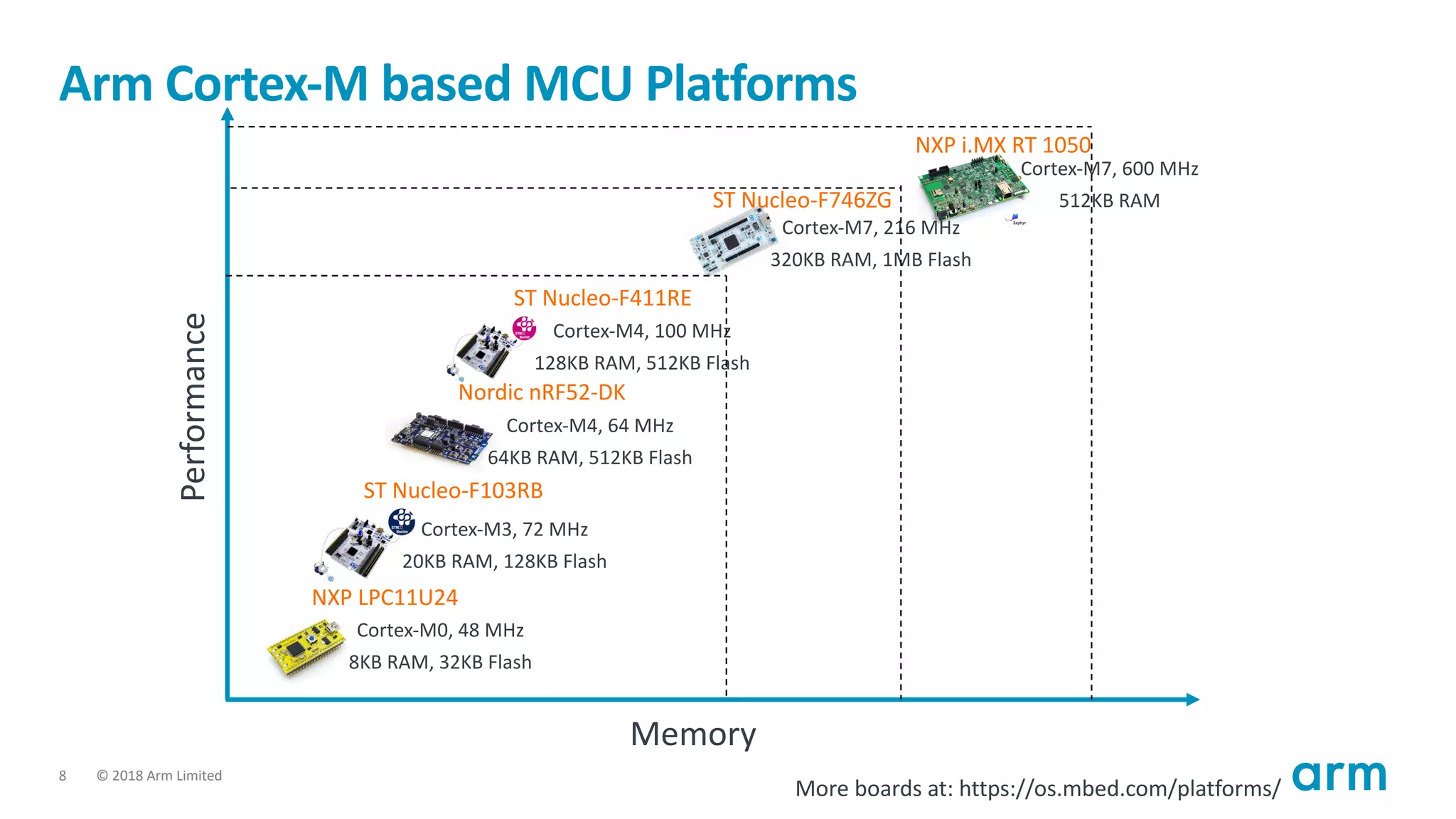

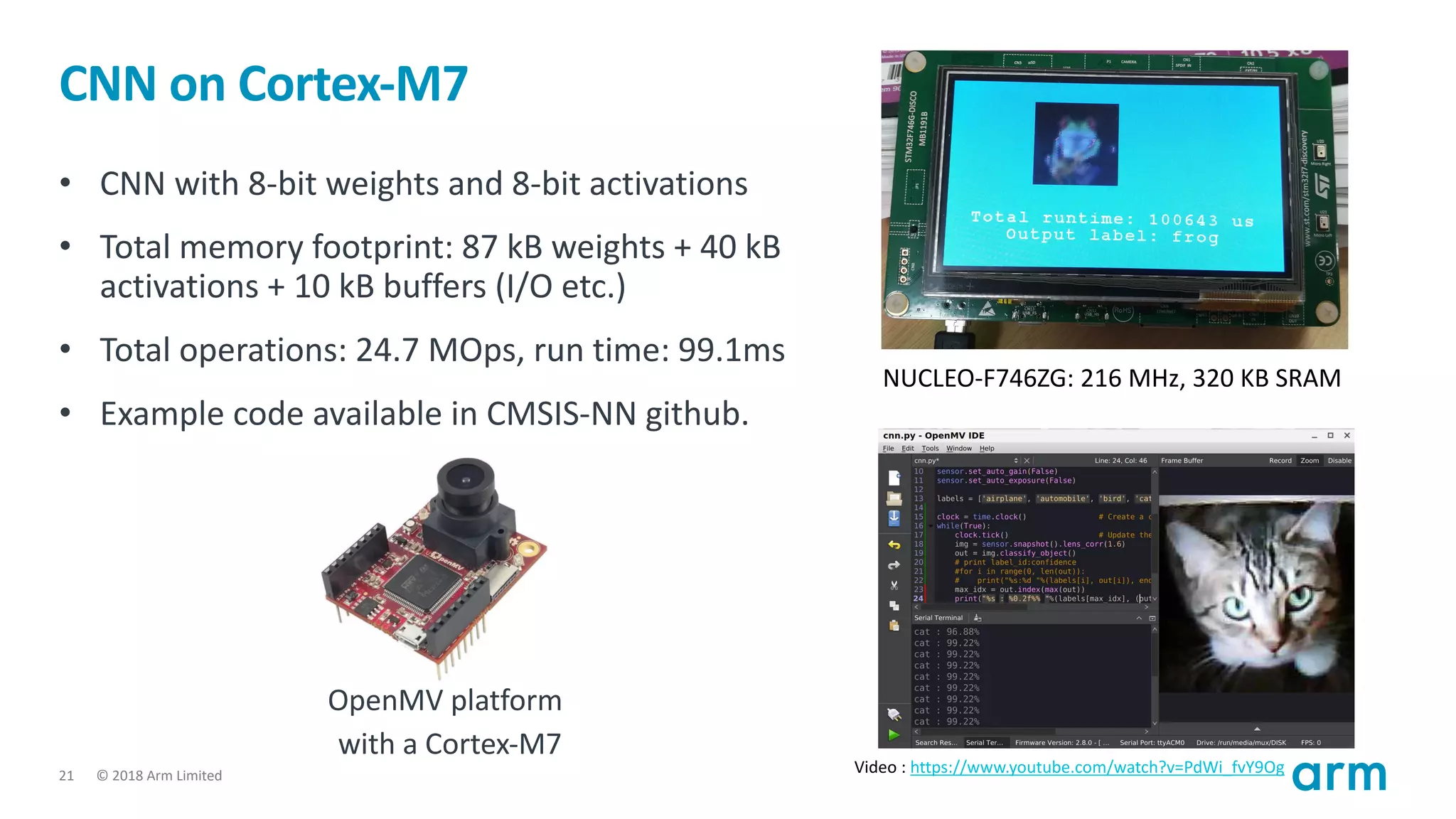

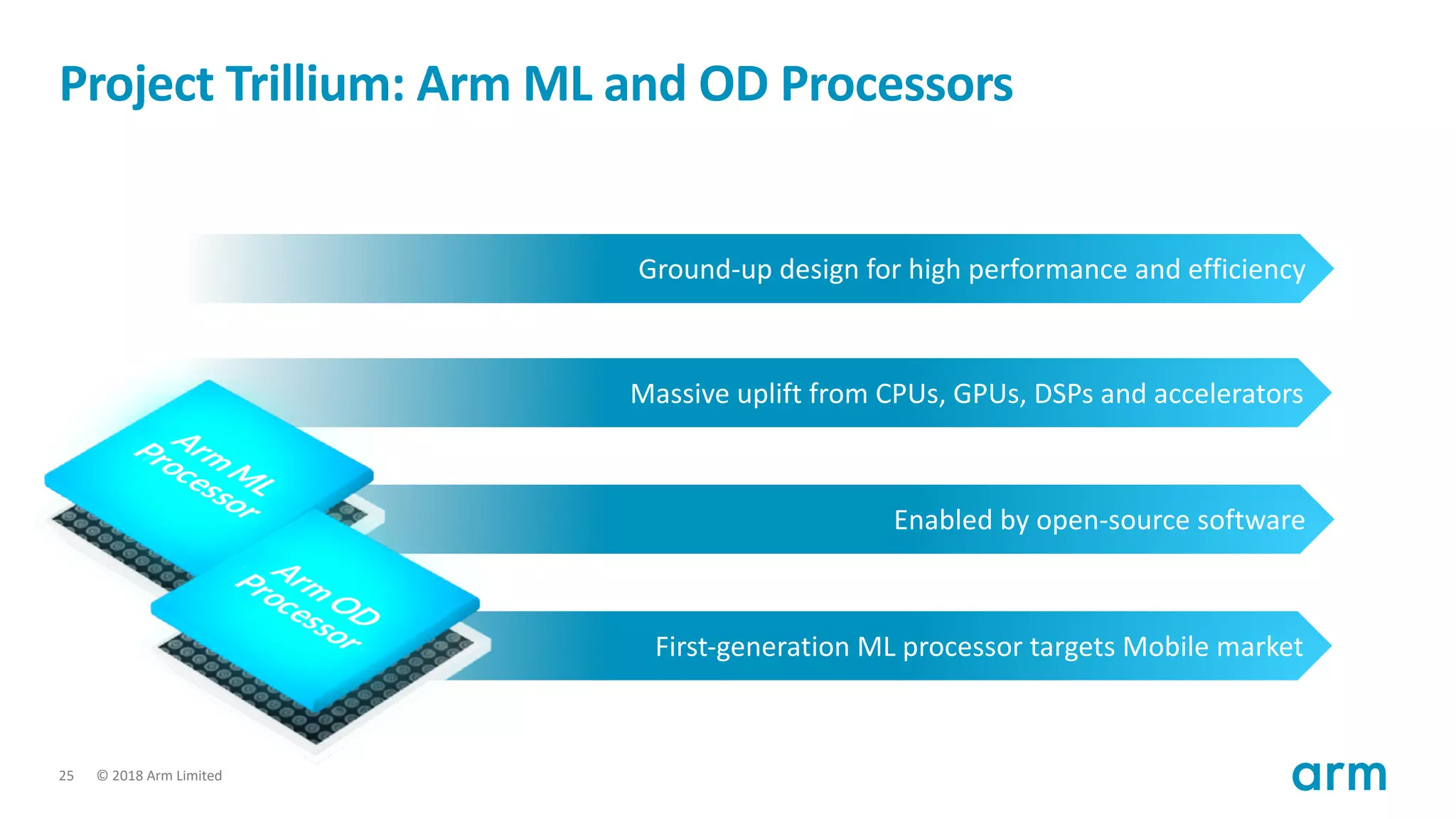

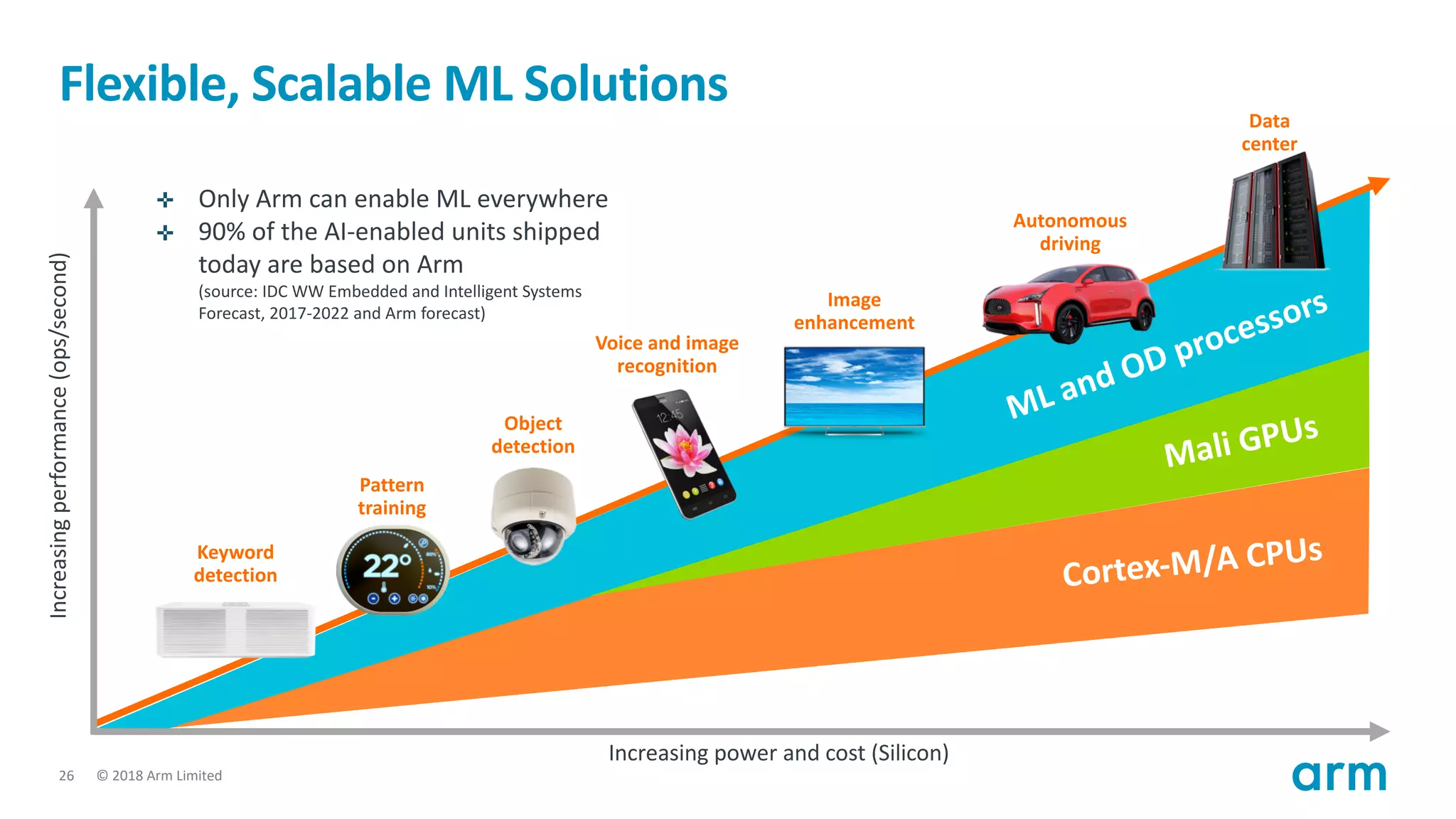

The document discusses the transition of machine learning (ML) to edge computing, particularly on ARM Cortex-M microcontrollers, enabling embedded intelligence with a focus on applications such as keyword spotting. It emphasizes the importance of hardware-constrained neural network architectures and the use of optimized libraries like CMSIS-NN for efficient model deployment. Key takeaways include advancements in NN model performance, quantization strategies, and edge ML use cases, driven by growing demands for localized processing capabilities.