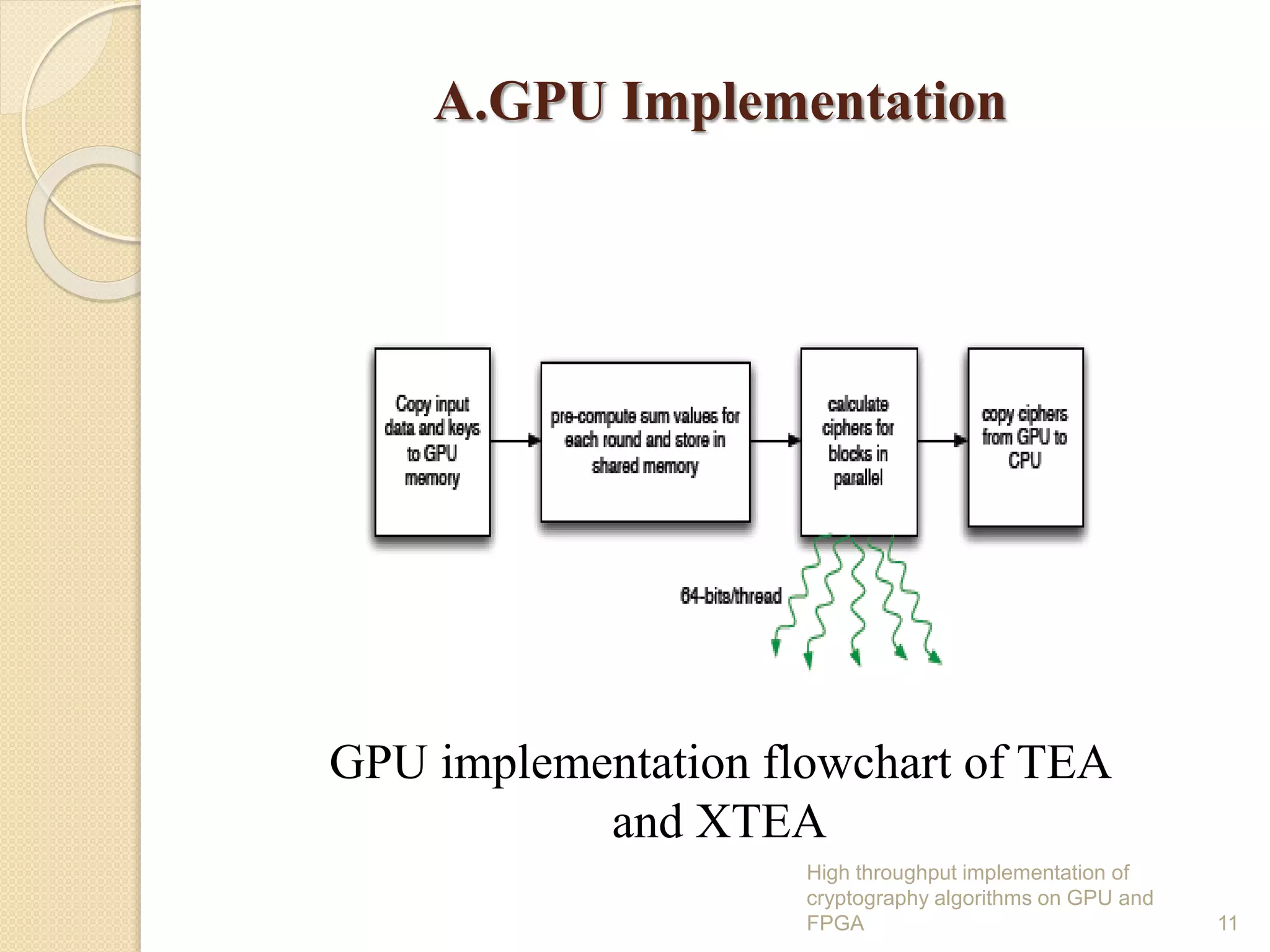

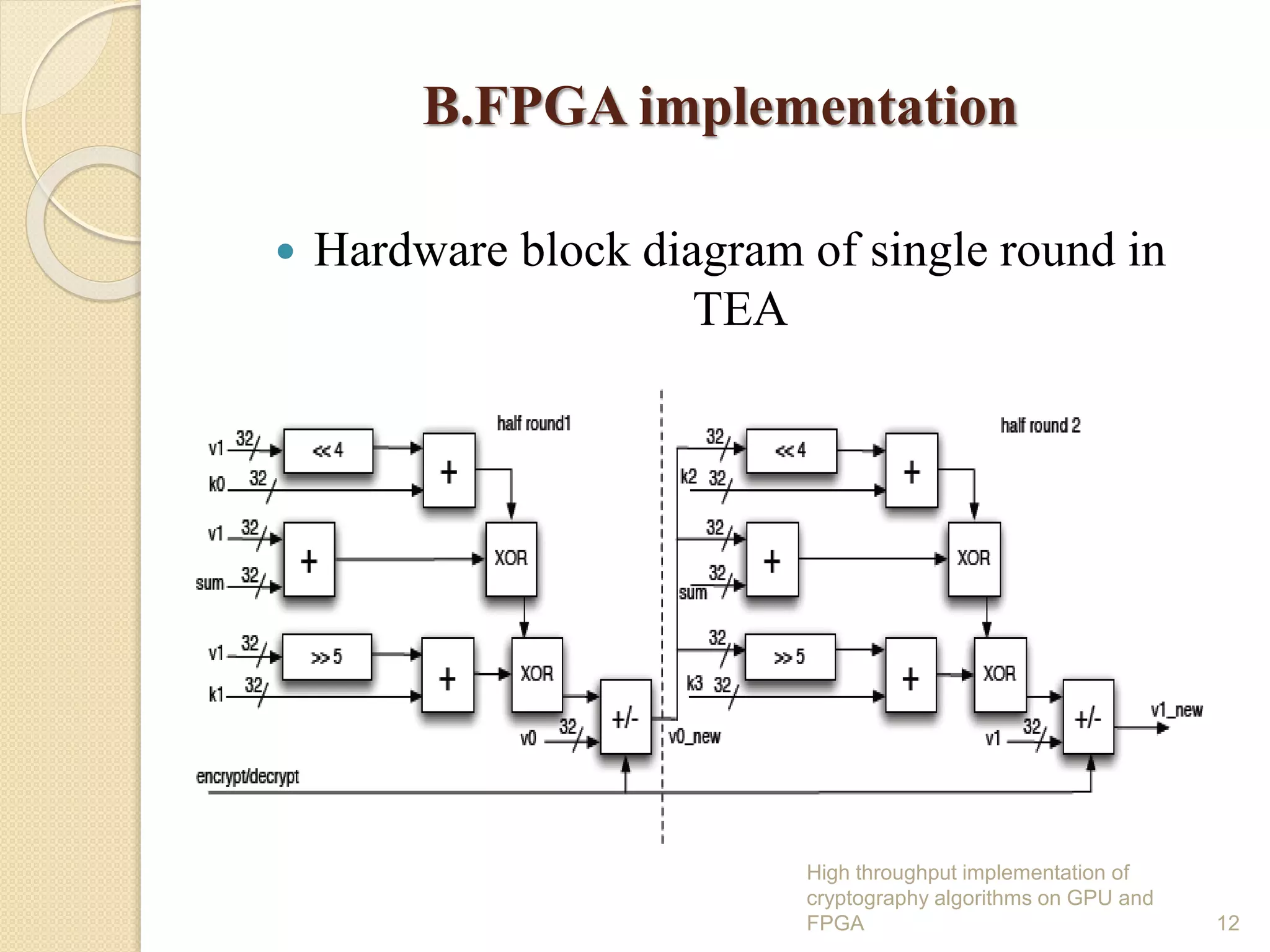

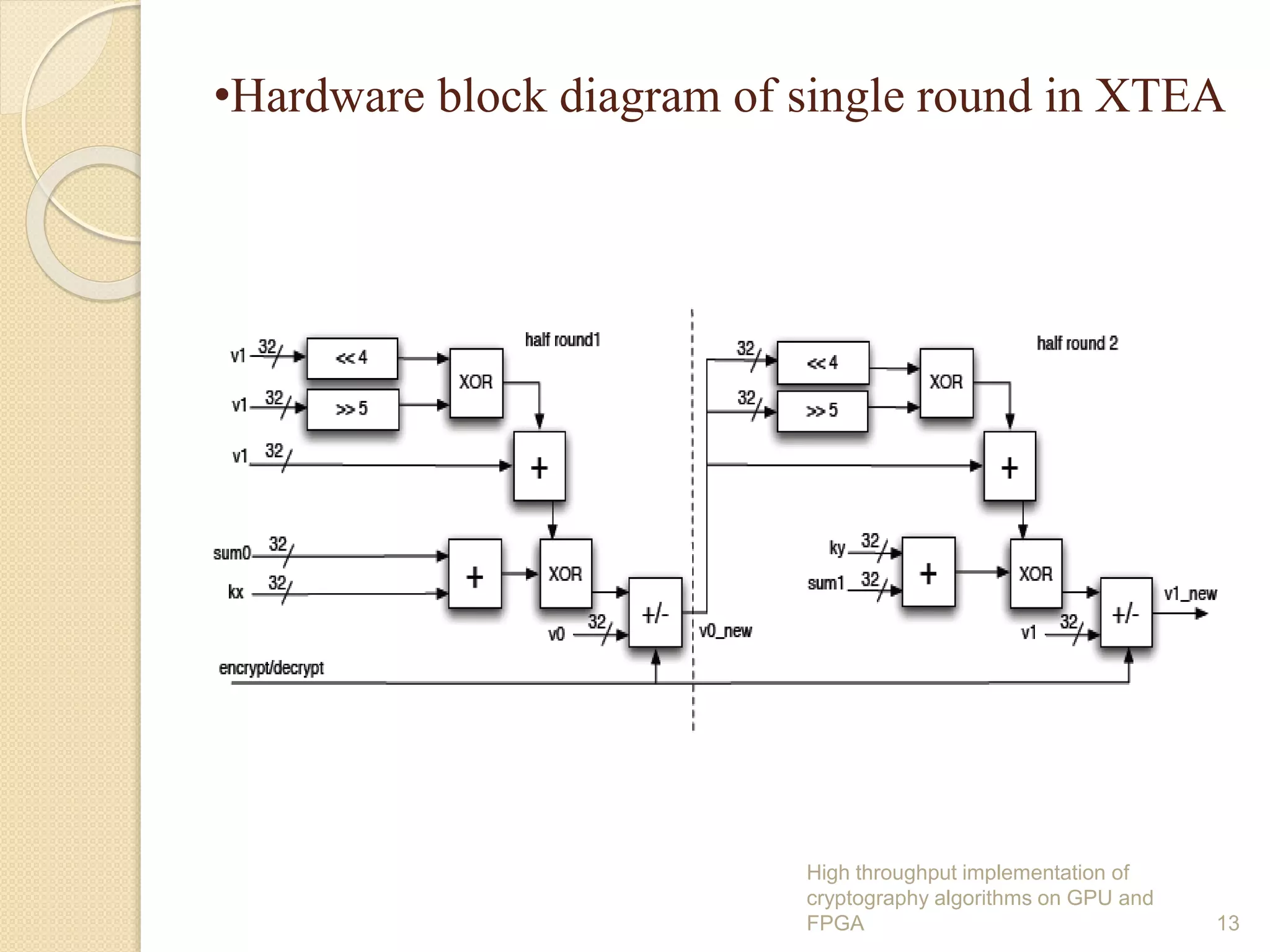

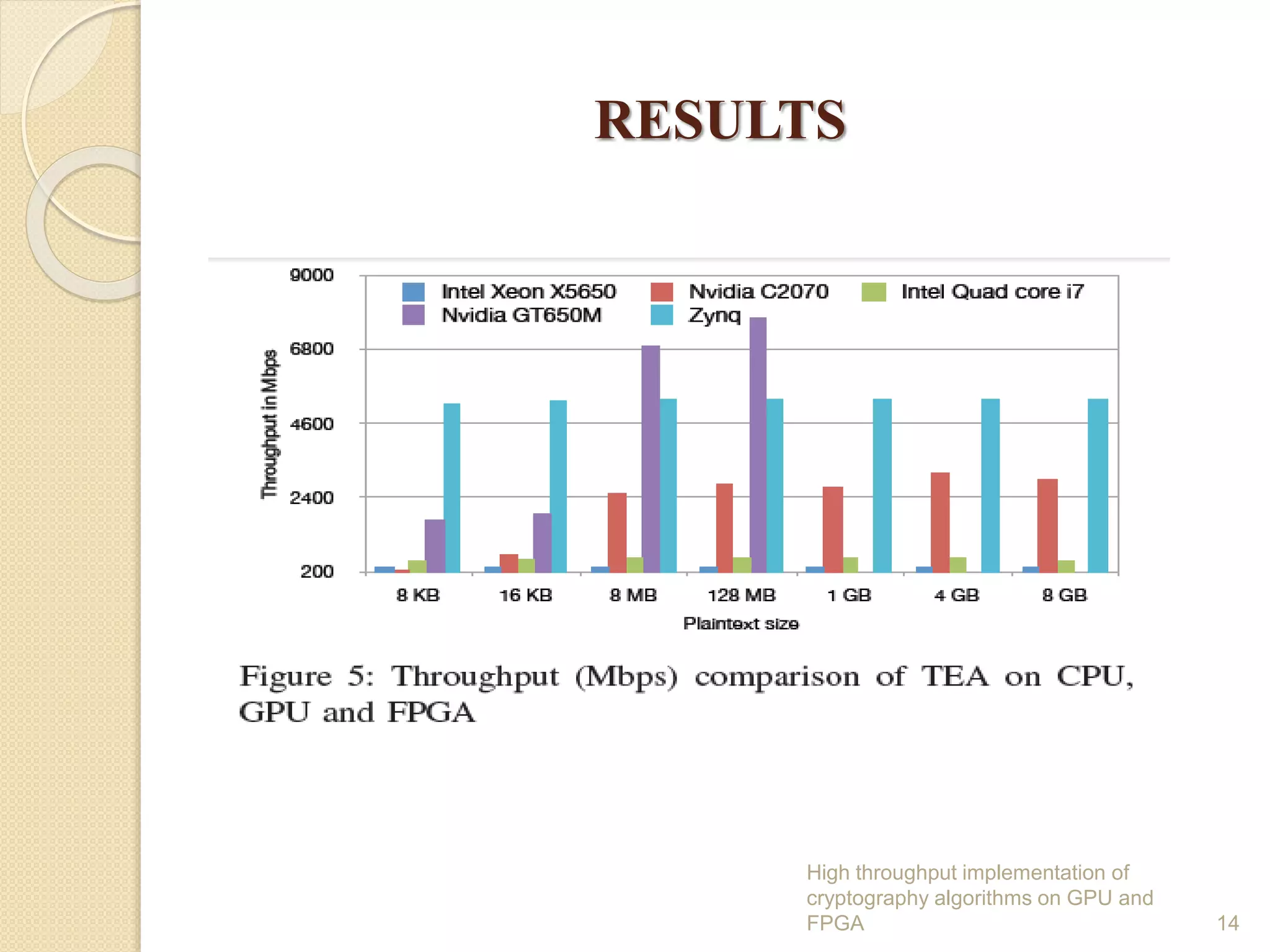

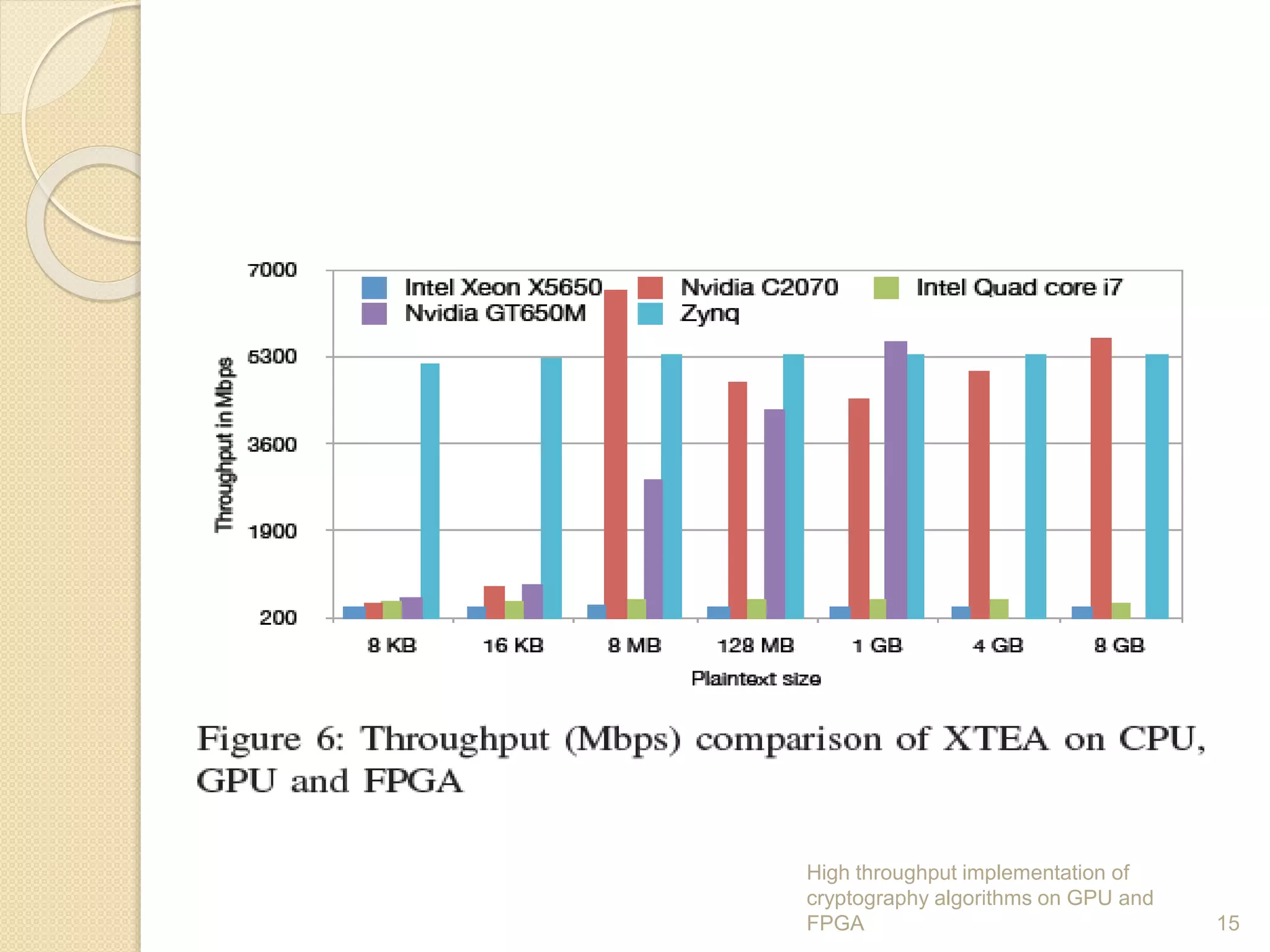

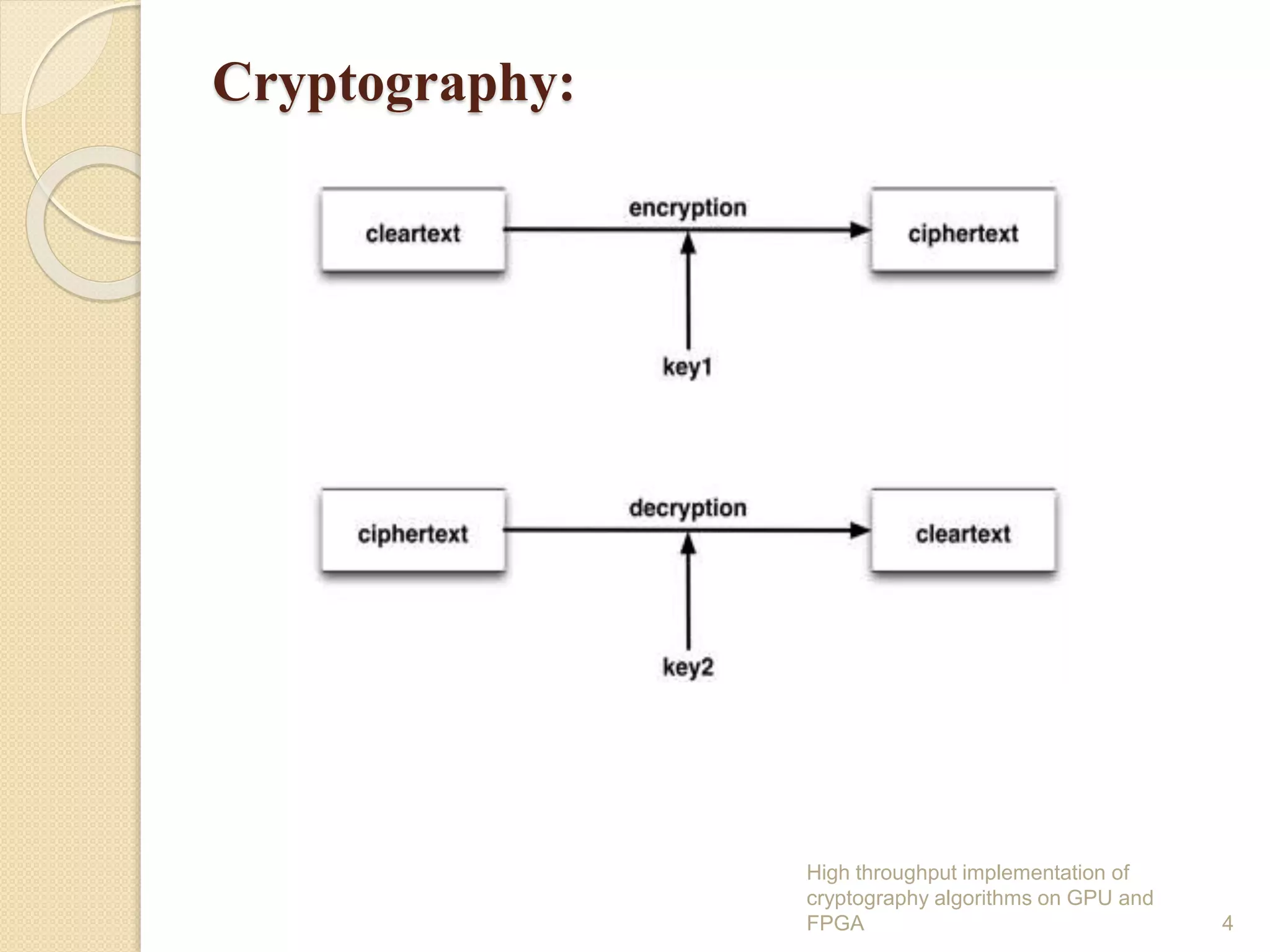

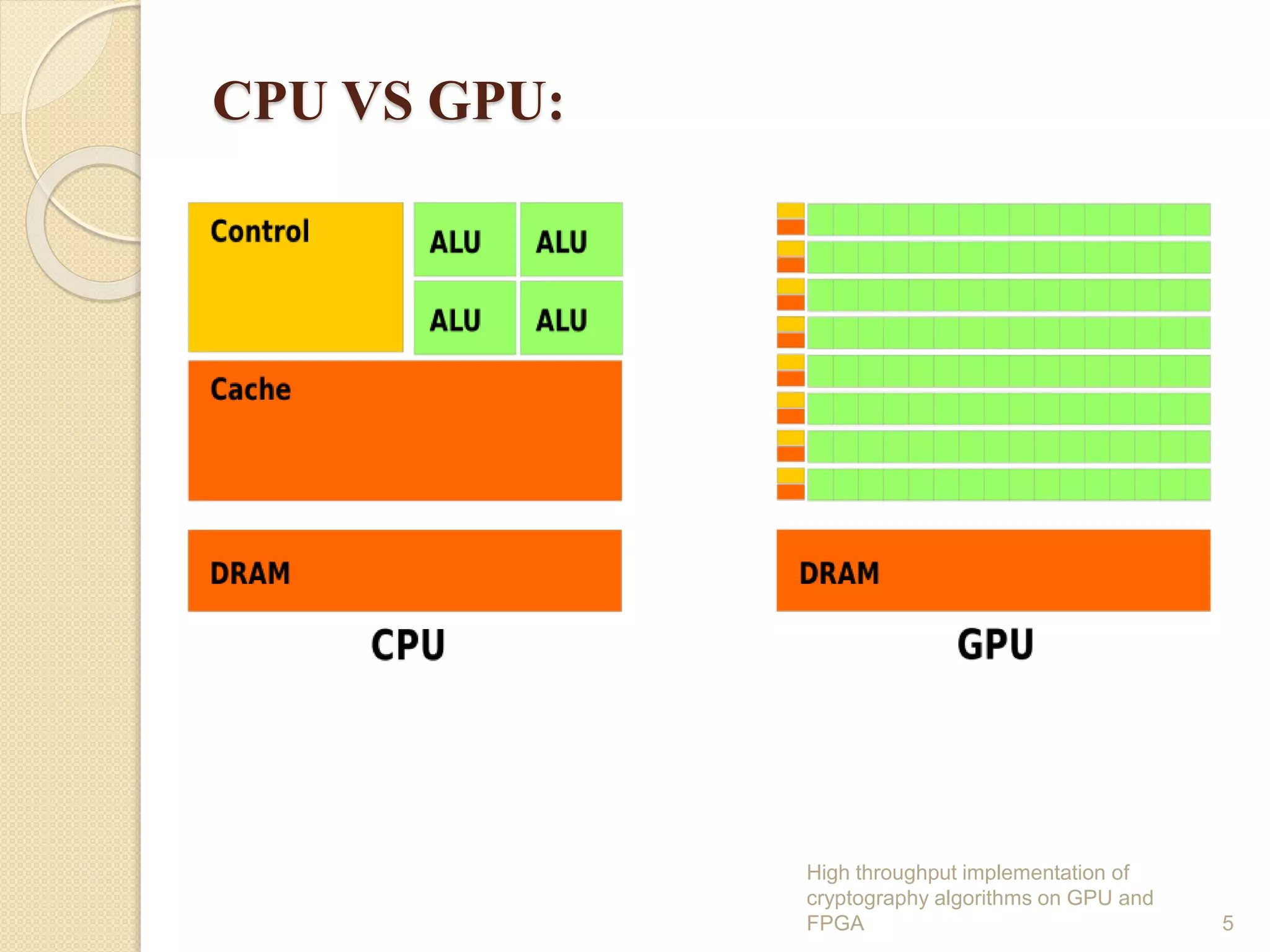

This document summarizes a seminar presentation on implementing cryptography algorithms with high throughput on GPUs and FPGAs. It introduces tiny encryption algorithm (TEA) and an extended version of TEA (XTEA) as lightweight cryptography algorithms suitable for hardware acceleration. It describes implementing TEA and XTEA on GPUs and FPGAs using cryptographic co-processors and hardware acceleration tools. Results show that FPGAs perform better for smaller plaintext sizes while GPUs achieve higher throughput for larger plaintext sizes.

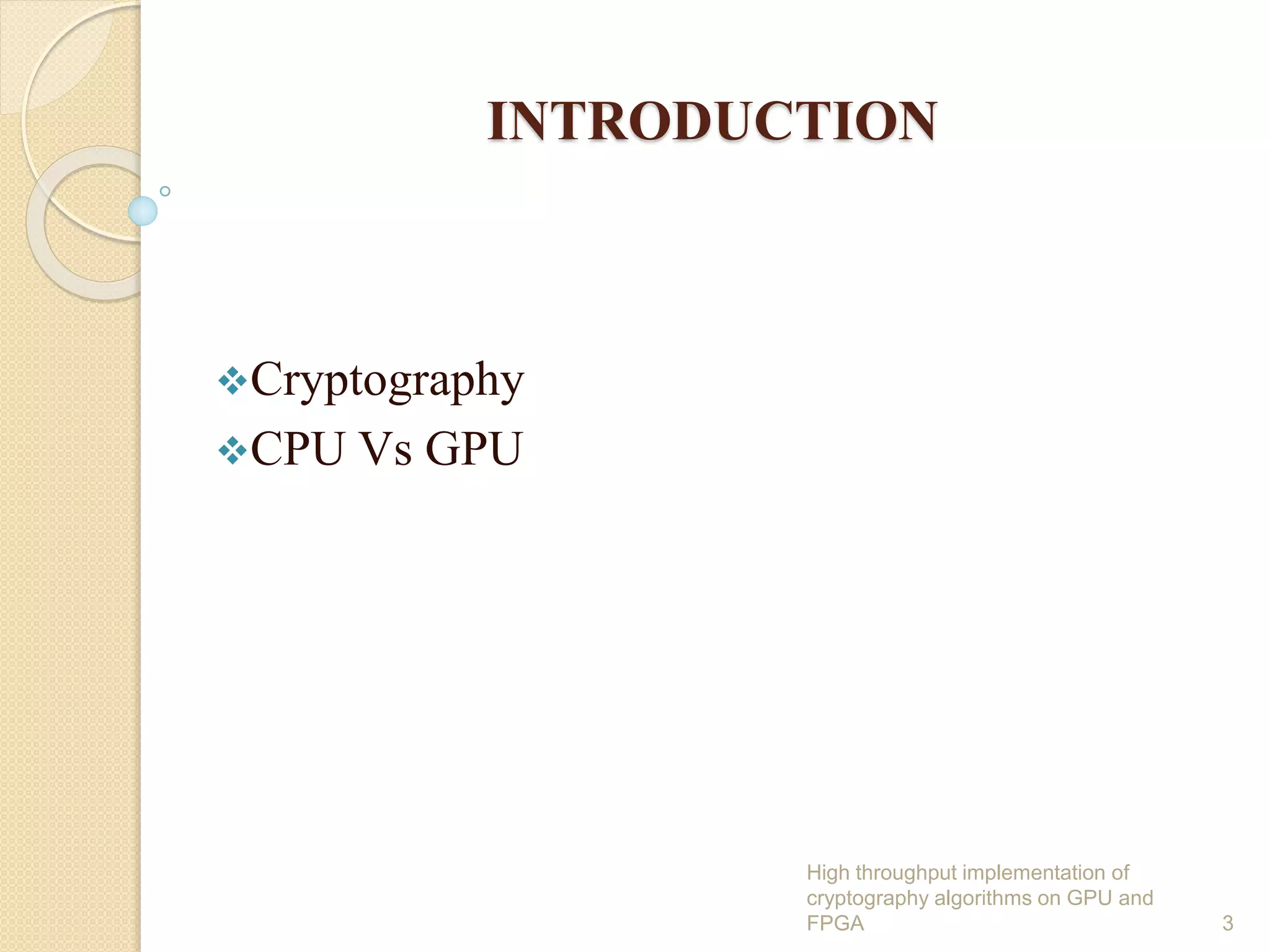

![Extended Version of TEA

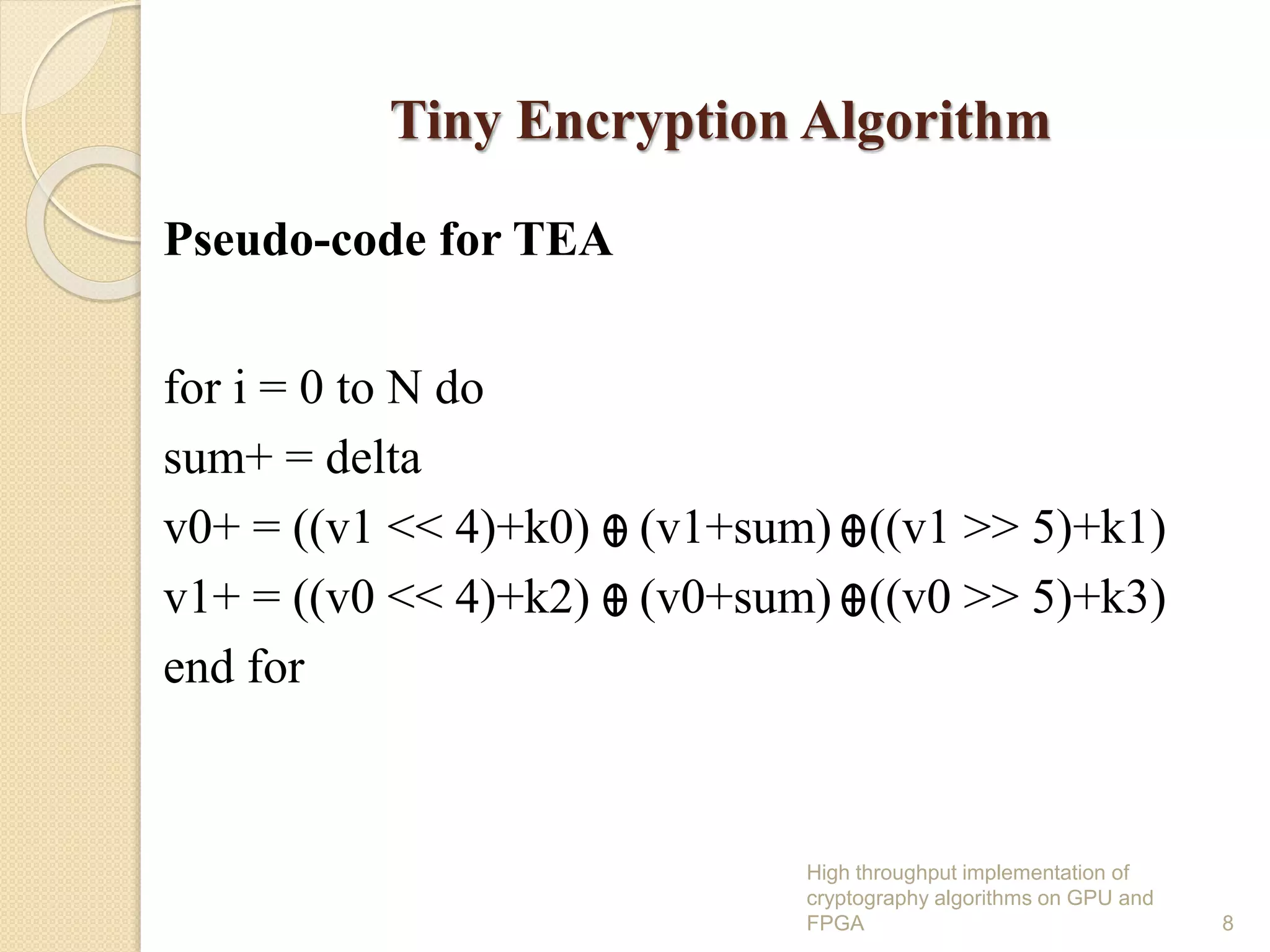

Pseudo-code for XTEA

for i = 0 to N do

v0+ = ((v1 << 4) (v1 >> 5) + v1) (sum +

key[sum&3])

sum+ = delta

v1+ = ((v0 << 4) (v0 >> 5) + v0) (sum +

key[sum&3])

end for

High throughput implementation of

cryptography algorithms on GPU and

FPGANMIET 9](https://image.slidesharecdn.com/highthroughputimplementations-150316030720-conversion-gate01/75/High-throughput-implementations-of-cryptography-algorithms-on-GPU-and-FPGA-9-2048.jpg)