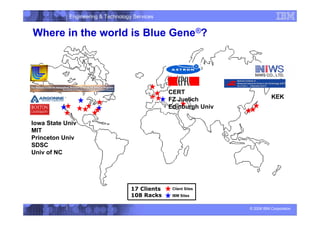

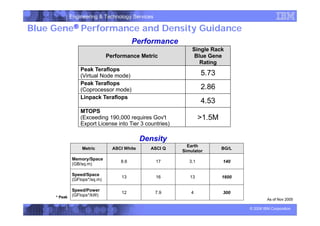

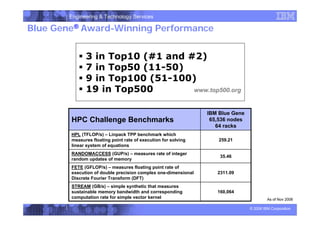

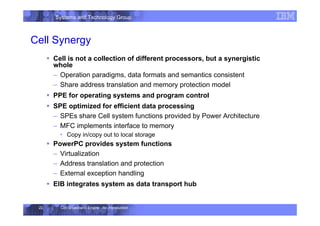

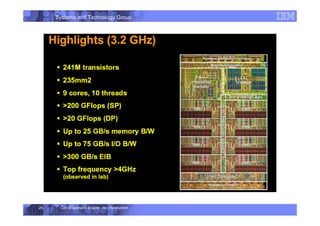

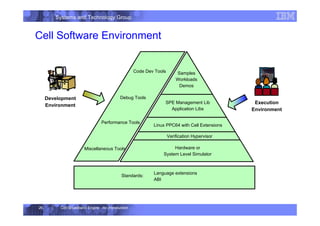

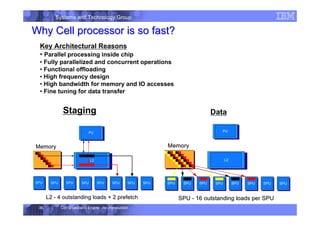

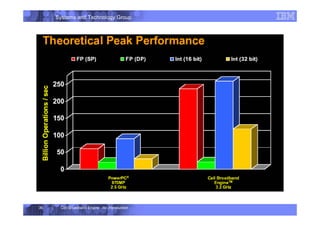

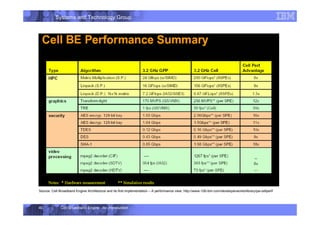

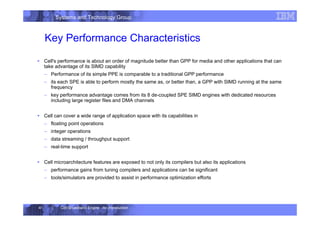

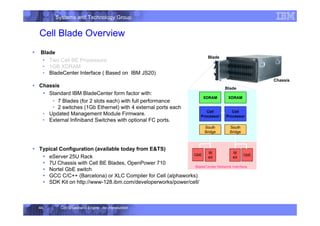

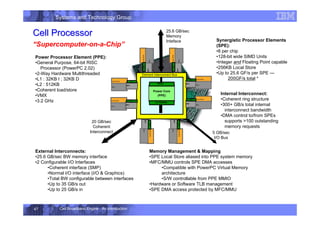

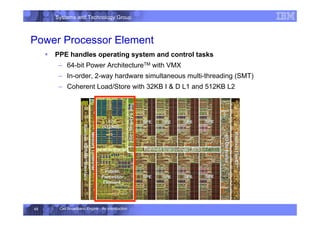

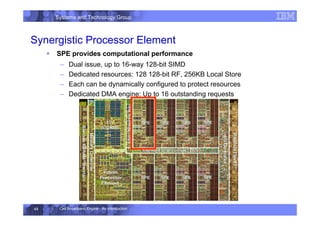

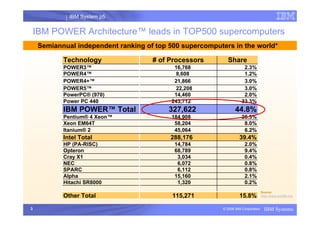

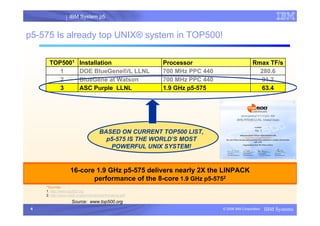

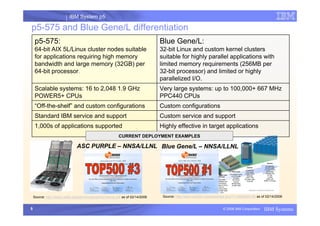

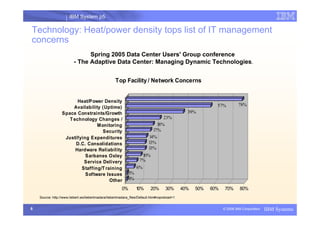

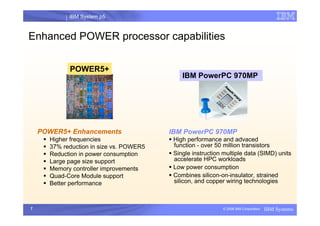

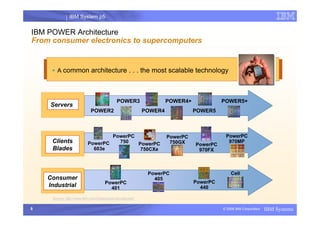

The document introduces the Cell Broadband Engine and its relevance in high-performance computing (HPC), detailing its architecture, performance characteristics, and hardware components. It highlights the advantages of the IBM Power architecture, including the P5-575 server’s superior performance and scalability for applications requiring high memory bandwidth. The document also discusses software development considerations and the synergy of the Cell's hardware and software ecosystem.

![IBM System p5

I

9 © 2006 IBM Corporation IBM Systems

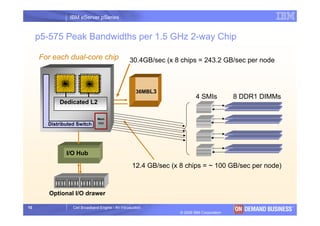

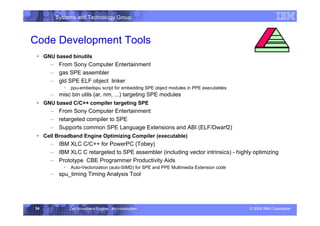

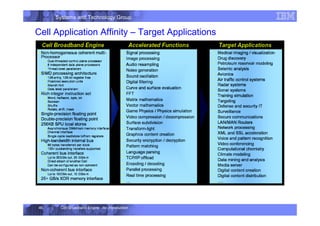

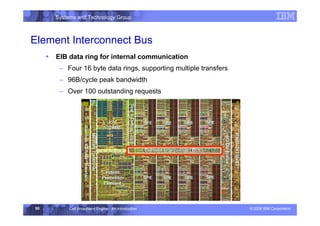

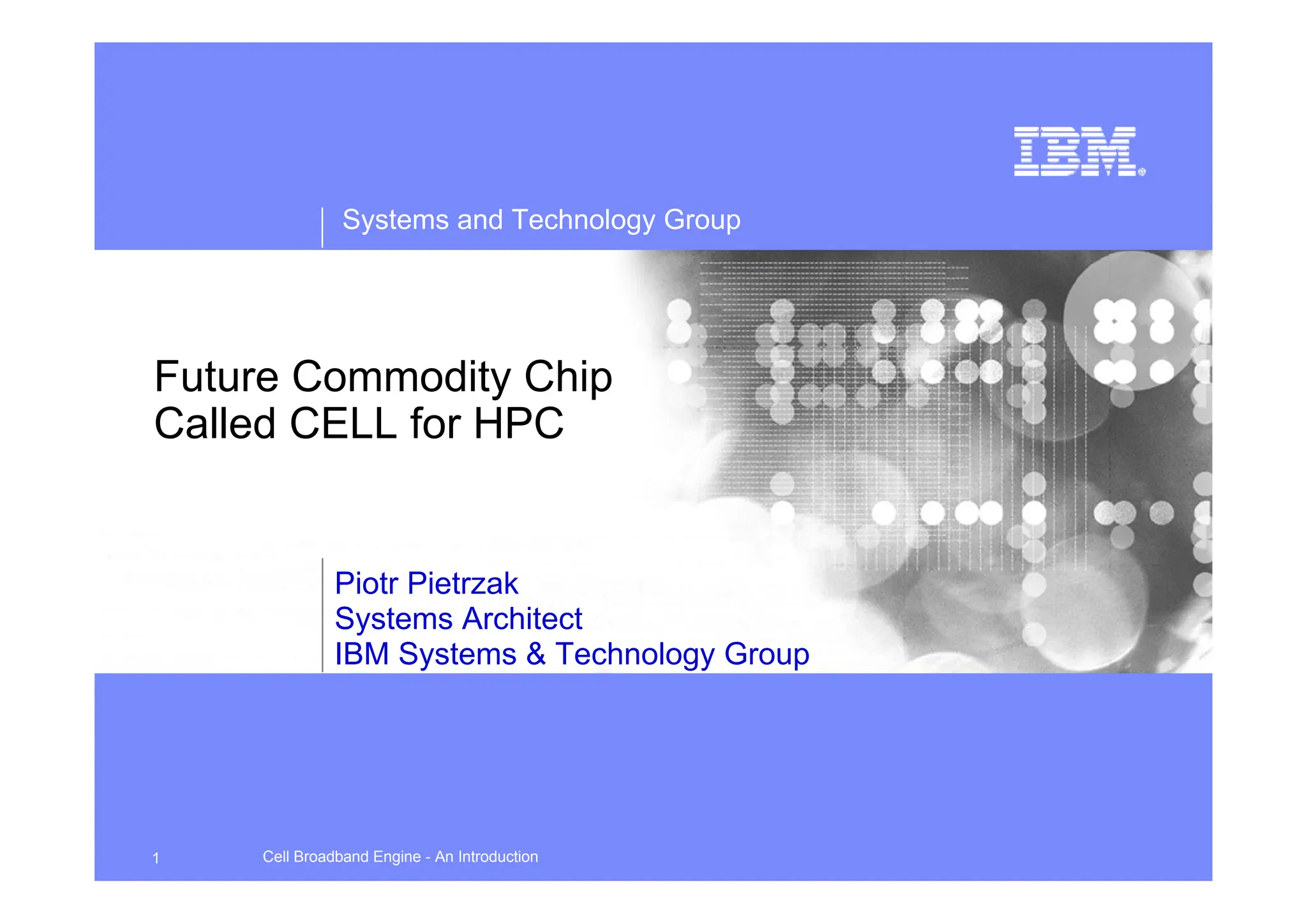

IBM System p5 575: THE CRUNCHER!

New 8-core

DATA CRUNCHER

p5-575 [8-core] 2.2 GHz

66.4 GFLOPS/node

LINPACK HPC

100.5 GB/sec

STREAM Traid (Tuned)

Sources: http://www.cs.virginia.edu/stream/ submitted February 14, 2006

http://www.netlib.org/benchmark/performance.pdf submitted February 14,2006

New 16-core

NUMBER CRUNCHER

p5-575 [16-core] 1.9 GHz

111.4 GFLOPS/node

LINPACK HPC

86.3 GB/sec

STREAM Triad (Tuned)

NEW!

1: Node hardware only, 1GB memory 2: Node hardware only, 16GB memory

NEW!](https://image.slidesharecdn.com/panibmpower-240529160541-2a010405/85/Future-Commodity-Chip-Called-CELL-for-HPC-9-320.jpg)